Знакомство с программой Micro-cap. Изучение характеристик и логических элементов транзисторно-транзисторной логики (ТТЛ)

ЗНАКОМСТВО С ПРОГРАММОЙ MICRO-CAP. ИЗУЧЕНИЕ ХАРАКТЕРИСТИК ЛОГИЧЕСКИХ ЭЛЕМЕНТОВ ТТЛ

1. ЦЕЛЬ РАБОТЫ

Ознакомиться с программой схемотехнического моделирования и проектирования MC8DEMO из семейства Micro-Cap (Microcomputer Circuit Analysis Program) фирмы Spectrum Software. Изучить характеристики ключевых схем на биполярных транзисторах и базовых схем логических элементов ТТЛ, используя возможности программы MC8DEMO.

2. КРАТКИЕ СВЕДЕНИЯ О ПРОГРАММЕ MC8DEMO

Программа MC8DEMO является студенческой или демонстрационной версией, которая предназначена для моделирования простых электронных схем, содержащих не более 50 компонентов или 100 связей, что вполне достаточно для изучения базовых схем цифровой техники и их характеристик. Эта программа свободно доступна на сайте http://www.spectrum-soft.com.

Программа позволяет создавать проектируемые аналоговые, цифровые и смешанные аналого-цифровые электрические схемы, выполнять их ввод для моделирования и получения характеристик, изменять параметры схем для получения требуемых характеристик.

Программа позволяет выполнять анализ нелинейных электронных схем по постоянному току, выполнять расчет переходных процессов, рассчитывать частотные характеристики. Есть средства синтеза пассивных и активных аналоговых фильтров. Программа может строить графики результатов моделирования.

Спроектированные и отработанные схемы, а также графики, отображающие их характеристики, могут выводиться в графическом виде для документирования.

Для освоения студенческой или профессиональной версии программы Micro-Cap следует обратиться к источнику [ 1 ].

3. КРАТКИЕ СВЕДЕНИЯ О РАБОТЕ КЛЮЧЕЙ

3.1. СТАТИЧЕСКИЕ РЕЖИМЫ КЛЮЧЕЙ НА БИПОЛЯРНЫХ ТРАНЗИСТОРАХ

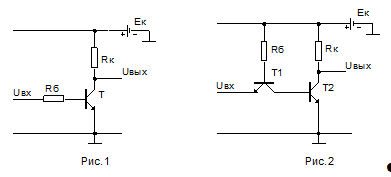

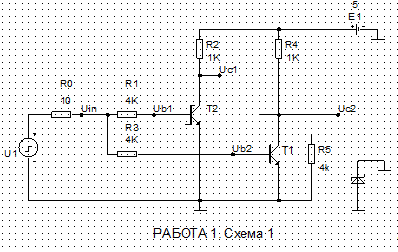

Роль коммутирующего ключевого элемента в ключах рис.1,2 играет выходной транзистор, который в статических состояниях находится либо в режиме отсечки (пропускает минимальный остаточный ток, близкий к нулевому), либо в режиме насыщения (на нем падает минимальное остаточное напряжение, близкое к нулевому), и только при смене состояний он в течение некоторого времени находится в активной области.

Остаточный ток и остаточное напряжение являются главными статическими параметрами ключа.

В запертом состоянии

ключа рис.1, строго говоря, должно

выполняться условие Uвх

< 0. В этом случае эмиттерный и коллекторный

p-n

переходы транзистора смещены в обратном

направлении. Однако кремниевый p-n

переход остается запертым и при

положительном напряжении, если Uвх

< U0

(U0 0,7В

– напряжение на открытом p-n

переходе, которое считают напряжением

отпирания p-n

перехода). При этом токи всех трех выводов

транзистора обычно не превышают долей

микроампера. Простейшей моделью (схемой

замещения) запертого кремниевого

транзистора является разрыв всех его

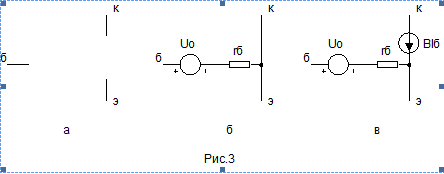

выводов (рис.3,а).

0,7В

– напряжение на открытом p-n

переходе, которое считают напряжением

отпирания p-n

перехода). При этом токи всех трех выводов

транзистора обычно не превышают долей

микроампера. Простейшей моделью (схемой

замещения) запертого кремниевого

транзистора является разрыв всех его

выводов (рис.3,а).

В данной лабораторной работе исследуются ключи на кремниевых транзисторах, поэтому токи запертого транзистора в последующем изложении считаются нулевыми.

В режиме насыщения

транзистора оба p-n

перехода смещены в прямом направлении.

В таком случае напряжение Uбэ U0,

а остаточное напряжение между коллектором

и эмиттером Uкн

= Uр

+ Iкн

rк

, где Uр

– разность напряжений на эмиттерном и

коллекторном переходах; Iкн

- ток коллектора; rк

- сопротивление коллекторного слоя.

Обычно полное остаточное напряжение

Uкн

составляет 50-100 мВ, что много меньше

напряжения Eк,

поэтому в последующем изложении

остаточное напряжение Uкн

считается нулевым. В таком случае

простейшей моделью (схемой замещения)

насыщенного кремниевого транзистора

является схема рис.3,б. Резистор rб

учитывает сопротивление открытого

эмиттерного p-n

перехода.

U0,

а остаточное напряжение между коллектором

и эмиттером Uкн

= Uр

+ Iкн

rк

, где Uр

– разность напряжений на эмиттерном и

коллекторном переходах; Iкн

- ток коллектора; rк

- сопротивление коллекторного слоя.

Обычно полное остаточное напряжение

Uкн

составляет 50-100 мВ, что много меньше

напряжения Eк,

поэтому в последующем изложении

остаточное напряжение Uкн

считается нулевым. В таком случае

простейшей моделью (схемой замещения)

насыщенного кремниевого транзистора

является схема рис.3,б. Резистор rб

учитывает сопротивление открытого

эмиттерного p-n

перехода.

В состоянии нормального активного усиления эмиттерный p-n переход открыт, а коллектрный – смещен в обратном направлении (в состоянии инверсного усиления – наоборот). Простейшая модель транзистора в режиме усиления представлена на рис.3.в. Усилительные свойства транзистора учитываются включением между коллектором и эмиттером зависимого генератора тока BIб . Напряжение на открытом эмиттерном переходе учитывается включением между базой и эмиттером транзистора генератора эдс U0.

Для определения статических токов и напряжений в ключах рис.1,2 можно использовать простейшие модели транзисторов, приведенные на рис.3, в соответствии с рабочими режимами транзисторов.

Для схемы рис.1 при использовании соответствующей схемы замещения имеем:

( 1 )

( 1 )

Минимальный базовый ток, который требуется для насыщения (граничный режим между насыщенным и активным), находится по известному значению коллекторного тока Iкн:

( 2 )

( 2 )

Глубина насыщения транзистора (коэффициент насыщения s) характеризуется отношением реального тока Iб к минимальному току базы, который требуется для насыщения:

( 3 )

( 3 )

Из (1) и (2) можно определить минимальное напряжение Uвх , которое требуется для насыщения, положив Iб = Iбн :

( 4 )

( 4 )

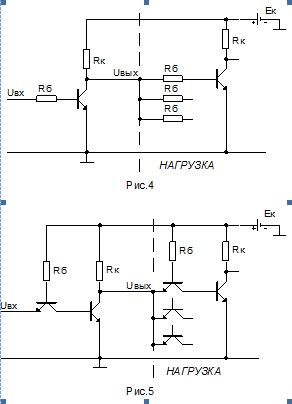

При подключении нагрузки к выходу ключа статические уровни выходного напряжения изменяются. В цифровых схемах ключ, как правило, нагружает входная цепь другого ключа такого же типа (или несколько одинаковых ключей), как показано на рис. 4. Такая нагрузка практически не влияет на режим насыщенного транзистора, так как входы внешних ключей при этом имеют потенциал, практически равный нулевому, транзисторы внешних ключей закрыты, входной ток в них отсутствует, составляющая тока нагрузки в анализируемом ключе тоже отсутствует.

Нагрузка, подключаемая по схеме рис.4, влияет на режим закрытого транзистора. В этом случае на выходе анализируемого ключа высокий уровень напряжения – внешние ключи открыты. Внешнюю цепь нагрузки можно заменить эквивалентным резистором нагрузки Rн, включенным между коллектором и эмиттером закрытого транзистора. Ток нагрузки (вытекающий из ключа), который протекает через резистор Rк, понижает уровень выходного напряжения в анализируемом ключе. Он теперь равен

( 5 )

( 5 )

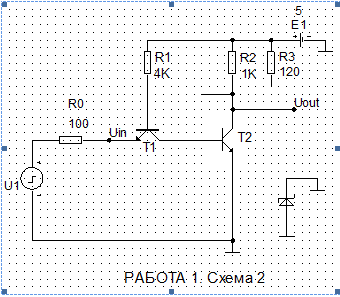

Для интегральных логических элементов, в которых используются биполярные насыщенные транзисторы, характерна схема ключа (инвертора) с управляющим (коммутирующим) входным транзистором (рис.2). В элементах ТТЛ для расширения логических возможностей входной транзистор Т1 делается многоэмиттерным (в таком случае схема реализует логическую операцию И-НЕ).

Управляющее напряжение

в

ключе рис.2 однополярное (положительное).

При условии, что напряжение

в

ключе рис.2 однополярное (положительное).

При условии, что напряжение

есть

выходное напряжение другого ключа

такого же типа, оно может изменяться от

есть

выходное напряжение другого ключа

такого же типа, оно может изменяться от

до

до

В ключе рис.2 в отличие от ключа рис.1

токи выходного транзистора Т2 в статических

состояниях от напряжения

В ключе рис.2 в отличие от ключа рис.1

токи выходного транзистора Т2 в статических

состояниях от напряжения

практически

не зависят.

практически

не зависят.

При

транзистор Т1 находится в насыщенном

состоянии, т.к. оба его перехода смещены

в прямом направлении (потенциал базы

транзистора Т1 выше потенциала его

эмиттера и коллектора, т.к.

транзистор Т1 находится в насыщенном

состоянии, т.к. оба его перехода смещены

в прямом направлении (потенциал базы

транзистора Т1 выше потенциала его

эмиттера и коллектора, т.к.

,

а

,

а

).

Для насыщенного транзистора Т1 имеем

).

Для насыщенного транзистора Т1 имеем

,

тогда

,

тогда

<

< ,

поэтому транзистор Т2 закрыт и

,

поэтому транзистор Т2 закрыт и

Ток

базы транзистора Т2 при этом отсутствует.

Вытекающий ток

Ток

базы транзистора Т2 при этом отсутствует.

Вытекающий ток

замыкается

через источник управляющего напряжения

замыкается

через источник управляющего напряжения

и

задается резистором

и

задается резистором

:

:

( 6 )

( 6 )

Если

,

транзистор Т1 находится в статическом

состоянии инверсного усиления, т.к. его

эмиттерный переход смещен в обратном

направлении (потенциал эмиттера Т1 выше

потенциала базы, т.к.

,

транзистор Т1 находится в статическом

состоянии инверсного усиления, т.к. его

эмиттерный переход смещен в обратном

направлении (потенциал эмиттера Т1 выше

потенциала базы, т.к.

,

а

,

а

),

а его коллекторный переход – в прямом

(

),

а его коллекторный переход – в прямом

( >

> ).

В режиме инверсного усиления “нормальный”

коллектор Т1 фактически является

эмиттером, “нормальный” эмиттер –

коллектором, поэтому в данном случае

).

В режиме инверсного усиления “нормальный”

коллектор Т1 фактически является

эмиттером, “нормальный” эмиттер –

коллектором, поэтому в данном случае

(ток

(ток

-

вытекающий,

а токи

-

вытекающий,

а токи

и

и

-

втекающие).

Из-за существенной асимметрии структуры

транзистора коэффициент передачи тока

базы

-

втекающие).

Из-за существенной асимметрии структуры

транзистора коэффициент передачи тока

базы

в

режиме инверсного усиления мал (

в

режиме инверсного усиления мал ( <<1),

поэтому втекающий ток

<<1),

поэтому втекающий ток

тоже

мал (

тоже

мал ( ),

а вытекающий ток

),

а вытекающий ток

практически

равен току

практически

равен току

:

:

. ( 7 )

. ( 7 )

Для насыщения

транзистора Т2 требуется, чтобы

(s

> 1).

(s

> 1).

Влияние нагрузки на работу ключа рис.2 рассмотрим при условии, что нагружают анализируемый ключ один или несколько ключей такого же типа, рис.5. Анализ показывает, что на режим работы ключа, когда транзистор Т2 закрыт, нагрузка практически не влияет, т.к. все входные транзисторы внешних ключей нагрузки имеют на эмиттерах высокий потенциал и работают в режиме инверсного усиления с весьма малыми входными токами, которые практически не нагружают анализируемый ключ.

В состоянии, когда

транзистор Т2 насыщен, входные транзисторы

внешних ключей также насыщены, вытекающие

эмиттерные токи внешних ключей в сумме

образуют дополнительную составляющую

коллекторного тока транзистора Т2,

обусловленную нагрузкой. Внешнюю цепь

нагрузки можно заменить эквивалентным

резистором нагрузки

,

включенным

параллельно резистору

,

включенным

параллельно резистору

.

Коэффициент

насыщения нагруженного ключа меньше,

чем у не нагруженного (sн

< s).

Если сопротивление

.

Коэффициент

насыщения нагруженного ключа меньше,

чем у не нагруженного (sн

< s).

Если сопротивление

слишком

мало, открытый транзистор Т2 работает

в активном режиме при соответствующем

увеличении уровня выходного напряжения.

слишком

мало, открытый транзистор Т2 работает

в активном режиме при соответствующем

увеличении уровня выходного напряжения.

3.2 ПЕРЕКЛЮЧЕНИЕ КЛЮЧЕЙ НА БИПОЛЯРНЫХ ТРАНЗИСТОРАХ

Быстродействие ключевого элемента определяется максимально допустимой частотой входных переключающих сигналов. Быстродействие зависит от общей длительности переходного процесса, обусловленной двумя факторами: собственной инерционностью ключевого транзистора (конечной скоростью изменения заряда в базе) и влиянием паразитных параметров (конечной скоростью изменения напряжения на барьерных и паразитных емкостях).

Переходный процесс переключения транзистора из запертого состояния в насыщенное содержит три стадии: задержки отпирания эмиттерного перехода, формирования фронта включения, накопление заряда в базе.

Задержка отпирания транзистора равна времени заряда барьерных емкостей до напряжения отпирания транзистора U0. Практически задержка проявляется в сдвиге фронта включения относительно фронта входного отпирающего сигнала (импульса). В большинстве практических случаев задержка отпирания невелика и существенно меньше длительности фронта включения.

Формирование фронта

включения

начинается с появления ступеньки

базового тока

вследствие отпирания эмиттерного

перехода. В насыщенных ключах ступенька

тока

вследствие отпирания эмиттерного

перехода. В насыщенных ключах ступенька

тока

достаточна для последующего насыщения

транзистора:

достаточна для последующего насыщения

транзистора:

>

> .

.

Если пренебречь влиянием емкостей на переходный процесс, поведение ключа на стадии формирования фронта включения непосредственно обусловлено процессом изменения заряда неосновных носителей в базе транзистора, который описывается уравнением:

( 8 )

( 8 )

где

-

время переноса заряда через базу в

нормальном режиме (время жизни неосновных

носителей в базе), которое проявляется

как постоянная времени переходной

характеристики транзистора.

-

время переноса заряда через базу в

нормальном режиме (время жизни неосновных

носителей в базе), которое проявляется

как постоянная времени переходной

характеристики транзистора.

Формирование фронта

включения происходит при существовании

активного режима работы пока выполняется

условие

<

< .

Окончание

фронта включения соответствует моменту,

когда заряд

.

Окончание

фронта включения соответствует моменту,

когда заряд

становится

равным

становится

равным

.

.

В общем случае, когда

нужно учитывать влияние емкости

коллекторного перехода

и

емкости нагрузки

и

емкости нагрузки

,

при анализе вместо

,

при анализе вместо

следует

пользоваться эквивалентной постоянной

времени

следует

пользоваться эквивалентной постоянной

времени

:

:

( 9 )

( 9 )

Длительность фронта включения рассчитывается по формуле

( 10 )

( 10 )

Для схемы рис.1 ток

рассчитывается

по (1), для

схемы рис.2

рассчитывается

по (1), для

схемы рис.2

=

= и рассчитывается

по (7).

и рассчитывается

по (7).

Если условие насыщения

не выполняется (

),

для определения времени включения

следует использовать формулу

),

для определения времени включения

следует использовать формулу

. ( 10а

)

. ( 10а

)

Накопление заряда

в базе происходит уже в насыщенном

транзисторе. Начиная с момента

,

все три

внешних тока транзистора не меняются.

Однако заряд в базе продолжает нарастать

по экспоненциальному закону, и этот

процесс заканчивается лишь через время

,

все три

внешних тока транзистора не меняются.

Однако заряд в базе продолжает нарастать

по экспоненциальному закону, и этот

процесс заканчивается лишь через время

,

которое

называют временем накопления. Значение

,

которое

называют временем накопления. Значение

может

существенно отличаться от величины

может

существенно отличаться от величины

(

( <

<

),

поскольку распределение носителей в

базе при насыщении отличается от

распределения при нормальном активном

режиме.

),

поскольку распределение носителей в

базе при насыщении отличается от

распределения при нормальном активном

режиме.

Процесс переключения транзистора из насыщенного состояния в запертое содержит две стадии: рассасывание избыточного заряда и формирование фронта выключения.

Рассасывание

избыточного заряда

проявляется внешне как задержка начала

фронта выключения относительно

выключающего (отрицательного) перепада

входного сигнала. На стадии рассасывания

транзистор остается насыщенным,

концентрация заряда в базе остается

выше равновесной концентрации, и оба

перехода транзистора смещены в прямом

направлении. При этом напряжение Uбэ

= U0

= 0,7 В.

Поэтому при установлении запирающего

входного напряжения Uвх

< U0

возникает

отрицательный входной ток

,

обусловленный

наличием в базе избыточного заряда. Ток

,

обусловленный

наличием в базе избыточного заряда. Ток

вытекает из базы, т.к. потенциал базы

выше потенциала входа. Величина этого

тока:

вытекает из базы, т.к. потенциал базы

выше потенциала входа. Величина этого

тока:

. (

11 )

. (

11 )

Отрицательный ток

означает “отсос” заряда из базы, поэтому

он начинает уменьшаться, и при

означает “отсос” заряда из базы, поэтому

он начинает уменьшаться, и при

=

= стадия

рассасывания заканчивается.

стадия

рассасывания заканчивается.

Анализ функции

изменения заряда

дает

формулу для определения времени

рассасывания:

дает

формулу для определения времени

рассасывания:

,

( 12 )

,

( 12 )

в которой для схемы

рис.1 ток

рассчитывается

по (1), а ток

рассчитывается

по (1), а ток

- по

(11).

Формула (12)

получена для случая, когда отпирающий

сигнал - длинный, а ток

- по

(11).

Формула (12)

получена для случая, когда отпирающий

сигнал - длинный, а ток

существенно меньше тока

существенно меньше тока

.

.

Для схемы рис.2

=

= и рассчитывается по (7). Ток

и рассчитывается по (7). Ток

=

= в

этой схеме замыкается далее через

насыщенный транзистор Т1 и источник

управляющего напряжения. Резисторов в

этой цепи нет. Ток

в

этой схеме замыкается далее через

насыщенный транзистор Т1 и источник

управляющего напряжения. Резисторов в

этой цепи нет. Ток

в этом случае определяется внутренним

сопротивлением насыщенных транзисторов

Т2 и Т1:

в этом случае определяется внутренним

сопротивлением насыщенных транзисторов

Т2 и Т1:

, ( 13 )

, ( 13 )

где Rг, rк1, rб2 - соответственно сопротивление источника Uвх, насыщенных транзисторов Т1 и Т2.

Если перед подачей запирающего сигнала транзистор в ключе не насыщен, то tр = 0.

Формирование фронта

выключения

начинается

в момент

времени, когда Q(t)=Qгр

. Если

емкостями Ск,

Сн можно

пренебречь, заряд в базе меняется по

тому же закону, что и на предыдущей

стадии рассасывания. Но величина заряда

не может достигать отрицательного

асимптотического значения

,

так как заряд неосновных носителей в

базе знак изменить не может. Поэтому

процесс формирования фронта выключения

заканчивается, когда Q(t)=0.

В таком случае при запирающих токах,

существенно меньших, чем ток насыщения,

можно получить:

,

так как заряд неосновных носителей в

базе знак изменить не может. Поэтому

процесс формирования фронта выключения

заканчивается, когда Q(t)=0.

В таком случае при запирающих токах,

существенно меньших, чем ток насыщения,

можно получить:

( 14 )

( 14 )

Ток

для ключей рис.1,2 рассчитывается

соответственно по формулам (11),(13).

для ключей рис.1,2 рассчитывается

соответственно по формулам (11),(13).

На практике часто

запирающий ток сравним с током насыщения.

Физика процессов выключения в этом

случае сложнее из-за усложнения формы

распределения носителей в базе. При

больших запирающих токах

Iкн

выключению

соответствует так называемый режим

динамической отсечки, когда и эмиттерный

и колекторный переходы работают при

обратном смещении, но из-за наличия

некоторого остаточного заряда в базе

все три тока транзистора имеют конечные

зачения (не равны нулю) и спадают до нуля

с постоянной времени отсечки, равной

Iкн

выключению

соответствует так называемый режим

динамической отсечки, когда и эмиттерный

и колекторный переходы работают при

обратном смещении, но из-за наличия

некоторого остаточного заряда в базе

все три тока транзистора имеют конечные

зачения (не равны нулю) и спадают до нуля

с постоянной времени отсечки, равной

,

значительно меньшей

,

значительно меньшей

.

В таком случае длительность выключения

коллекторного тока составляет величину:

.

В таком случае длительность выключения

коллекторного тока составляет величину:

;

( 15 )

;

( 15 )

ток спадает очень быстро.

В то же время длительность фронта выключения напряжения при наличии емкостной нагрузки Cк (Cн >Cк) может быть существенно больше, чем длительность выключения тока, и составляет

( 16 )

( 16 )

4. БАЗОВЫЕ ЛОГИЧЕСКИЕ ЭЛЕМЕНТЫ ТТЛ

ТТЛ - обозначает получившую широкое распространение технологию изготовления интегральных схем (ИС) – транзисторно-транзисторную логику. Отличительной особенностью данной технологии является использование на входах ИС многоэмиттерных транзисторов.

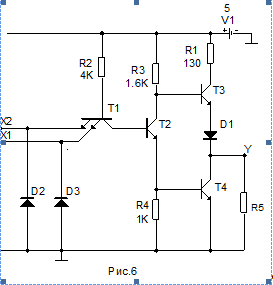

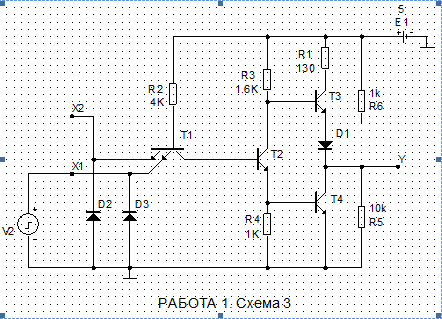

На рис.6 показан базовый логический элемент (ЛЭ), выполненный по технологии ТТЛ и реализующий логическое преобразование И-НЕ. Базовым является тот ЛЭ, физические параметры которого наиболее полно характеризуют физические свойства большинства ИС определенной серии ЛЭ. Например, базовый элемент рис.6 характеризует свойства ИС серии SN74 фирмы Texas Instruments Inc. (TI) и отечественной 155 серии, в которых он применен. ИС серии SN74 (155) предназначены для применения в среднечастотных цифровых узлах (до 35 МГц).

Существуют модификации базового элемента ТТЛ, определяющие свойства соответствующих ИС и другую область их применения. Так, к примеру, ИС серии SN74L (134) предназначены для применения в низкочастотных узлах (до 3 МГц), а ИС серии SN74H (131) – в высокочастотных (до 50 МГц). Совершенствование ТТЛ-технологий изготовления ИС привело к созданию базового элемента ТТЛ с использованием диодов Шоттки, предотвращающих режим глубокого насыщения транзисторов – ТТЛШ.

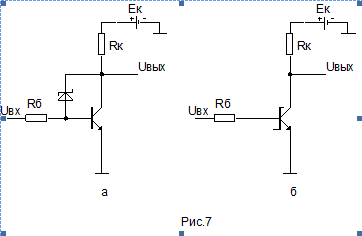

На рис.7,а показано включение диода Шоттки в простейшем ключе. В ключе рис.7,б использован транзистор Шоттки. Прямое пороговое напряжение диодов Шоттки равно 0,3...0,4 В, поэтому в схемах рис.7 напряжение на коллекторном переходе транзистора никогда не достигает значений, при которых он смещен в прямом направлении. Поэтому транзистор с диодом Шоттки не попадает в режим насыщения. Базовые элементы ТТЛШ используются, к примеру, в интегральных схемах серии SN74S (531).

Анализ схемы рис.6 показывает, что многоэмиттерный транзистор Т1 выполняет логическую операцию И, а транзистор Т2 - операцию НЕ. Выходной каскад на транзисторах Т3 и Т4 позволяет получить большие значения втекающего и вытекающего токов в нагрузке, подключаемой к выходу Y ЛЭ. Для получения максимальных значений токов в нагрузке один из выходных транзисторов должен быть обязательно закрыт. Диод D1 в эмиттерной цепи транзистора Т3 обеспечивает его надежное запирание при открытом транзисторе Т4. При запертом состоянии транзистора Т4 транзистор Т3 по отношению к нагрузке работает как эмиттерный повторитель. Резистор R1 предотвращает выход из строя транзистора T3 при коротком замыкании выхода на корпус и снижает уровень импульсных помех при переключении ЛЭ.

Выход ЛЭ с показанным на рис.6 соединением выходных транзисторов Т3 и Т4 называется стандартным выходом.

Диоды, включенные между входными выводами и общим выводом, обеспечивают защиту ЛЭ при попадании на его входы отрицательного напряжения.

Статические режимы в логических элементах ТТЛ характеризуются стандартными параметрами, к которым относятся уровни входных и выходных напряжений и значения входных и выходных токов:

-

входное напряжение высокого уровня

(логической единицы),

-

входное напряжение высокого уровня

(логической единицы),

-

входное напряжение низкого уровня

(логического нуля),

-

входное напряжение низкого уровня

(логического нуля),

-

выходное напряжение высокого уровня

(логической единицы),

-

выходное напряжение высокого уровня

(логической единицы),

-

выходное напряжение низкого уровня

(логической единицы),

-

выходное напряжение низкого уровня

(логической единицы),

(при

(при

)

- входной ток при подаче на вход высокого

уровня напряжения (втекающий ток),

)

- входной ток при подаче на вход высокого

уровня напряжения (втекающий ток),

(при

(при

)

- входной ток при подаче на вход низкого

уровня напряжения (вытекающий ток),

)

- входной ток при подаче на вход низкого

уровня напряжения (вытекающий ток),

( при

( при

)

– выходной ток при высоком уровне

выходного сигнала (вытекающий ток),

)

– выходной ток при высоком уровне

выходного сигнала (вытекающий ток),

(при

(при )

– выходной ток при низком уровне

выходного сигнала (втекающий ток).

)

– выходной ток при низком уровне

выходного сигнала (втекающий ток).

Отношения

и

и

характеризуют

нагрузочную способность ЛЭ для низких

и высоких уровней сигналов. Стандартный

параметр

характеризуют

нагрузочную способность ЛЭ для низких

и высоких уровней сигналов. Стандартный

параметр

определяет максимальное число входов

базовых ЛЭ, которое допустимо подключать

к выходу аналогичного ЛЭ. Для базового

ЛЭ серии SN74

нагрузочная способность

определяет максимальное число входов

базовых ЛЭ, которое допустимо подключать

к выходу аналогичного ЛЭ. Для базового

ЛЭ серии SN74

нагрузочная способность

Помехоустойчивость ЛЭ определяется стандартными значениями величин

Помехи с уровнем напряжения менее 0,4 В не могут привести к изменению состояния ЛЭ.

Переход ЛЭ в

усилительный режим (режим переключения)

характеризуется значением напряжения

переключения. Для базового ЛЭ серии

SN74

стандартное

значение напряжения переключения

.

.

Анализ схемы рис.6

показывает, что типовые значения

выходного напряжения равны

и

и

,

поэтому типовое значение помехоустойчивости

для базового ЛЭ серии SN74

определяется

значениями величин

,

поэтому типовое значение помехоустойчивости

для базового ЛЭ серии SN74

определяется

значениями величин

Стандартные

динамические параметры ЛЭ характеризуются

временами задержки

при

переходе выходного сигнала с высокого

уровня на низкий,

при

переходе выходного сигнала с высокого

уровня на низкий,

-

при переходе выходного сигнала с низкого

уровня на высокий или средним временем

задержки сигналов в ЛЭ

-

при переходе выходного сигнала с низкого

уровня на высокий или средним временем

задержки сигналов в ЛЭ

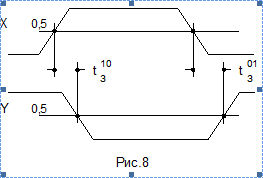

Задержки

Задержки

и

и показаны

на рис.8 (

показаны

на рис.8 ( -

эквивалентный входной сигнал ЛЭ,

учитывающий взаимодействие физических

входных сигналов

-

эквивалентный входной сигнал ЛЭ,

учитывающий взаимодействие физических

входных сигналов

и

и на

рис.6;

на

рис.6;

-

выходной сигнал ЛЭ). Для стандартной

серии SN74

-

выходной сигнал ЛЭ). Для стандартной

серии SN74

.

Указанное значение

.

Указанное значение

позволяет

использовать триггеры данной серии при

частоте переключения

позволяет

использовать триггеры данной серии при

частоте переключения

.

Для других серий ИС, построенных на

модифицированных базовых схемах ТТЛ,

эти параметры равны: серия SN74L

-

.

Для других серий ИС, построенных на

модифицированных базовых схемах ТТЛ,

эти параметры равны: серия SN74L

-

,

, ;

серия SN74H

-

;

серия SN74H

-

,

, ;

серия SN74S

-

;

серия SN74S

-

,

, .

.

Упомянутые выше серии ИС ТТЛ, в названиях которых используется префикс SN, разработаны фирмой TI. Перечисленные ИС помимо фирмы-разработчика выпускаются многими другими фирмами -изготовителями. Другие фирмы-изготовители используют иные префиксы для идентичных ИС, поэтому в справочниках по ИС и учебной литературе префикс часто опускается.

В частности, названия цифровых ИС, включенных в библиотеку программы Micro-Cap (Component > Digital Library), не содержат префикса, обозначающего фирму изготовителя.

5. ПРОГРАММА РАБОТЫ

5.1 ПОДГОТОВКА К РАБОТЕ

1. Изучить:

а) модели биполярных транзисторов и схемы замещения ключей в статических состояниях,

б) влияние резистивной нагрузки (параллельно транзистору или коллекторному резистору) на токи и напряжения в ключах в статических состояниях,

в) физику процессов при переключении транзистора из запертого состояния в насыщенное (задержка отпирания, фронт включения, накопление заряда) и из насыщенного состояния в запертое (рассасывание избыточного заряда, фронт выключения),

г) влияние коллекторной емкости и емкости нагрузки на переходные процессы в ключах,

д) особенности статических режимов и переключения транзисторов в ключе с управляющим транзистором (рис.2),

е) принцип работы базового логического элемента ТТЛ (рис.6), его свойства и характеристики (физика работы в статических состояниях и в режиме переключения, реализуемая логическая функция, стандартные статические и динамические параметры, работа при подключении нагрузки и сохранение работоспособности при ее подключении).

2. Исходные данные

для выполнения расчетов (параметры

элементов схем рис.1 и рис.2, в скобках

приведены имена параметров моделей биполярных транзисторов, используемые

в программе Micro-Cap):

биполярных транзисторов, используемые

в программе Micro-Cap):

,

, ,

, ,

, ,

,

,

,

,

,

,

,

,

,

,

,

,

,

,

,

.

.

3. Рассчитать для схемы рис.1, используя соответствующие модели транзистора:

а)

статическое напряжение

,

при котором транзистор отпирается,

,

при котором транзистор отпирается,

б)

статическое напряжение

,

при котором транзистор входит в насыщение,

,

при котором транзистор входит в насыщение,

в) статические уровни выходного напряжения для ненагруженного ключа,

г)

статические уровни выходного напряжения,

если параллельно транзистору включен

резистор нагрузки

,

,

д)

минимальное сопротивление резистора

нагрузки

,

включенного параллельно резистору

,

включенного параллельно резистору

,

при котором открытый транзистор остается

насыщенным,

,

при котором открытый транзистор остается

насыщенным,

е)

зависимости длительности фронта

включения

,

длительности стадии рассасывания

,

длительности стадии рассасывания

и длительности фронта выключения

и длительности фронта выключения

от амплитуды входных отпирающих

импульсов.

от амплитуды входных отпирающих

импульсов.

4. Рассчитать для

схемы рис.2, используя соответствующие

модели транзистора, длительность стадий

переключения ключа

,

,

,

,

,

если ключ управляется положительными

импульсами с амплитудой

,

если ключ управляется положительными

импульсами с амплитудой

.

Начальный уровень входного напряжения

считать равным нулю.

.

Начальный уровень входного напряжения

считать равным нулю.

5.2 ВЫПОЛНЕНИЕ РАБОТЫ

(результаты по всем пунктам программы работы документировать и включить в отчет)

1. Вызвать программу Micro-Cap (ярлык Micro-Cap Evaluation 8.0)

2. Открыть (File > Open > DATA RUS > 1p-1.CIR) и исследовать

Схему 1:

а) получить передаточные характеристики (ПХ) ключей (Analysis > DC... > Run);

б) определить по ним напряжения, при которых транзисторы открываются и при которых входят в насыщение, сравнить полученные значения с расчетными;

в) определить и объяснить значения статических уровней ПХ;

г) подключить нагрузку R5 на выход ключа и повторить п.п. а) и в), сравнить значения уровней ПХ с результатами расчета;

д) получить ПХ ключей при вариации сопротивления нагрузки R5 (DC > Stepping > Step It Yes > OK > F2); проследить за изменением формы ПХ, задокументировать и объяснить изменения;

е) выключить режим вариации сопротивления нагрузки и выйти из режима анализа (DC > Stepping > Step It No > OK > F3);

ж) выключить нагрузку R5;

з) получить переходные характеристики ключей (Analysis > Transient > Run), определить стадии переходных процессов при включении и выключении транзисторов, сравнить работу ключей и объяснить результаты;

и) получить переходные характеристики ключей при вариации амплитуды управляющих импульсов (Transient > Stepping > Step It Yes > OK > F2); получить и построить графики зависимостей длительности фронта включения, длительности стадии рассасывания, длительности фронта выключения от амплитуды входных импульсов, сравнить с расчетными зависимостями; проследить за изменением формы выходных импульсов, задокументировать изменения;

к) выключить режим вариации амплитуды управляющих импульсов и выйти из режима анализа (Transient > Stepping > Step It No > OK > F3);

л) закрыть Схему 1 (File > Сlose > No Save...).

2. Открыть (File > Open > DATA RUS > 1p-2.CIR) и исследовать

Схему 2:

а)

получить статические характеристики

выходного напряжения

и входного тока

и входного тока

от

значения статического напряжения

от

значения статического напряжения

на

входе ключа (Analysis

> DC...

> Run)

и объяснить поведение и параметры

полученных характеристик;

на

входе ключа (Analysis

> DC...

> Run)

и объяснить поведение и параметры

полученных характеристик;

б) подключить нагрузку R3 и повторить п.а), сравнить и объяснить различие характеристик нагруженного и ненагруженного ключа;

в)

получить статические характеристики

ключей при вариации сопротивления

нагрузки R3

(DC

> Stepping

> Step

It

Yes

> OK

> F2);

проследить за изменениями характеристик,

задокументировать и объяснить изменения;

определить минимальное допустимое

сопротивление нагрузки, при котором

выходное напряжение не превышает

стандартное значение

для элементов ТТЛ;

для элементов ТТЛ;

г) выключить режим вариации сопротивления нагрузки и выйти из режима анализа (DC > Stepping > Step It No > OK > F3);

д) выключить нагрузку R3;

е) закрыть Схему 2 (File > Сlose > No Save...).

3. Открыть (File > Open > DATA RUS > 1p-3.CIR) и исследовать

Схему 3:

а)

получить статические характеристики

выходного напряжения

,

входного тока

,

входного тока

и тока

и тока

в

резисторе выходного каскада от значения

входного статического напряжения

в

резисторе выходного каскада от значения

входного статического напряжения

(Analysis

> DC...

> Run);

объяснить поведение характеристик;

(Analysis

> DC...

> Run);

объяснить поведение характеристик;

б) определить параметры характеристик входного тока и выходного напряжения и их соответствие стандартным значениям для элементов ТТЛ;

в)

повторить п.п. а)

и б)

при вариации сопротивления нагрузки

R5

(Stepping

> Step

It

Yes

> OK

> F2);

проследить за изменениями характеристик,

задокументировать и объяснить изменения;

определить минимальное допустимое

сопротивление нагрузки, при котором

выходное напряжение не ниже стандартного

значения

для элементов ТТЛ;

для элементов ТТЛ;

г) выключить режим вариации сопротивления нагрузки и выйти из режима анализа (DC > Stepping > Step It No > OK > F3);

д)

получить временную диаграмму выходного

напряжения

при

воздействии на вход импульсного

напряжения

при

воздействии на вход импульсного

напряжения

(Analysis

>Transient

> Run)

; измерить задержки фронтов выходного

напряжения и их соответствие стандартным

значениям базового элемента ТТЛ;

(Analysis

>Transient

> Run)

; измерить задержки фронтов выходного

напряжения и их соответствие стандартным

значениям базового элемента ТТЛ;

е) заземлить вход X2 и повторить п. д); сформулировать вывод о влиянии на работу элемента ТТЛ свободного (неподключенного) и заземленного входа; получить таблицу истинности для базовой схемы рис.3 как логического элемента;

ж) выйти из режима анализа (F3);

з) закрыть Схему 3 (File > Сlose > No Save...).

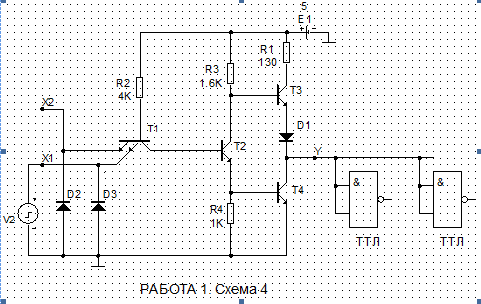

4. Открыть (File > Open > DATA RUS > 1p-4.CIR) и исследовать

Схему 4:

а) отключить внешние ЛЭ (нагрузку) от выхода Y исследуемой схемы;

б) определить статические и динамические параметры ЛЭ;

в) коммутируя линии подключения нагрузки, повторить п. б) для разного числа входов нагрузки;

в) сформулировать выводы о влиянии нагрузки на рабочие параметры ЛЭ;

г) выйти из режима анализа (F3);

д) закрыть Схему 4 (File > Сlose > No Save...).

5. Получить у преподавателя дополнительное задание по работе.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1.Разевиг В.Д. Схемотехническое моделирование с помощью Micro-Cap 7. – М.: Горячая линия – Телеком, 2003. – 368 с.

2.Элементы импульсных и цифровых устройств: Руководство к лабораторным работам №1027 / Сост. Белкин А.П., Сальников Н.И., Соколов Ю.П. – Рязань. : РРТИ, 1985. - 44 с.

3.Сальников Н.И., Белкин А.П., Соколов Ю.П. Импульсные устройства на интегральных логических элементах: Учебное пособие. – Рязань: РРТИ, 1986. – 72 с.

4.Ерофеев Ю.Н. Импульсная техника: Учеб пособие. - М.: Высш. шк., 1984. – 391 с.

5.Алексенко А.Г., Шагурин И.И. Микросхемотехника: Учеб. пособие. – М.: Радио и связь, 1982. – 416 с.

6.Пухальский Г.И., Новосельцева Т.Я. Цифровые устройства: Учеб. пособие. СПб.: Политехника, 1996.