Система команд микроконтроллеров

Система команд микроконтроллеров

В семействе AVR система команд у микроконтроллеров разных типов содержат от 89 до 130 команд (табл. В1, колонка NK). У микроконтроллеров типа 2323, 2343, 2313, 4433, 8515 и 8535 в систему команд входят 118 команд. Эту систему команд будем называть базовой.

В табл. 1—13 описаны операции, выполняемые по командам базовой системы, и приведены мнемокоды команд, используемые при разработке программы на языке AVR Ассемблера. В таблицах дана сквозная нумерация команд, используемая далее в тексте.

Базовая система команд содержит:

■ 33 команды регистровых операций, при выполнении которых используются только регистры общего назначения (команды №№ 1—33);

■ 26 команд с обращением по адресу в адресном пространстве SRAM (команды №№ 34—59);

■ 2 команды с обращением к регистрам ввода-вывода (команды №№ 60 и 61);

■ 1 команда с обращением к FlashROM (команда № 62);

■ 22 команды операций с битами в разрядах регистров общего назначения и регистров ввода-вывода (команды №№ 63—84);

■ 34 команды управления ходом программы (команды №№ 85—118).

В систему команд микроконтроллеров типа t1l, t12, t15, 1200 и t28, у которых нет SRAM, не входят команды с обращением по адресу в адресном пространстве SRAM за исключением команд с мнемокодами LD Rd, Z (№ 40) и ST Z, Rr (№ 41), по которым производится обращение к регистрам общего назначения и регистрам ввода-вывода с использованием косвенной адресации. В систему команд у этих микроконтроллеров не входят также 2 команды регистровых операций (№№ 32 и 33) и две команды управления ходом программы (№№ 86 и 88). У микроконтроллеров типа 1200 в систему команд не входит также команда с обращением к FlashROM (№ 62).

В систему команд микроконтроллеров типа m163 и m10З входят дополнительные команды. Появление некоторых из них связано с увеличенным объемом FlashROM, а у микроконтроллера типа т163, кроме того, с наличием аппаратного умножителя.

При разработке программы работы микроконтроллера кроме мнемокодов команд используются директивы ассемблера и другие средства ассемблера. Особенности разработки программы на языке AVR Ассемблера фирмы Atmel рассмотрены в приложении П8.

Таблица 1

|

№ |

Операция |

Мнемокод команды |

Признаки результата |

|||||

|

H |

S |

V |

N |

Z |

C |

|||

|

1 |

|

CLR |

0 |

0 |

0 |

1 |

||

|

2 |

|

TST |

+ |

0 |

+ |

+ |

||

|

3 |

|

COM |

+ |

0 |

+ |

+ |

1 |

|

|

4 |

|

NEG |

+ |

+ |

+ |

+ |

+ |

+ |

|

5 |

|

INC |

+ |

+ |

+ |

+ |

||

|

6 |

|

DEC |

+ |

+ |

+ |

+ |

||

|

7 |

|

LSR |

+ |

+ |

0 |

+ |

+ |

|

|

8 |

|

LSL |

+ |

+ |

+ |

+ |

+ |

+ |

|

9 |

|

ROR |

+ |

+ |

+ |

+ |

+ |

|

|

10 |

|

ROL |

+ |

+ |

+ |

+ |

+ |

+ |

|

11 |

|

ASR |

+ |

+ |

+ |

+ |

+ |

|

|

12 |

|

SWAP |

||||||

|

13 |

|

MOV |

||||||

|

14 |

|

ADDV |

+ |

+ |

+ |

+ |

+ |

+ |

|

15 |

|

ADC |

+ |

+ |

+ |

+ |

+ |

+ |

|

16 |

|

sub> |

+ |

+ |

+ |

+ |

+ |

+ |

|

17 |

|

SBC |

+ |

+ |

+ |

+ |

+ |

+ |

|

18 |

|

CP |

+ |

+ |

+ |

+ |

+ |

+ |

|

19 |

|

CPC |

+ |

+ |

+ |

+ |

+ |

+ |

|

20 |

|

AND |

+ |

0 |

+ |

+ |

+ |

|

|

21 |

|

OR |

+ |

0 |

+ |

+ |

||

|

22 |

|

EOR |

+ |

0 |

+ |

+ |

||

|

d = 0 – 31, r = 0 – 31 |

Таблица 2

-

№

Операция

Мнемокод команды

Признаки результата

23

SER

H

S

V

N

Z

C

24

LDI

25

sub>I

+

+

+

+

+

+

26

SBCI

+

+

+

+

+

+

27

CPI

+

+

+

+

+

+

28

ANDI

+

0

+

+

29

CBR

+

0

+

+

30

ORI

+

0

+

+

31

SBR

+

0

+

+

d = 16 – 31 (‘), K = 0 – 255

Таблица 3

-

№

Операция

Мнемокод команды

Признаки результата

H

S

V

N

Z

C

32

ADIW

+

+

+

+

+

33

SBIW

+

+

+

+

+

d = 24, 26, 28, 30, K = 0 – 63

Таблица 4

-

№

Операция

Мнемокод команды

№

Операция

Мнемокод команды

34

LSD

35

STS

d, r = 0 – 31, k – адрес из адресного пространства SRAM

Таблица 5

-

№

Операция

Мнемокод команды

№

Операция

Мнемокод команды

36

LD

37

ST

38

LD

39

ST

40

LD

41

ST

42

1

2

LD

43

1

2

ST

44

1

2

LD

45

1

2

ST

46

1

2

LD

47

1

2

ST

48

1

2

LD

49

1

2

ST

50

1

2

LD

51

1

2

ST

52

1

2

LD

53

1

2

ST

54

LDD

55

ST

56

LDD

57

ST

58

1

2

POP

59

1

2

PUSH

d, r = 0 – 31, q = 0 – 63

Таблица 6

-

№

Операция

Мнемокод команды

№

Операция

Мнемокод команды

60

IN

61

OUT

d, r = 0 – 31, P = 0 – 63 = $00-$3F

Таблица 7

-

№

Операция

Мнемокод команды

(Z.15-1) – адрес в FlashROM

Z.0 = 0 – мл. байт; Z.0 = 1 – ст. байт

62

LPM

Таблица 8

|

№ |

Операция |

Мнемокод команды |

№ |

Операция |

Мнемокод команды |

|

63 |

|

BLD |

64 |

|

BST |

|

65 |

|

CBI |

66 |

|

SBI |

|

67 |

|

BCLR |

68 |

|

BSET |

|

d, r = 0 – 31; P = 0 – 31(!); b = 0 – 7 |

Таблица 9

-

№

Операция

Мнемокод команды

№

Операция

Мнемокод команды

69

CLI

70

SEI

71

CLT

72

SET

73

CLH

74

SHE

75

CLS

76

SES

77

CLV

78

SEV

79

CLN

80

SEN

81

CLZ

82

SEZ

83

CLC

84

SEC

Таблица 10

-

№

Операция

Мнемокод команды

№

Операция

Мнемокод команды

85

RJMP k

86

IJMP

87

1.

2.

3.

RCALL k

88

1.

2.

3.

ICALL

89

1.

2.

RET

90

1.

2.

3.

RETI

k = -2048 - +2047

В группу регистровых операций входят пересылочные, арифметические и логические операции. Команды регистровых операций описаны в табл. 1, 2 и 3. Машинные коды всех команд регистровых операций имеют формат "слово", команды №№ 1—31 выполняются за один такт, а команды №№ 32 и 33 — за два такта.

При описании операций в табл. 1—3 используются следующие обозначения:

Таблица 11

|

№ |

Операция |

Мнемокод команды |

№ |

Операция |

Мнемокод команды |

|

91 |

I = 0 |

BRID k |

92 |

I = 1 |

BRIE k |

|

93 |

T = 0 |

BRTC k |

94 |

T = 1 |

BRTS k |

|

95 |

H = 0 |

BRHC k |

96 |

H = 1 |

BRHS k |

|

97 |

S = 0 |

BRGE k |

98 |

S = 1 |

BRLT k |

|

99 |

V = 0 |

BRVC k |

100 |

V = 1 |

BRVS k |

|

101 |

N = 0 |

BRPL k |

102 |

N = 1 |

BRMI k |

|

103 |

Z = 0 |

BRNE k |

104 |

Z = 1 |

BREQ k |

|

105 |

C = 0 |

BRCC k |

106 |

C = 1 |

BRCS k |

|

107 |

C = 0 |

BRSH k |

108 |

C = 1 |

BRLO k |

|

109 |

SREG.b=0 |

BRBC b, k |

110 |

SREG.b= 1 |

BRBS b, k |

|

k = -64 – +63; b = 0 – 7 |

Таблица 12

|

№ |

Операция |

Мнемокод команды |

№ |

Операция |

Мнемокод Команды |

|

111 |

|

SBRC

|

112 |

|

SBRS

|

|

113 |

|

SBIC

|

114 |

|

SBIS

|

|

115 |

|

CPSE

|

|||

|

d, r = 0 – 31; P = 0 – 31 (!); b = 0 – 7 |

Таблица 13

|

№ |

Операция |

Мнемокод команды |

|

116 |

МК – режим энергосбережения |

SLEEP |

|

117 |

Перезапуск WDT |

WDR |

|

118 |

Нет |

NOP |

■ RdRr — регистры общего назначения с номерами d и r соответственно;

■ (Rd), (Ri) — байты в регистрах Rd n R, соответственно;

■ Rd.b — разряд b (b = 0—7) регистра Rfi, бит в разряде Rd.b;

■ $ — указатель шестнадцатернчного кода;

■ ^, v, + - знаки логических операции И, ИЛИ, исключающее ИЛИ соответственно;

■ (‾)/( ),( ) — знаки операции НЕ, сдвиг кода вправо, сдвиг кода влево соответственно.

Арифметические операции — сложение и вычитание — могут выполняться с числами без знака в двоичном коде и с числами со знаком в дополнительном двоичном коде. В отличие от микроконтроллеров многих других семейств, в которых вычитание сводится к сложению с числом с измененным знаком (X-Y = X + (-Y )), в микроконтроллерах семейства AVR вычитание выполняется с помощью аппаратного двоичного вычитателя. Работа двоичного вычитателя рассмотрена в приложении П7.

При выполнении арифметических и логических операций кроме кода результата формируются значения признаков результата. При выполнении операций сравнения (команды М»№ 18, 19 и 27) формируются только значения признаков результата.

Значения признаков результата представлены состоянием разрядов регистра состояния SREG (№ S3F). Используются тесть признаков результата, которым присвоены имена С (SREG.O), Z (SREG.1) N (SREG.2), V (SREG.3), S (SREG.4) и Н (SREG.5). В табл. 1-3 признаки, значения которых формируются при выполнении команд, отмечены знаком "+" пли указано их значение.

При выполнении разных операций значение признаков формируются по разным правилам.

Признак С принимает единичное значение:

■ при появлении единицы переноса из старшего разряда при выполнении операции сложения (команды №№ 14, 15 и 32);

■ при появлении единицы займа в старший разряд при выполнении операции вычитания (команды №>№ 4, 16, 17, 18, 19, 25, 26, 27 и 33);

■ при выходе единицы за пределы разрядной сетки при выполнении операции сдвига (команды №№ 7, 8, 9, 10 и 11).

Единичное значение признака С при выполнении операций сложения и вычитания с числами без знака свидетельствует о получении неправильного результата операции вследствие переполнения разрядной сетки.

Признак Z принимает единичное значение при получении нулевого результата операции. При выполнении операции вычитания с учетом займа (команды №№ 17, 19 и 26) Z = 1, если нулевой результат получен при выполнении данной и предшествующей операций.

Признак N имеет значение, равное значению старшего разряда кода результата. При выполнении арифметических операции с числами со знаком и отсутствии переполнения разрядной сетки он представляет знак результата.

Признак V принимает единичное значение, если при выполнении арифметической операции с числами со знаком возникло переполнение разрядной сетки.

Признак S = N+V представляет знак результата при выполнении арифметических операций с числами со знаком вне зависимости от переполнения разрядной сетки. При переполнении разрядной сетки (V=l) знак результата противоположен значению в старшем разряде кода результата.

Признак Н принимает единичное значение при наличии единицы переноса из разряда D3 в разряд D4 при выполнении операции сложения, при наличии единицы займа в разряд D3 из разряда D4 при выполнении операции вычитания и при передаче единицы из разряда D3 в разряд D4 при выполнении операции сдвига кода влево.

Команды с обращением по адресу SRAM

По командам с обращением по адресу в адресном пространстве SRAM выполняются операции пересылки (копирования) байта между регистром общего назначения и элементом, которому соответствует адрес в адресном пространстве SRAM. Таким элементом может быть регистр общего назначения (адреса от $00 до $1F), регистр ввода-вывода (адреса от $20 до $5F), ячейка памяти в SRAM (адреса от $60 до максимального адреса в SRAM), ячейка памяти в ERAM (адреса от максимального адреса в SRAM +1 до максимального адреса в ERAM) (см. п. 1.5).

Команды с обращением по адресу в адресном пространстве SRAM описаны в табл. 4 и 5.

Машинные коды команд №№ 34 и 35 имеют формат "2 слова", машинные коды остальных команд — формат "слово". Команды выполняются за 2 такта, а при обращении к ячейкам в ERAM — за 3 такта. В случае необходимости в цикл выполнения команды при обращении к ERAM может быть введен дополнительный такт ожидания.

В табл. 4 и 5 используются следующие новые обозначения:

■ ЯчА — регистр общего назначения, регистр ввода-вывода, ячейка памяти в SRAM, ячейка памяти в ERAM, к которым производится обращение с использованием адреса А из адресного пространства SRAM;

■ (ЯчА) - байт в ЯчА;

■ X, Y, Z — пара регистров общего назначения X (R26, R27), Y (R28, R29), Z (R30, R31) соответственно;

■ (X), (Y), (Z) — слово в паре регистров X, Y, Z соответственно;

■ СТЕК — ЯчА, к которой производится обращение с использованием адреса, хранящегося в регистре-указателе стека SP;

■ (СТЕК) - байт в СТЕК, е;

■ (SP) — код числа в регистре SP.

В командах №№ 34 и 35 реализуется прямая адресация. Адрес байта (А = к) указывется в коде команды.

В командах №№ 36—57 реализуется косвенная адресация. Адрес байта находится в паре регистров X, Y или Z. При выполнении команд №№ 42—47 после выполнения пересылки адрес в паре регистров аппаратно увеличивается па единицу. При выполнении команд №№ 48—53 до выполнения пересылки адрес в паре регистров аппаратно уменьшается на единицу. При выполнении команд №№ 54—57 адрес, по которому производится обращение, равен адресу в паре регистров Y или Z, увеличенному на число q, которое указано в коде команды. Адрес в паре регистров остается без изменения.

В командах №№ 58 и 59 в качестве кода адреса используется код, находящийся в регистре-указателе стека. При запуске микроконтроллера в регистр-указатель стека заносится код числа 0. Для нормальной работы стека в регистр-указатель стека в начале программы необходимо занести код другого числа. Обычно в качестве такого числа используют старший адрес в SRAM. Например, для микроконтроллера типа 8515 таким адресом является число $025F.

Команды с обращением к регистрам ввода–вывода

По командам с обращением к регистрам ввода-вывода выполняются операции пересылки (копирования) байта между регистром общего назначения и регистром ввода-вывода с использованием для выбора регистра ввода-вывода его номера ($00 - $3F). Команды с обращением к регистрам ввода-вывода описаны в табл. 6. Машинные коды команд имеют формат "слово". Команды выполняются за один такт.

В табл. 6 используются следующие новые обозначения:

■ РгР — регистр ввода-вывода с номером Р;

■ (РгР) — байт в регистре РгР.

При записи мнемокода команды вместо конкретного номера регистра может использоваться его символическое имя. Все регистры ввода-вывода имеют штатные имена. Имена регистров ввода-вывода и их номера приведены в приложении П4. У микроконтроллеров разных типов регистры ввода-вывода, имеющие одинаковые имена, могут иметь разные номера. При записи в мнемокодах имен регистров вместо их номера необходимо использовать версию AVR-Ассемблера для микроконтроллера данного типа.

Команда с обращением к FlashROM

По команде с обращением к FlashROM выполняется пересылка (копирование) байта из половины ячейки памяти в FlashROM в регистр общего назначения R0. Команда описана в табл. 7. Машинный код команды имеет формат "слово". Команда выполняется за три такта.

До выполнения команды необходимо адрес, соответствующий ячейке памяти в FlashROM, в которой хранится константа, умножить на 2 и записать в пару регистров Z (№№ $30, $31).

При умножении на 2 (сдвиг кода влево на один разряд) в младшем разряде регистра ZL ($30) оказывается цифра 0. При нулевом значении младшего разряда выбирается байт из младшей половины ячейки FlashROM. Для выбора байта из старшей половины ячейки необходимо число, код которого находится в паре регистров Z, увеличить на 1 с использованием команды № 33 с мнемокодом ADIW R30, 1 или ADIW ZL, 1.

Запись констант в FlashROM выполняется при программировании микроконтроллера.

Команды операций с битами

Команды операций с битами описаны в табл. 8 и 9. Машинные коды всех команд имеют формат "слово". Команды №№ 65 и 66 выполняются за 2 такта, остальные команды — за 1 такт.

В табл. 8 используется следующее новое обозначение:

■ РгР.b — разряд b (b = 0—7) регистра ввода-вывода с номером Р (Р = $00 - $1F (!)), бит в разряде РгР.Ь.

По командам №№ 63 и 64 выполняется пересылка (копирование) бита между указанным разрядом регистра общего назначения и разрядом Т регистра SREG.

По командам №№ 65 и 66 устанавливается в требуемое состояние (0 или 1 соответственно) указанный разряд регистра ввода-вывода, а по командам №№ 67 и 68 - указанный разряд регистра SREG.

При записи мнемокодов команд №№ 65 и 66 вместо номера регистра (Р) может быть указано его символическое имя (см. приложение П4), а вместо номера разряды (b) — символическое имя разряда. В микроконтроллерах семейства AVR разряды многих регистров ввода-вывода имеют штатные имена. Эти имена приводятся в тексте при рассмотрении устройств, в которых эти разряды используются. Штатные имена разрядов регистров ввода-вывода, управляющих работой различных устройств микроконтроллера и отражающих состояние этих устройств приведены в приложении П5.

В микроконтроллерах некоторых типов разряды одноименных регистров с одинаковыми именами имеют разные номера. При использовании штатных имен регистров ввода-вывода и штатных имен разрядов в них необходимо использовать версию AVR Ассемблера для микроконтроллера соответствующего типа.

При назначении штатного имени разряда подразумевалось, что этот разряд принадлежит определенному регистру ввода-вывода, однако в мнемокоде команд №№ 65 и 66 необходимо указывать и имя/номер регистра и имя разряда. Требуемое значение бита (0 или 1) в разрядах регистров ввода-вывода с номерами от $20 до $3F устанавливается с использованием команд регистровых операций с мнемокодами CBR (№ 29) и SBR (№ 31) соответственно.

В табл. 9 приведены мнемокоды команд, по которым устанавливается в определенное состояние (0 или 1) разряды регистра SREG без указания в мнемокоде команды номера разряда.

В группу команд управления ходом программы входят команды безусловного и условного переходов, перехода в энергосберегающий режим, перезапуска сторожевого таймера и "холостая" команда.

В табл. 10 описаны команды безусловного перехода (№№ 85 и 86), безусловного перехода с возвратом (№№ 87 и 88), возврата из подпрограммы (№ 89) и возврата из прерывающей программы (№ 90). В таблице используются следующие новые обозначения:

■ PC — счетчик команд;

■ (PC) — код числа в счетчике команд;

■ k- приращение числа в счетчике команд.

При записи программы на языке ассемблера в мнемокодах команд №№ 85 и 87 вместо приращения к указывается метка (символический адрес), записанная перед мнемокодом команды, к выполнению которой нужно перейти. Приращение вычисляется и помещается в машинный код команды в процессе ассемблирования.

Машинные коды команд, описанные в табл. 10, имеют формат "слово". Команды безусловного перехода (№№ 85 и 86) выполняются за 2 такта, команды безусловного перехода с возвратом (№№ 87 и 88) — за 3 такта, команды возврата (№№ 89 и 90) — за 4 такта.

Группа команд условного перехода делится на две подгруппы. В командах первой подгруппы в качестве условия используется равенство нулю или равенство единице одного из битов в регистре SREG. Условия н мнемокоды команд первой подгруппы приведены в табл. 11. Если условие выполняется, совершается переход по адресу, который формируется с использованием приращения к, указанного в коде команды ((PC) + 1 + k-PC; -64 < k < 63).

Если условие не выполняется, происходит переход к следующей команде в программе ((PC) + 1->РС).

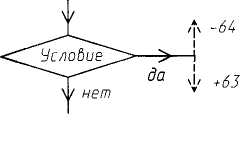

Фрагмент структурной схемы программы с командой условного перехода из первой подгруппы изображен на рис. 1.

При записи программы на языке ассемблера в мнемокоде команд, описанных в табл. 11, вместо приращения к указывается метка (символический адрес), записанная перед мнемокодом команды, к выполнению которой нужно перейти, если условие выполняется.

Машинные коды команд первой подгруппы (табл. 11) имеют формат 'слово". При выполнении условия команда выполняется за 2 такта, при невыполнении условия — за 1 такт.

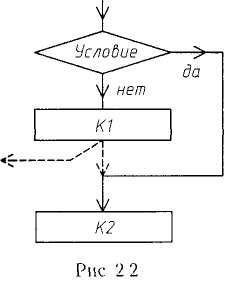

Команды условного перехода второй подгруппы и используемые в них условия описаны в табл. 1 Если условие не выполняется, совершается переход к очередной команде в программе ((PC) + 1-РС). Если условие выполняется, происходит переход к выполнению команды, следующей за очередной ((PC) + 1 + 1/2-РС). Приращение числа в счетчике команд (1 или 2) определяется форматом машинного кода очередной команды (1 слово или 2 слова соответственно). Фрагмент структурной схемы программы с командой условного перехода из второй подгруппы изображен на рис. 2.

Машинные коды команд условного перехода второй подгруппы (табл. 2,12) имеют формат "слово". Команды выполняются за один такт, если условие не выполняется, за 2 такта, если условие выполняется и очередная команда (К1) имеет формат "слово", или за 3 такта, если условие не выполняется и очередная команда (К1) имеет формат "2 слова".

В табл. 13 приведены мнемокоды команд, при выполнении которых совершается переход микроконтроллера в один из энергосберегающих режимов (№ 116), выполняется перезапуск сторожевого таймера (№ 117) или в ходе программы появляется "холостой" такт, в котором не выполняются какие-либо операции (№ 118).

Дополнительные команды в системе команд микроконтроллеров типа m163 и m10З

Операции, выполняемые по командам, и мнемокоды дополнительных команд описаны в табл. 14. Знаком "+" отмечено вхождение команды в систему команд микроконтроллера указанного типа.

Таблица 14

|

№ |

Операция |

Мнемокод команды |

Тип МК |

|

|

m163 |

m103 |

|||

|

119 |

d, r = 0,2 ,…, 30 |

MOVW |

+ |

|

|

120 |

d, r = 0 – 31 |

MUL |

+ |

|

|

121 |

d, r = 16 – 31 |

MULS |

+ |

|

|

122 |

d, r = 16 – 23 |

MULSU |

+ |

|

|

123 |

1. |

FMUL |

+ |

|

|

124 |

2. |

FMULS |

+ |

|

|

125 |

d, r = 16 – 23 |

FMULSU |

+ |

|

|

126 |

|

JMP k |

+ |

+ |

|

127 |

1. 2. 3.

|

CALL k |

+ |

+ |

|

128 |

d = 0 – 31 |

LPM |

+ |

|

|

129 |

1. 2. d = 0 – 31 |

LPM |

+ |

|

|

130 |

|

ELPM |

+ |

|

|

131 |

см. табл. 15 |

SPM |

+ |

По команде регистровой операции с мнемокодом MOVW Rd, Rг (№ 119) выполняется пересылка (копирование) слова из одной пары регистров общего назначения в другую пару регистров. Машинный код команды имеет формат "слово", команда выполняется за один такт.

По трем командам регистровых операций с мнемокодами MUL Rd, Rг MULS Rd, Rr и MULSU Rd, Rr (№№ 120, 121 и 122) выполняется операция умножения, в которой участвует целые числа без знака (MUL), целые числа со знаком (MULS) и целое число со знаком и целое число без знака (MULSU). При выполнении операции формируются значения признаков результата С и Z (С = R1.7, Z = 1, если после выполнения операции (R1) = 0 и (R2) = 0).

По трем командам регистровых операций с мнемокодами операции FMUL, FMULS и FMULSU (№№ 123, 124, 125) выполняется операция умножения с увеличением результата в два раза, в которой участвуют дробные числа без знака (FMUL), дробные числа со знаком (FMULS) и дробное число со знаками и дробное число без знака (FMULSU). Операнды имеют формат 1.7, а результат — формат 1.15, где справа от точки указано число дробных разрядов. При выполнении операции формируются значения признаков результата С и Z (С — результат сдвига влево кода произведения, Z = 1, если после выполнения операции (R1) = 0 и (R0) = 0.)

Машинные коды команд №№ 120—125 имеют формат "слово". Команды выполняются за два такта с использованием аппаратного умножителя.

По командам с мнемокодами JMP k (№ 126) и CALL к (№ 127) совершаются безусловный переход и безусловный переход с возвратом в пределах всего адресного пространства FlashROM. Машинные коды этих команд имеют формат "2 слова". Команды выполняются за 3 JМР) и 4 (CALL) такта.

По командам пересылочных операций с обращением к FlashROM с мнемокодами LPM Rd, Z и LPM Rd, Z+ (№№ 128, 129) выполняется операция пересылки (копирования) константы из половины ячейки FlashROM в любой регистр общего назначения. До выполнения команды необходимо адрес, соответствующий ячейке памяти, в которой хранится константа, умножить на 2 и записать в пару регистров Z. Если требуется прочитать байт из старшей половины ячейки, к числу, код которого записан в паре регистров Z, необходимо добавить 1.

При выполнении команды с мнемокодом LPM Rd, Z+ после пересылки байта число, код которого хранится в паре регистров Z, увеличивается на 1 аппаратно.

Машинные коды команд №№ 128 и 129 имеют формат "с юво". Команды выполняются за 3 такта.

По команде с мнемокодом ELPM (№ 130) выполняется пересылка Константы из половины ячейки FlashROM в регистр R0 (см. команду № 62). В микроконтроллере типа ml03 FlashROM содержит 64 К ячеек памяти. Для размещения старшего разряда кода после умножения на 2 используется разряд RAMPZ0 регистра RAMPZ (№ $ЗВ). Машинный код команды имеет формат "слово". Команда выполняется за 3 такта.

Команда с мнемокодом SPM (№ 131) предназначена для записи байтов в FlashROM в процессе выполнения программы. При выполнении команды используется регистр управления SPMCR (№ $37) и пара регистров Z.

С использованием команды с мнемокодом SPM выполняются следующие операции:

1) пословное заполнение буферного запоминающего устройства (BUF) емкостью 64X16 бит;

2) стирание в FlashROM страницы — группы из 64-х ячеек;

3) перепись 64-х слов из буферного ЗУ в "очищенную" страницу FlashROM.

Для задания номера ячейки в буферном ЗУ используются разряды Z6—Z1 в паре регистров Z. Для задания номера страницы (начального адреса в странице) используются разряды Z13—Z7 в парс регистров Z.

Выбор операции, выполняемой по команде с мнемокодом SPM, определяется кодом, который до выполнения команды SPM, но не ранее, чем за 4 такта до ее выполнения, записывается в регистр SPMCR. Коды, записываемые в регистр SPMCR, и операции, выполняемые при этом по команде SPM, указаны в табл. 15.

Таблица 15

|

(SPMCR) |

Операция |

|

$01 |

|

|

$03 |

-------------------------------------

|

|

$05 |

-------------------------------------

|

|

$09 |

|

При (SPMCR) = $01 по команде SPM слово, ранее записанное в пару регистров R1, R0, пересылается (копируется) в ячейку буферного ЗУ, номер которой указан в разрядах с шестого по первый в паре Z регистров общего назначения. Буферное ЗУ может заполняться в произвольном порядке.

При (SPMCR) = $03 происходит стирание группы ячеек в FlashROM с номерами в двоичном коде от Z.13, ..., Z.7, 0, 0, 0, 0, 0, 0, X до Z.13, .... Z.7, 1, 1, 1, 1, 1, 1, X.

При (SPMCR) = $05 происходит перепись 64-х слов из буферного ЗУ в ранее стертую страницу FlashROM.

При (SPMCR) = $09 производится установка битов защиты (Lock Bits) BLB12, BLB11, BLB02 и BLB01, которые разрешают/запрещают выполнять запись в FlashROM с использованием команды SPM и чтение из FlashROM с использованием команды LPM.

Литература

Тавернье К. PIC-микроконтроллеры. Практика применения: Пер. с фр. -М: ДМКПресс, 2008. - 272 с.: ил. (Серия «Справочник»).

Борзенко А.Е. IBM PC: устройство, ремонт, модернизация. – 2-е изд. перераб. и доп. – М.: ТОО фирма «Компьютер Пресс», 2006. – 344с.: ил.

Цифровые интегральные микросхемы: Справ./М. И. Богданович, И.Н. Грель, В.А. Прохоренко, В.В. Шалимо.–Мн.: Беларусь, 2001. – 493 с.: ил.