Разработка цифрового фазового корректора

Министерство образования и науки РФ

Пояснительная записка

к курсовому проекту по дисциплине

"Цифровые устройства и микропроцессоры"

Студент Тришин С.В.

Группа 114 специальность 2007

2004

Содержание

1. Постановка задачи (введение)

2. Формализация задачи

3. Разработка и описание общего алгоритма функционирования устройства

4. Обоснование аппаратной части устройства

5. Разработка и отладка программы на языке команд микропроцессора

6. Составление и описание электрической принципиальной схемы устройства

7. Расчёт быстродействия устройства

8. Расчёт АЧХ и ФЧХ устройства для заданных и реальных значений коэффициентов. Оценка устойчивости устройства

9. Заключение

10. Список использованных источников

1. Постановка задачи (введение)

Цифровая обработка сигналов , т.е. обработка сигналов с помощью средств электронной вычислительной техники ,стала известна около 35 лет назад. Электронные вычислительные машины тогда были дороги и несовершенны и поэтому их применяли лишь в сложных радиокомплексах , например, при расчете координат и траекторий объектов в радионавигационных системах слежения за космическими объектами , при расчете координат цели в радиолокационных станциях.

В последующие годы благодаря широкому применению транзисторов а затем и развитию микроэлектроники ЭВМ стали совершеннее, дешевле, а главное, компактнее. Появилась возможность использования вычислительной техники в сравнительно простой аппаратуре, например, в специальных радиоприемниках, системах фазовой подстройки частоты, системах телеметрии и т.д. С помощью цифровых устройств можно реализовать очень сложные алгоритмы обработки сигналов, которые трудно, а часто даже невозможно реализовать, используя обычную аналоговую технику. Алгоритм обработки сигналов можно изменять в зависимости от характера входного сигнала. Следовательно, легко построить самонастраивающуюся (адаптивную) систему. Цифровые фильтры могут анализировать параметры сигнала и принимать те или иные решения , например, вырабатывать управляющие команды. С помощью цифровых методов можно реализовать любой алгоритм обработки сигнала , который может быть описан совокупностью арифметических и логических операций. Точность обработки сигнала цифровыми фильтрами определяется точностью выполняемых расчетов. Она может быть несоизмерима выше точности обработки сигнала в аналоговых фильтрах. Одним из источников погрешности аналоговых фильтров является нестабильность их параметров , вызываемая колебаниями температуры , старением , дрейфом нуля , изменением питающих напряжений и т.д. В цифровых фильтрах эти неприятные эффекты отсутствуют. При разработке цифровых фильтров не возникает задача согласования нагрузок. Недостатком цифровых фильтров является их большая сложность по сравнению с аналоговыми , более высокая стоимость и не очень высокое быстродействие. В последние годы в связи с появлением микропроцессоров цифровая обработка сигналов получила еще более широкое распространение. Для цифровых фильтров стало возможным построение разнообразных частотных характеристик , путем их аналитической задачи. При этом реализуемы и фильтры традиционных типов: нижних частот, верхних частот, полосовые и режекторные.

В данном курсовом проекте необходимо реализовать цифровой фазовый корректор, основой которого служит однокристальный микропроцессор К1821ВМ85 (ВМ85). Данный МП является усовершенствованной версией МП КР580ВМ80 (ВМ80). МП ВМ85 более экономичный (технология КМОП), использует только один источник питания (+5 В), имеет мультиплексированную шину адреса/данных, расширенные возможности обработки прерываний. На примере данного МП легко построить дешевые и компактные устройствам , в ряду которых фазовый корректор с требуемыми характеристиками.

Обработка должна происходить в реальном масштабе времени. При проектировании следует придерживаться двух критериев: минимальная аппаратная конфигурация устройства и минимальное время операций обработки сигнала (вычисления). При определенных условиях эти критерии противоречат друг другу.

2,.Формализация задачи

Минимальная конфигурация МП-системы на основе набора К1821 (К1821ВМ85, КР1821РФ55,КР1821РУ55 ) , совместно с ЦАП 572ПА1 и вспомогательными элементами определяет функциональную схему фазового корректора, которая представлена на рис.1.

Рис. 1. Функциональная схема проектируемого фильтра

Входное напряжение в виде кода

поступает в порт PA

БИС РУ55. Частота дискретизации

=8.0кГц

формируется аппаратным таймером РУ55 ,

в котором частота переполнения

=8.0кГц

формируется аппаратным таймером РУ55 ,

в котором частота переполнения

в режиме 3 , равна

в режиме 3 , равна

.

При использовании в качестве входных

импульсов таймера тактовых импульсов

CLK

МП - системы (

.

При использовании в качестве входных

импульсов таймера тактовых импульсов

CLK

МП - системы ( =1.5МГц)

исходное состояние таймера равно:

=1.5МГц)

исходное состояние таймера равно:

16-разрядный двоичный код содержит два бита (T15 и T14) задающих режим работы таймера. Для третьего режима работы необходимо в эти биты записать единицы.

Получаем код:

Байты

и

и

загружаются при инициализации системы

(фильтра).

загружаются при инициализации системы

(фильтра).

Необходимость хранения

данных вытекает из вида разностного

уравнения. Уравнение использует входную

выборку отсчетов ( )

и выходную (

)

и выходную ( ).

Все выборки должны быть доступны для

вычислений , а следовательно, должны

храниться в памяти МП - системы. Требуется

также вычислить четыре текущих

произведения (

).

Все выборки должны быть доступны для

вычислений , а следовательно, должны

храниться в памяти МП - системы. Требуется

также вычислить четыре текущих

произведения ( )

и сохранить их в памяти. После вычисления

выходного

)

и сохранить их в памяти. После вычисления

выходного

и записи в ОЗУ , перед приемом нового

входного отсчета , необходимо сдвинуть

отсчеты всех выборок в памяти , (n-1)

- й отсчет на место (n-2)-ого

, а n

-й на место (n-1)-ого.

В результате вычисления разностного

уравнения , можно получить результат ,

выходящий за пределы (-1,+1). Для исключения

переполнения разрядной сетки введем

масштабирование (ослабление) входных

отсчетов путем их умножения на коэффициент

масштабирования k>М>

1, при котором вычисление разностного

уравнения никогда не дает недопустимого

результата.

и записи в ОЗУ , перед приемом нового

входного отсчета , необходимо сдвинуть

отсчеты всех выборок в памяти , (n-1)

- й отсчет на место (n-2)-ого

, а n

-й на место (n-1)-ого.

В результате вычисления разностного

уравнения , можно получить результат ,

выходящий за пределы (-1,+1). Для исключения

переполнения разрядной сетки введем

масштабирование (ослабление) входных

отсчетов путем их умножения на коэффициент

масштабирования k>М>

1, при котором вычисление разностного

уравнения никогда не дает недопустимого

результата.

Реальные значения коэффициентов

разностного уравнения и коэффициента

отличается от заданных , вследствие

ограничения длины разрядной сетки:

отличается от заданных , вследствие

ограничения длины разрядной сетки:

По этой причине форма и параметры реальных частотных характеристик фильтра (АЧХ, ФЧХ) отличаются от расчетных. Могут также нарушаться условия устойчивости фильтра.

Алгоритм умножения на коэффициент (на константу без знака) целесообразно реализовать программным способом на основе алгоритма умножения вручную: арифметические сдвиги множимого вправо, соответствующие позициям единиц множителя, и накопление суммы частичных произведений. Разряды множимого, выходящие в результате сдвига за границу разрядной сетки, теряются.

Если затраты времени на вычисление произведений программным способом не допускают обработку сигнала в реальном времени, для вычисления произведений следует использовать БИС аппаратных перемножителей, которые вычисляют произведение за один машинный такт.

Согласование кода МП и кода ЦАП

необходимо , так как по заданию входной

код – дополнительный, Вычисленный

отсчет

, перед выводом на ЦАП суммируется с

константой

, перед выводом на ЦАП суммируется с

константой

.

.

Вывод данных на ЦАП целесообразно

осуществлять через порт PA

(РФ55) , этот порт имеет выходной буферный

регистр , в котором отсчет

хранится в течение всего интервала

дискретизации(ЦАП не имеет входного

буфера). Напряжение на выходе ЦАП на

интервале дискретизации остается

постоянным. Исходное состояние аппаратной

части и программы фильтра

устанавливается при включении питания

по сигналу аппаратного узла сброса. При

этом:

хранится в течение всего интервала

дискретизации(ЦАП не имеет входного

буфера). Напряжение на выходе ЦАП на

интервале дискретизации остается

постоянным. Исходное состояние аппаратной

части и программы фильтра

устанавливается при включении питания

по сигналу аппаратного узла сброса. При

этом:

программный счетчик (ВМ85) принимает нулевое значение;

сбрасывается флаг разрешения прерываний (ВМ85);

все линии портов PA и PB (РФ55) настраиваются на ввод;

порты PA , PB , PC (РУ55) настраиваются на ввод данных в режиме простого обмена данными;

таймер (РУ55) останавливается;

содержимое ячеек ОЗУ и буферных регистров портов (РУ55) сохраняется.

Из этого следует, что переходу фильтра в рабочий режим должна предшествовать его настройка (инициализация) на обеспечение принятого принципа функционирования, выбранных режимов работы узлов, заданных рабочих характеристик.

Для настройки портов ОЗУ (РУ55) нужно задать значение управляющего слова.

Формат управляющего слова:

Биты РА и РВ управляющего слова задают направление передачи данных через порты РА и РВ ( 0 – ввод, 1 – вывод).

Биты РС2 и РС1 определяют вариант использования порта С в соответствии с таблицей:

Здесь и ранее использованы следующие обозначения:

INTR A (B) – запрос прерывания по порту РА (РВ); BF A (B) – буфер порта РА (РВ) полон ( занят); STB A (B) – управляющий сигнал записи, соответствующий порту РА (РВ).

Биты IEA, IEB управляющего слова разрешают (IE = 1) или запрещают выработку сигналов прерывания INTR.

Биты ТМ2, ТМ1 содержат код (ТМ2 ТМ1) команды управления таймером. Описание команд приведено в таблице.

Я выбрал следующее значение управляющего слова:

Таким образом я настроил ОЗУ (РУ55) следующим образом:

Таймер настроен на 3 – ий режим

работы (ТМ1 = 1; ТМ2 = 1); Линии порта С

используются в соответствии с выше

приведённой таблицей при РС2 = 0 и РС1 =

0; Порт В настроен на вывод данных ( РВ =

1); Порт А настроен на вывод данных по

сигналу готовности и квитирования ( РА

= 1). При настройке режимов прерывания

необходимо разрешить прерывание МП

типа RST

6,5 по вводу

>

>По команде SIM

обеспечивается установка нового

состояния маски в соответствии с

содержимым аккумулятора:

>

>По команде SIM

обеспечивается установка нового

состояния маски в соответствии с

содержимым аккумулятора:

-

A7

A6

A5

A4

A3

A2

A1

A0

SOD

SDEN

-

R 7,5

MSEN

M 7,5

M 6,5

M 5,5

А0 – А2 – соответственно маски RST 5.5, RST 6.5, RST 7.5;

А3 – разрешение установки маски; А4 – сброс триггера приема запроса RST 7.5; А5 – не используется; А6 – разрешение вывода данных; А7 – бит данных для вывода через SOD.

Установка маски запрещает соответствующее прерывание. Смена маски в соответствии с А0 – А2 выполняется только при разрешении ее установки (А3 = 1). В противном случае функция установки маски подавляется. Для маски прерывания RST 6.5 содержимое аккумулятора будет следующим ( Dh ):

A7 = 0; A6 = 0; A5 = 0; A4 = 0; A3 = 1; A2 = 1; A1 = 0; A0 = 1.

3. Разработка и описание общего алгоритма функционирования устройства

Общий алгоритм функционирования фильтра строится на основе выводов и определений, сделанных при анализе задачи, и включает в себя все функции устройства, реализуемые аппаратно и реализуемые программно. Он содержит также все сигналы и сообщения, необходимые для взаимосвязи аппаратно-реализуемых и программно-реализуемых операций (сигналы и сообщения, которые обеспечивают взаимодействие аппаратной части фильтра и программы).

Общий алгоритм функционирования фильтра приведен на рис.2

При подаче питания , схема сброса формирует импульсы сброса , который обнуляет счетчик команд МП и инициирует формирование импульса сброса RESET для установки МП - системы в исходное состояние. Запускается программа инициализации МП – системы, которая должна начинаться с нулевого адреса. При инициализации:

в указатель стека SP записывается начальный адрес , с которого начинается стек;

порт PA (РФ55) настраивается на ввод данных ; в регистр направления передачи записывается управляющее слово;

таймер настраивается на период

переполнения , равным

в режиме 3;

в режиме 3;

порт PA (РУ55) настраивается на ввод ;

пуск таймера;

настройка режима прерывания.

Программа инициализации завершается остановом МП. Из состояния останова МП выводится сигналом INTRA , поступающим на вход RST 7.5 МП. Последующие операции выполняются под управлением рабочей программы фильтра. Выполнение рабочей программы - это реакция на прерывание, поэтому после обслуживания прерываний по команде возврата из подпрограммы МП возвращается в состояние останова.

Рис. 2. Общий алгоритм функционирования фильтра

4. Обоснование аппаратной части устройства

Основой аппаратной части устройства является многопроцессорный набор К1821 , в состав которого входят три микросхемы:

К1821ВМ85 – микропроцессор;

КР1821РФ55 – ПЗУ с двумя портами ввода/вывода , работающими в режиме простого обмена;

КР1821РУ55 – ОЗУ, таймер и два направленных порта ввода/вывода. Выходной сигнал должен иметь аналоговый вид, для преобразования цифрового кода в аналоговый сигнал , используя ЦАП типа К572ПА1.

Микросхема ЦАП К572ПА1 преобразует 10 – разрядный входной параллельный двоичный код в ток на аналоговом выходе, пропорциональный значениям кода и опорного напряжения.

Для преобразования кода в ток используют внешний источник опорного напряжения и матрица резисторов R – 2R.

В устройство РФ55 входит ПЗУ емкостью 2К х 8 бит и два 8-разрядных порта ввода – вывода. Каждая линия обоих портов может программироваться индивидуально и определяться как входная или выходная. Порты могут работать только в режиме простого обмена без каких-либо сопровождающих сигналов, причем выводимый байт запоминается в буферном регистре порта, а вводимый – не запоминается.

В устройство РУ55 входит статическое ОЗУ емкостью 258 х 8 бит, два 8-разрядных (А и В) и один 6-разрядный (С) порты ввода-вывода и 14-разрядный программируемый счетчик/таймер. Все разряды портов А и В используются для ввода-вывода параллельно, т.е. невозможна установка направления передачи индивидуально для каждого разряда. Порты А и В содержат буферные регистры для запоминания пересылаемого байта данных.

Для преобразования выходного тока в выходное напряжение, пропорциональное значению входного кода, требуются внешние операционные усилители (ОУ) с цепью отрицательной обратной связи.

5. Разработка и отладка программы на языке команд микропроцессора

Рабочая программа разработана на основе спроектированного алгоритма функционирования устройства и результатов анализа и формализации задачи. Программа привязана к минимальной конфигурации аппаратной части фильтра.

Распределение памяти ПЗУ:

0000h….003Bh – программа инициализации;

003Ch….07FFh – программа реакции на прерывание RST 6.5.

Распределение памяти ОЗУ:

5000h, 5001h, 5002h – хранение отсчетов x> >>n>> >, x >n>> – 1>, x >n>> – 2>;

5003h, 5004h, 5005h – хранение отсчетов y> >>n>> >, y >n>> – 1>, y >n>> – 2>;

5006h, 5007h, 5008h, 5009h – хранение произведений p> 1>>n>> >, p >2>>n>, p> 3>>n>> >, p> 4>>n>> >;

50FFh – начальный адрес стека.

;Программа "Фазовый корректор"

;Автор: студент гр.114 Тришин Сергей Викторович

;Дата: 10 апреля 2004 г.

;Разностное уравнение: y>n>> >= 0,988 x>n> – 1,6 x>n>> – 1> + x>n>> – 2> + 1,6 y>n>> – 1> –0,988 y>n>> – 2>;

;Определение символических имен

;Инициализация по сигналу "Сброс"

Листинг программного модуля вычисления выходного отсчета

С целью проверки на переполнение осуществлен ручной и машинный просчет программы. В качестве исходного случая взят случай, когда все отсчеты имеют максимальное значение.

X>n>> >= 1>(10)>= 0,1111111>(2) >= 7F>(16)>;

X>n>>-1 >= –1>(10)>= 1,0000000>(2) >= 80>(16)>;

X>n>>-2 >= 1>(10)>= 0,1111111>(2) >= 7F>(16)>;

Y>n>>-1 >= 1>(10)>= 0,1111111>(2) >= 7F>(16)>;

Y>n>>-2 >= –1>(10)>= 1,0000000>(2) >= 80>(16)>;

k>М >= 0,1619>(10)> 0,0010100>(2) >= 0,15625;

x>n>=X>n>k>М>=0,9921875*0,15625> >= 0,155029296>(10)>0,0010011>(2) >= 13>(16)>;

x>n>>-1>=X>n>>-1>k>М>=–1*0,15625=–0,15625> (10)>1,1101100>(2)>= EC>(16)>;

x>n>>-2>=X>n>>-2>k>М>=0,9921875*0,15625> >= 0,155029296>(10)>0,0010011>(2) >= 13>(16)>;

y>n>>-1>=Y>n>>-1>k>М>=0,9921875*0,15625> >= 0,155029296>(10)>0,0010011>(2) >= 13>(16)>;

y>n>>-2>=Y>n>>-2>k>М>=–1*0,15625=–0,15625> (10)>1,1101100>(2)>= EC>(16)>;

Разностное уравнение имеет вид: y>n>> >= p>n>>1 >+ p>n>>2>+ x>n>>-2> + p>n>>3>+ p>n>>4 , >где с учётом погрешности

p>n>>1>=0,984375*x>n>, p>n>>2>=1,59765625*x>n>>-1>,

p>n>>3>=1,59765625*y>n>>-1>, p>n>>4>=0,984375*y>n>>-2>.

p>n1>=0, 984375*0,1484375=0,146118164> (10)> 0,0010010>(2)> = 12>(16)>;

p>n2>= p>n2>=1,59765625*(–0,15625) > >=–0,24963379>(10)> 0,0011111>(2)> = 1F>(16)>;

p>n3>=1,59765625*0,1484375=0,237152099>(10)> 0,0011110>(2)> = 1E>(16)>;

p>n>>4>= p>n>>4>=0, 984375*(–0,15625) > >=–0,153808593>(10)> 0,0010011>(2)> = 13>(16)>;

y>n>> >=12> (16)>+ 1F> (16)>+ 1E> (16)>+ 13> (16)>=62>(16)>.

Таким образом при ручном просчёте переполнения не произошло.

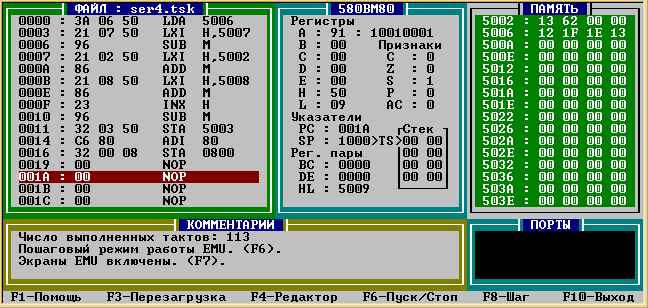

Машинный просчёт программного модуля вычисления выходного отсчета представлен на рисунке :

Результат машинного просчёта совпадает с результатом ручного просчёта. Таким образом в процессе выполнения программы переполнения не происходит.

6. Составление и описание электрической принципиальной схемы устройства

Электрическая принципиальная схема цифрового фазового корректора содержит следующие микросхемы:

DD1 – МП К1821ВМ85

DD2 – ПЗУ КР1821РФ55

DD3 – ОЗУ КР1821РУ55

DA1 – ЦАП К572ПА1

DA2 – ОУ К154УД3

DA3 – ОУ К154УД3

Опишем назначение выводов микросхем.

К1821ВМ85 :

1 – вход линии подключения кварцевого генератора ;

2 – выход линии подключения кварцевого генератора ;

3 – выход сброса системы ;

4 – выход линии последовательной передачи данных ;

5 – вход линии последовательной передачи данных ;

6 – вход немаскируемого прерывания с фиксированным вектором типа RST n (n = 4.5) высшего приоритета ;

7 – 9 – входы запроса маскируемогопрерывания с фиксированным вектором типа RST n (n = 5.5 , 6.5 , 7.5) ;

10 – вход запроса векторного маскируемого прерывания ;

11 – выход подтверждения прерывания ;

12 – 19 – мультиплексная шина адреса / данных ;

20 – общий ;

21 – 28 – выходы адресной шины ;

29 , 33 , 34 – выходы типа машинного цикла ;

30 – выход разрешения фиксации адреса: сигнал появляется в течение такта каждого машинного цикла и разрешает запись адреса во внешний регистр адреса ;

31 – выход управления записью ;

32 – выход управления чтением ;

35 – вход готовности пересылать или получать информацию ;

36 – вход приёма сигнала сброса МП в начальное положение ;

37 – выход импульсов синхронизации ;

38 – выход подтверждения захвата шин адреса и данных ;

39 – вход запроса захвата адресной шины и шины данных внешним модулем ;

40 – питание (5В) .

КР1821РФ55 :

1 , 2 – вход выбора кристалла ;

3 – вход синхронизации ;

4 – вход сброса ( все линии обоих портов настраиваются на ввод ) ;

6 – выход запроса состсяния ожидания МП ;

7 – вход выбора портов или памяти ;

8 – вход управления чтением из портов (А или В) ;

9 - вход управления чтением из ПЗУ ;

10 – вход управления записью в портоы (А или В) ;

11 - вход разрешения фиксации адреса, поступающего по шине AD0 – AD7(выводы 12 – 19) во внутренний регистр адреса.

12 – 19 – мультиплексная шина адреса / данных ;

20 – общий ;

21 – 23 – вход адреса (три старших разряда) ;

24 – 31 - двунаправленная шина данных порта А ;

32 – 39 - двунаправленная шина данных порта В ;

40 – питание (5В) .

КР1821РУ55 :

1 , 2 , 5 , 37 – 39 – двунаправленная шина данных порта С ;

6 – выход счётчика таймера ;

7 – вход выбора порта или памяти ;

8 – вход выбора кристалла ;

9 – вход управления чтением данных из БИС ;

10 – вход управления чтением данных из БИС ;

11 – вход разрешения фиксации адреса, поступающего по шине AD0 – AD7(выводы 12 – 19) во внутренний регистр адреса.

12 – 19 – мультиплексная шина адреса / данных ;

20 – общий ;

21 – 28 – двунаправленная шина данных порта А ;

29 – 36 – двунаправленная шина данных порта В ;

40 – питание (5В) .

К572ПА1 :

1 – аналоговый выход 1;

2 – аналоговый выход 2;

3 – общий вывод;

4-13 – цифровые входы (4 – старший разряд, 13 – младший разряд);

14 – напряжение источника питания;

15 – опорное напряжение;

16 – вывод резистора обратной связи.

К микропроцессору подключается кварцевый резонатор для обеспечения работы внутреннего генератора тактовых импульсов CLK.

Схема формирования импульса сброса на микропроцессоре состоит из RC – цепи и диода KD522, так же возможно принудительное формирование импульса сброса при замыкании переключателя.

Передача сигналов микросхем DD1, DD2, DD3 осуществляется по мультиплексированной шине адреса/данных (AD0 – AD7). Микросхема K1821РУ55 соединена с ЦАП портом PВ (PВ0 – PВ7).

Для синхронизации передачи данных микросхемы DD1, DD2, DD3 соединены по тактовым входам CLK.

7. Расчёт быстродействия устройства

Быстродействие фильтра в рабочем режиме оценивается как время, необходимое для обработки прерывания микропроцессора. Рабочая программа фильтра линейная, поэтому общее число машинных тактов, требуемых для выполнения программы, получили как сумму машинных тактов всех последовательно выполняемых команд, составляющих рабочий цикл процессора.

Сумма машинных тактов рабочего

цикла программы равна 895.

При частоте процессора

и

и

процессор не успевает выполнить

подпрограмму обслуживания прерывания,

так как

процессор не успевает выполнить

подпрограмму обслуживания прерывания,

так как

,

то есть интервал дискретизации

,

то есть интервал дискретизации

равен

187 машинным тактам. Необходимо увеличить

тактовую частоту микропроцессора до

равен

187 машинным тактам. Необходимо увеличить

тактовую частоту микропроцессора до и

скорректировать слово загрузки в таймер:

и

скорректировать слово загрузки в таймер:

получим управляющее слово таймера:

Необходимо провести коррекцию в программе, заменив эти константы.

8. Расчет АЧХ и ФЧХ устройства для заданных и реальных значений коэффициентов. Оценка устойчивости устройства

Разностное уравнение проектируемого фильтра в общем виде можно представить следующим образом:

y>n> = b> 0 >x> n> + b> 1>x >n – 1> + b> 2>x >n – 2> – a> 1> y >n – 1> – a> 2 >y >n – 2>

Коэффициенты b>i> , a>i> определяют характеристики фильтра.

Значения коэффициентов: b> 0> = 0.988;b> 1> = -1,6;b> 2> = 1; a> 1> = -1.6;a> 2> = 0.988

Разностное уравнение задает во временной области порядок получения выходной последовательности отсчетов из входной. Приведенное уравнение соответствует однокаскадному цифровому фильтру: каскад вычисляет выходную последовательность y>n> .

В z-плоскости свойства цифрового фильтра описывает передаточная функция H(z), которая при однокаскадной структуре и для приведенного выше разностного уравнения имеет вид:

При z

= e

jT

= e

j2fT,

где Т = Т>Д >=

1/F>Д>

( F>Д

>= 8кГц ) сигнал на входе

фильтра – синусоида с частотой f

и с единичной амплитудой, а функция H(e

j2fT)

равна частотной характеристике фильтра,

из которой можно получить АЧХ и ФЧХ.

Значения коэффициентов разностного

уравнения определяют форму и параметры

частотных характеристик, поэтому для

выявления влияния их приближенного

представления следует рассчитать АЧХ

и ФЧХ при заданных (точных) и реальных

(приближенных) значениях коэффициентов.

Расчёт заданной

и реальной

и реальной

ФЧХ по формулам :

ФЧХ по формулам :

= arg(H>Т>(e

j2fT))

и

= arg(H>Т>(e

j2fT))

и

= arg(H>Р>(e

j2fT))

= arg(H>Р>(e

j2fT))

Расчёт заданной

и реальной

и реальной

АЧХ по формулам :

АЧХ по формулам :

,

,

Для проектируемого фазового корректора :

Результаты расчета заданной

и реальной

и реальной

АЧХ приведены на следующих графиках.

АЧХ приведены на следующих графиках.

Результаты расчета заданной

и реальной

и реальной

ФЧХ приведены на следующих графиках.

ФЧХ приведены на следующих графиках.

9. Заключение

В данном курсовом проекте было разработано МП–устройство. Также составлена программа, которая и обеспечивает работу этого устройства как всепропускающее фазовое звено. Аппаратная часть по возможности была минимизирована, а программа оптимизирована, что обеспечивает работу устройства в реальном масштабе времени. Основой данного устройства являются набор К1821 и ЦАП К572ПА1, что соответствует заданию.

10. Список использованных источников

1. Рафикузаман М. Микропроцессоры и машинное проектирование микропроцессорных систем: В 2-х кн. Пер. С англ. - М.: Мир, 1988.

2. Калабеков Б.А. Микропроцессоры и их применение в системах передачи и обработки сигналов: Учеб. пособие для вузов. – М.: Радио и связь, 1988.

3. Проектирование импульсных и цифровых устройств радиотехнических систем: Учеб. Пособие для радиотехнич. спец. вузов/Гришин Ю.П., Катаков В.М. и др.; Под ред. Ю.М. Казаринова . – М.: Высш. шк., 1985.

4. Микропроцессоры: системы программирования и отладки / В.А. Мясников, М.Б. Игнатьев, А.А. Кочкин, Ю.Е. Шейнин; Под ред. В.А. Мясникова, М.Б. Игнатьева. – М.: Энергоатомиздат, 1985.

5. Р. Токхайм. Микропроцессоры. Курс и упражнения. Пер. с англ. В.Н Грасевиче и Л.А. Ильяшенко. М.: Энергоатомиздат, 1988.

6. Щелкунов Н.Н., Дианов А.П. Микропроцессорные средства и системы .- М.: Радио и связь,1989.

7. Федорков Б.Г., Телец В.А. Микросхемы ЦАП и АЦП: функционирование, параметры, применение.- М.: Энергоатомиздат , 1990.

8. Лебедев О.Н. Микросхемы памяти и их применение. - М.: Радио и связь, 1990.

9. Микропроцессорные комплекты интегральных схем: состав и структура. Справочник / Под ред. А.А. Васенкова, В.А. Шахнова. - М.: Радио и связь, 1982