Методические указания по микропроцессорным системам

Министерство образования Российской Федерации

Г осударственное

образовательное учреждение

осударственное

образовательное учреждение

высшего профессионального образования

Таганрогский государственный радиотехнический университет

В.Ф. Гузик, А. Н. Гармаш, Г.Н. Евтеев

Микропроцессорные системы

Учебное пособие

Таганрог 2003

УДК 681.3(07.07)

Гузик В.Ф., Гармаш А.Н., Евтеев Г.Н. Микропроцессорные системы: Учебное пособие. Таганрог: Изд-во ТРТУ, 2003. 71 с.

Является обобщением опыта преподавания кафедрой вычислительной техники курса «Микропроцессорные системы» студентам специальности 220100 «Вычислительные машины, комплексы, системы и сети», обучающимся по дистанционной технологии.

Излагаются: архитектура микроЭВМ и микропроцессорных систем, организация и особенности проектирования микропроцес-сорных систем на основе однокристальных микроЭВМ, рассматриваются архитектура мультимикропроцессорных и транспьютерных систем, средства разработки и отладки микропроцессорных систем.

Предназначено для студентов специальности 220100 «Вычислительные машины, комплексы, системы и сети» заочной формы обучения. Может быть полезно студентам всех форм обучения по специальности «Вычислительные машины, комплексы, системы и сети», а также студентам всех специальностей направления «Информатика и вычислительная техника».

Печатается по решению редакционно-издательского совета Таганрогского государственного радиотехнического университета.

Рецензенты:

Конструкторское бюро морской электроники «Вектор», А.Н. Долгов, канд. техн. наук, директор.

ТФ ОАО “НИИ системотехники”, А.И. Гречишников, канд. техн. наук, директор.

©Таганрогский государственный радиотехнический университет, 2003

Содержание

стр.

Список сокращений 4

ВВЕДЕНИЕ 6

1. ОСНОВНЫЕ ХАРАКТЕРИСТИКИ, ОБЛАСТИ ПРИМЕНЕНИЯ И ОСОБЕННОСТИ РАБОТЫ МИКРОПРОЦЕССОРНЫХ СРЕДСТВ 8

Упражнения 23

Контрольные вопросы 24

2. АРХИТЕКТУРА МИКРОЭВМ И МИКРОПРОЦЕССОРНЫХ СИСТЕМ 24

Контрольные вопросы 29

3. ЭТАПЫ ПРОЕКТИРОВАНИЯ МИКРОПРОЦЕССОРНЫХ СИСТЕМ 30

Контрольные вопросы 35

4. ОРГАНИЗАЦИЯ И ОСОБЕННОСТИ ПРОЕКТИРОВАНИЯ МПС НА ОСНОВЕ ОДНОКРИСТАЛЬНЫХ МИКРОЭВМ 35

4.1. Общие принципы организации однокристальных микроЭВМ 35

4.2. Особенности проектирования МПC на основе однокристальных микроЭВМ и контроллеров. 40

4.3. Обзор перспективных проектов МПС на основе однокристальных комплектов БИС 44

Контрольные вопросы 51

5. МУЛЬТИМИКРОПРОЦЕССОРНЫЕ СИСТЕМЫ 51

5.1. Обзор развития ММПС и их архитектур 51

5.2. Основные перспективные проекты высокопроизводительных ММПС 59

Контрольные вопросы 65

6. ТРАНСПЬЮТЕРНЫЕ СИСТЕМЫ 65

Контрольные вопросы 69

7. СРЕДСТВА РАЗРАБОТКИ И ОТЛАДКИ МПС 70

7.1. Автономная и комплексная отладка МПС 70

7.2. Средства отладки МПС 72

Контрольные вопросы 78

Библиографический список 79

Список сокращений

АЛУ – арифметико-логическое устройство

АЦП – аналого-цифровой преобразователь

БА – буфер адреса

БД – буфер данных

БИС – большая интегральная схема

БПр – бенчмарковская программа

БПФ – быстрое преобразование Фурье

БР – буферный регистр

ВЗУ – внешнее запоминающее устройство

ВСЭ – внутрисхемный эмулятор

ЗУ – запоминающее устройство

ЗУПВ – запоминающее устройство с произвольной выборкой

И2Л – инжекционная логика (технология изготовления БИС)

ИС – интегральная схема

КПД – канал прямого доступа

КСНК – компьютер с сокращенным набором команд

ЛА – логический анализатор

МА – магистраль адреса

МД – магистраль данных

МК – микрокоманда

МКМД – Много потоков Команд – Много потоков Данных

МКОД – Много потоков Команд – Один поток Данных

МОП – металл – окисел – проводник (технология изготовления БИС)

ММПС – мультимикропроцессорная система

МП – микропроцессор

МПК – микропроцессорный комплект

МПС – микропроцессорная система

МУ – магистраль управления

ОКОД – Один поток Команд – Один поток Данных

ОКМД – Один поток Команд – Много потоков Данных

ПДП – прямой доступ к памяти

ПО – программное обеспечение

ППЗУ – программируемое ПЗУ

ПС – программный счетчик

РК – регистр команд

РР – регистр результата

РОН – регистр общего назначения

СБИС – сверхбольшая интегральная схема

ТТЛШ – транзисторно-транзисторная логика с диодами Шотки (технология изготовления БИС)

УВВ – устройство ввода-вывода

УУ – устройство управления

ЦАП – цифроаналоговый преобразователь

ЦОС – цифровая обработка сигналов

ЦП – центральный процессор

ЦПУ – центральное процессорное устройство

ЭЛС – эммитерно-связанная логика (технология изготовления БИС)

ЭМП – эмулятор микропроцессора

ВВЕДЕНИЕ

Появление и бурное развитие микропроцессоров (МП), микроЭВМ и систем на их основе стало возможным благодаря значительным достижениям микроэлектронной технологии изготовления средств ВТ. Успехи полупроводниковой электроники привели к появлению больших и сверхбольших интегральных схем (БИС и СБИС) с плотностью размещения компонентов от десятков до сотен тысяч транзисторов на кристалле. Использование этих схем позволяет значительно повысить эффективность цифровых систем: увеличить их производительность и надежность, уменьшить габариты, массу, потребляемую мощность и стоимость. Так, за два последних десятилетия скорость работы ЭВМ возросла на 6-7 порядков, объем оперативной памяти увеличился на 5-6 порядков.

Еще более динамичным является развитие микропроцессорных систем. Первое поколение микропроцессорных комплектов БИС представляло набор модулей с жесткой структурой, ориентированных на применение в конкретных системах с большим объемом выпуска. Последующие комплекты благодаря использованию принципов микропрограммирования нашли широкие области применения ввиду появившейся возможности проблемной ориентации. Высокими темпами развивается интегральная технология. Степень интеграции БИС удваивается ежегодно, стоимость вентиля – элементарного функционального элемента БИС – уменьшается каждые 10 лет в 103 - 104 раз, стоимость выполнения элементарной функции ежегодно снижается в 2 раза.

МП, микроЭВМ и системы на их основе имеют два направления применения:

- традиционное для средств ВТ;

- нетрадиционное (вместо устройств с жесткой структурой), в котором до появления МП использование средств ВТ и не предполагалось.

Говоря о месте и роли МП и микроЭВМ в иерархии средств ВТ, необходимо иметь в виду оба эти направления.

Значительные успехи в микропроцессорной технике привели к появлению и развитию на рубеже 70-80-х годов ХХ столетия весьма перспективных и обладающих большим быстродействием по сравнению с традиционными ЭВМ мультимикропроцессорных систем (ММПС), которые весьма значительно повлияли на развитие современной науки и техники.

Благодаря сверхвысокой производительности ММПС стало возможным достижение больших успехов в решении таких важных научных и технических задач, как нейрокомпьютинг и робототехника, стенография и теория полей, радио- и гидролокация, распознавания образов, геофизика, цифровая обработка сигналов и многие другие.

С другой стороны, развитие микропроцессорных средств влияет на достижения в области теории проектирования вычислительной техники: появляются все более перспективные архитектуры МПС и их компонентов (RISK – процессоры, транспьютеры, сигнальные процессоры и т.п.).

Неоценимое значение современные МПС имеют в теории и практике проектирования локальных и глобальных вычислительных сетей, расширяя тем самым области эффективного применения современных средств ВТ.

Множество областей применения МП и микроЭВМ позволяет классифицировать МПС на системном уровне следующим образом:

- встроенные системы контроля и управления;

- локальные системы накопления и обработки информации;

- распределенные системы управления сложными объектами;

- распределенные высокопроизводительные системы параллельных вычислений.

Исходя из этого, в настоящее время определились следующие приоритетные области применения МПС:

- системы управления;

- контрольно-измерительная аппаратура;

- техника связи;

- бытовая и торговая аппаратура;

- транспорт;

- военная техника;

- вычислительные машины, системы, комплексы и сети.

Перспективность применения МПС в различных системах управления обусловлена, в первую очередь, такими достоинствами МП, как малые габариты, низкая потребляемая мощность, возможность подключения большого количества процессоров к каналам управления, простота программной настройки и перестройки.

Внедрение МПС в контрольно-измерительную аппаратуру позволяет повысить точность измерений, надежность, расширить функциональные возможности приборов и обеспечивает выполнение следующих функций: калибровка, коррекция и температурная компенсация, контроль и управление измерительным комплексом, принятие решений и обработка данных, диагностика неисправностей, индикация, испытание и проверка приборов.

Внедрение МПС в системы связи обусловлено все большим вытеснением аналоговых методов цифровыми и привело к их широкому использованию в мультиплексорах, преобразователях кодов, устройствах контроля ошибок, блоках управления передающей и приемной аппаратуры.

Все шире используются МПС в таких устройствах, как контрольно-расчетные терминалы торговых центров, автоматизированные электронные весы, терминалы и кассовые аппараты для банков и т.п. Применение МП и МПС в бытовой технике открывает также широкие возможности последней с точки зрения повышения надежности, эффективности и разнообразия применений.

Доля применения МПС в различных областях военной техники растет с каждым годом от навигационных систем летательных аппаратов до управления движением транспортных роботов.

Если определить все множество применений МПС в процентном отношении, то это будет выглядеть следующим образом: информационно-измерительная техника 16% , управление производством 18%, авиация и космос 15%, системы связи 14 %, вычислительная техника 20%, военная техника 9%, бытовая техника 3%, медицина 3%, транспорт 2%, другие области 7 %.

1. ОСНОВНЫЕ ХАРАКТЕРИСТИКИ, ОБЛАСТИ ПРИМЕНЕНИЯ И ОСОБЕННОСТИ РАБОТЫ МИКРОПРОЦЕССОРНЫХ СРЕДСТВ

Микропроцессорной системой (МПС) называется система цифровой обработки информации и управления, содержащая в своем составе, по крайней мере, один микропроцессор (МП), один или несколько модулей основной (ОЗУ и ПЗУ) и дополнительной памяти, устройства ввода и вывода, блоки сопряжения (контроллеры) с устройствами ввода и вывода, которые связаны друг с другом с помощью системной магистрали, состоящей, в общем случае, из магистралей (шин) адресов (МА, ША), магистралей (шин) данных (МД, ШД) и магистралей (шин) управления (МУ, ШУ).

Логическая структура МПС приведена на рис.1.1, где ОУ – объект управления, Д – датчики, ИМ – исполнительные механизмы, ИК – информационные контроллеры, БСД – блок сопряжения с датчиками, БСИК – блок сопряжения с информационными контроллерами, ОП – основная память, ДП – дополнительная память.

Рис. 1.1. Логическая структура МПС

ОЗУ МПС обеспечивает чтение и запись информации и реализуется как энергозависимая память, содержимое которой стирается при выключении МПС. ПЗУ обеспечивает только чтение информации и реализуется в виде энергонезависимой памяти. Контроллеры представляют собой устройства сопряжения аппаратуры ввода-вывода с системной магистралью и реализуют определенный интерфейс. Магистраль обеспечивает коммуникацию аппаратных средств МПС и представляет собой набор проводников и усилителей сигналов.

В зависимости от областей применения МПС подразделяются на специализированные и универсальные, встроенные и автономные.

Основой любой МПС является микроЭВМ вычислительная или управляющая система, выполненная на основе МП, в состав которой, как правило, входят: постоянная (программируемая) память программ (ПЗУ), память данных (ОЗУ), генератор тактовых импульсов и информационный контроллер, построенные на основе БИС или СБИС.

По способу реализации микроЭВМ подразделяются на однокристальные, одноплатные и многоплатные. В одноплатных микроЭВМ МП выполняется в виде кристалла БИС (СБИС), на котором кроме самого МП могут располагаться и другие компоненты микроЭВМ (ПЗУ, ОЗУ, контроллеры и т.п.).

По назначению микроЭВМ разделяются на универсальные и специализированные (проблемно-ориентированные).

По организации структуры различают одно- и многомагистральные микроЭВМ (рис. 1.2).

Рис.

1.2. Общая структура ЭВМ: а – одномагистральная;

Рис.

1.2. Общая структура ЭВМ: а – одномагистральная;

б – многомагистральная

В одномагистральных микроЭВМ все устройства имеют одинаковый интерфейс и подключены к единой информационной магистрали, по которой передаются данные, адреса и управляющие сигналы. В многомагистральных микроЭВМ устройства группами подключаются к своей информационной магистрали, что позволяет осуществить одновременную передачу по нескольким (или всем) магистралям и тем самым увеличить быстродействие системы.

Центральной частью МПС является микропроцессор обрабатывающее устройство, выполненное с использованием технологии БИС (часто на одном кристалле) и обладающее способностью выполнять под программным управлением обработку информации (включая ввод-вывод), принятие решений, арифметические и логические операции.

МП характеризуется очень большим числом параметров и качеств, поскольку он, с одной стороны, является функционально сложным программно-управлемым цифровым процессором, т.е. устройством ЭВМ, а с другой стороны – интегральной схемой с высокой степенью интеграции элементов, т.е. электронным прибором.

МП классифицируются по следующим признакам.

По числу БИС в микропроцессорном комплекте однокристальные и многокристальные МП. Однокристальные МП получаются при реализации всех аппаратурных средств процессора в виде одной БИС или СБИС. Для получения многокристального МП необходимо произвести разбиение его логической структуры на функционально законченные части и реализовать их в виде БИС.

По назначению различают универсальные и специализированные МП. По виду обрабатывающих входных сигналов МП делят на цифровые и аналоговые. По характеру временной организации работы синхронные и асинхронные.

Кроме этого МП, как правило, классифицируются: по технологии изготовления (p-МОП, п-МОП, к-МОП, И2Л и т.д); по числу шин; по разрядности; по способу управления (схемное, микропрограммное); по числу аккумуляторов, уровней прерывания и программных счетчиков; по типу и емкости стека; по числу и длине команд и по видам адресации.

В общем случае в состав МП входят (рис. 1.3): арифметико-логическое устройство (АЛУ), блок прерываний (БП), дешифратор команд и схема управления (ДСК и СУ), регистр команд (РК), буферы адреса и данных (БА, БД), регистры общего назначения (РОН), индексный регистр (ИР), стек (С), его указатель (УС), программный счетчик (ПС), регистр-аккумулятор (А), регистр признаков (РП), схема инкремент-декремент (ИД), блок прерываний (БП).

Конкретные МП, как правило, не содержат всех узлов и блоков, показанных на рис. 1.3. В этих случаях соответствующие функции могут выполняться программно, а в качестве некоторых специальных регистров

Рис. 1.3. Логическая структура МП

могут использоваться РОН или ячейки памяти. В ряде микропроцессорных комплектов отдельные функциональные узлы и блоки выполняются автономно в виде БИС или схем средней степени интеграции.

При проектировании МПС следует учитывать, что их производительность и функциональные возможности напрямую зависят от организации внутренних шин МП их число существенно влияет на структуру и характеристики МПС в целом.

При определении оптимального числа шин следует учитывать, что уменьшение числа шин приводит к уменьшению быстродействия МП и сопровождается введением дополнительных буферных регистров, увеличивает площадь на кристалле, отводимую под функциональные элементы, и тем самым увеличивает функциональные возможности МП и МПС.

В трехшинном МП при определенной внутренней организации РОН возможно выполнение операций за один такт, включая выборку операндов из РОН и запись результата в один из регистров. Достоинства: высокое быстродействие и отсутствие буферных регистров, недостаток большая площадь шин на кристалле.

Двухшинная организация при меньшей площади шин требует введения одного-двух буферных регистров и операции выполняются за два такта.

Организация МП на основе одной шины позволяет максимально усложнить архитектуру МП, однако требует введения двух-трех буферных регистров и трех тактов для выполнения операций.

При использовании магистральной организации МПС возникает сложность в подключении выходов нескольких элементов к одной шине (к одному проводнику общей шины). Известны три следующих способа решения этой задачи.

Логическое объединение (рис. 1.4, а) выполняется с помощью схемы ИЛИ, на входы которой поступают сигналы от разных источников информации, предварительно проклапанированные сигналами управления на входах схем И.

Рис. 1.4. Способы подключения устройств к общей шине

Объединение с помощью схем с открытым коллектором (рис. 1.4, б) характеризуется электрическим соединением выходов нескольких логических элементов. Часто этот способ называют «монтажным ИЛИ» или «монтажным И».

Объединение с использованием схем с тремя состояниями (рис. 1.4, в) отличается именно таким характером нагрузки. В отличие от обычных ключевых схем здесь возможен третий режим, при котором оба транзистора одного каскада (VT1 и VT2 или VT3 и VT4) закрыты. В этом случае со стороны выхода каскад обладает высоким сопротивлением и практически не влияет на состояние общей шины. Если в состоянии высокого сопротивления будут находиться оба каскада, то общая шина может использоваться произвольно любыми внешними по отношению к МП устройствами. Этот способ широко используется при организации прямого доступа к памяти и при построении мультипроцессорных систем.

Кроме широко известных устройств внешней (ЗУ команд и ЗУ данных) и внутренней (РОН) памятей, для которых характерен адресный принцип общения, в МП МПС обычно предусматривается возможность работы с так называемой магазинной памятью (стеком), при обращении к которой не требуется указание адреса. Возможная организация магазинной памяти представлена на рис. 1.5.

Рис. 1.5. Организация стека

Выборка одной из ячеек матрицы памяти осуществляется через дешифратор адреса (ДСА) по адресу, находящемуся на реверсивном счетчике адреса, называемом указателем стека (УС). Начальное значение адреса поступает в УС на вход А. В процессе работы состояние УС при каждой записи уменьшается, а при каждом чтении увеличивается на единицу. Управление режимами записи и чтения выполняет местный блок управления (МБУ).

При записи входное слово Х поступает на регистр слов (PC) и записывается в матрицу памяти по адресу, который в данный момент был установлен в УС. С небольшой задержкой после записи информации содержимое УС уменьшается на единицу, подготавливаясь к следующей записи, так что УС постоянно указывает на пустую ячейку.

При чтении МБУ сначала вырабатывает сигнал, увеличивающий содержимое УС на единицу, а затем сигнал чтения информации из матрицы памяти. В результате на выходных цепях стека появится слово Х, которое было записано последним. Принцип работы стека может быть сформулирован как «последним записан – первым прочитан» (Last In First OUT LIFO). Ввиду отсутствия в коде команд записи (чтения) адресного поля уменьшается разрядность этих команд и время их выполнения.

В МПС используются два вида стека: встроенный и автономный. Встроенный стек полностью размещается на кристалле МП. Емкость (глубина) стека здесь не может быть большой (обычно 16-32 слова). При организации автономного стека в качестве матрицы памяти используется внешнее по отношению к МП ОЗУ, а на кристалле располагается лишь УС с разрядностью, равной разрядности шины адреса; глубина стека может быть равна адресуемой емкости памяти (обычно 64 К). Для компенсации снижения быстродействия в некоторых МП с автономным стеком реализованы аппаратная запись и восстановление при прерываниях содержимого ПС, аккумулятора и регистра состояния.

Работа МПС сопровождается интенсивным обменом информацией между МП, ЗУ, УВВ. Эффективность решения задач МПС в значительной степени определяется организацией этого обмена и структурой связи между МП, памятью и УВВ. Для организации обмена между указанными устройствами вводится понятие интерфейса – это система шин, вспомогательной аппаратуры и алгоритмов, реализованных на этой аппаратуре. В функции интерфейса входят: дешифрация адреса устройств, синхронизация обмена информацией, согласование форматов слов, дешифрация кода команды, связанной с обращением к памяти или УВВ, электрическое согласование сигналов.

Сложность задач, возлагаемых на интерфейс, а также недостаточная мощность буферных схем, входящих в состав БИС МП, привели к распределению средств интерфейса между различными устройствами:

- устройством управления памятью и вводом-выводом, входящим в состав МП;

- непосредственно интерфейсным устройством, являющимся промежуточным звеном между МП, памятью и УВВ;

- специализированными устройствами управления (контроллерами) УВВ.

Различают следующие способы организации связи между МП и УВВ в МПС: программный обмен данными по командам условного перехода; обмен данными по сигналам прерывания; обмен данными в канале прямого доступа в память; подключение устройств ввода-вывода к МП.

При программном обмене данными по командам условного перехода МП программным путем должен определить, готово ли периферийное устройство к выполнению операций ввода-вывода до того, как начнется программная передача данных. Внешнее устройство должно иметь аппаратурные средства для выработки информации о внутреннем состоянии статусной информации. МП считывает эту информацию, передает ее во внутренний регистр-аккумулятор, анализирует и на основе результата анализа принимает решение о готовности устройства (рис.1.6).

МП может находиться в режиме программного ожидания (готовности) внешнего устройства, выполняя команды блоков 1 и 2. После обнаружения состояния готовности МП передает данные по командам блоку 3, а затем приступает к работе по продолжению основной программы.

Рис. 1.6. Алгоритм программного обмена

На рис. 1.7 приведен пример обмена данными по командам условного перехода. Аналого-цифровой преобразователь (АЦП) при передаче данных имеет трехуровневые выходные каскады, передача данных с которых осуществляется по сигналу “Разрешение выдачи” (РВ). По сигналу “Начало преобразования” (НП) АЦП начинает преобразования мгновенной амплитуды входного аналогового сигнала в восьмиразрядный код. По окончанию преобразования выдается управляющий сигнал “Конец преобразования” (КП).

Сигналы НП, КП и РВ считываются МП из байтового выходного регистра данных. Сигналы Д7 – Д0 имеют правильное значение, если соблюдена последовательность выдачи управляющих сигналов НП, КП и РВ согласно временной диаграмме. Сигнал с дешифратора адреса ДСА

Рис. 1.7. Схема подключения АЦП к МП при программном вводе данных

вместе с сигналом операции МП Чт/Зп по сигналу импульса синхронизации С определяет генерацию необходимого управляющего сигнала. По сигналам АНП =АРВ = 1 осуществляется запуск АЦП; по сигналам АРВ = АКП = 1 – считывание и ввод в МП значения сигнала КП. Этот сигнал через трехуровневый каскад вводится в МП по шине Д7. Поэтому команда “Условный переход по знаку результата” определит либо окончание преобразования (КП=1), либо необходимость перехода к новому циклу анализа (КП=0). При сигнале КП=1 командой “Прочитать данные по адресу АРВ” осуществляется ввод информации с АЦП в МП.

Для организации обмена данными по сигналам прерывания от внешних устройств в МП должны быть предусмотрены специальные аппаратурные средства анализа состояния внешних устройств. Если они обнаруживают готовность к обмену какого-либо внешнего устройства, то сигнализируют об этом блоку управления МП, который завершает текущую операцию, передает на хранение в память всю информацию внутренних регистров данных и управления и переходит к подпрограмме обслуживания прерывания. Основная часть этой подпрограммы – команды передачи данных между МП и конкретным внешним устройством. В конце нее имеются программы восстановления состояния МП, которое существовало к началу прерывания.

Если необходимо осуществить обмен между внешним устройством и памятью, то нет необходимости пересылать данные через МП, так как в противном случае затраты времени МП будут очень большими. Можно ввести в МПС контроллер прямого доступа в память, который берет на себя управление передачей. Построение канала ПДП является альтернативой программному обмену, поэтому и в данном случае справедливы общие закономерности балансировки программно-аппаратурных средств. Средства канала ПДП могут быть подключены параллельно процессору (рис.1.8, а), с передачей функции арбитража ОЗУ.

Рис. 1.8. Схема подключения КПД к ОЗУ в МПС

Однако при этом усложняются схемы управления ОЗУ, появляется второй информационный канал, состоящий из информационных МД и МА и управляющих сигналов МУ. Поэтому в МПС решается задача разделения единого информационного канала между МП и КПД в память посредством использования свойств трехуровневого состояния информационных подмагистралей. МП во время передачи информации по КПД переводит выходные схемы управления всех магистралей в высокоомное состояние и изолируется от остальной части системы, что аналогично обрыву его информационного канала (рис. 1.8, б).

Способы подключения внешних устройств к МП определяются возможностями его корпуса, аппаратурно-программных средств, количеством и особенностями устройств ввода-вывода. Запрос на простое прерывание привлекает внимание МП к внешней системе и требует анализа ее состояния.

Если несколько устройств ввода-вывода (УВВ) подключены к своим индивидуальным аппаратурным ресурсам (радиальный интерфейс) (см. рис.1.9, а), то внутри МП необходимо иметь мультиплексор для последовательного опроса всех УВВ. В случае подключения многих УВВ к одному уровню прерывания при простом прерывании требуется обзор всех причин прерывания и выделения активного УВВ.

Последовательное расположение подпрограмм анализа причин прерываний УВВ в программе может считаться приоритетным, если не задан другой алгоритм. Следовательно, первое активное устройство, обнаруженное программой прерывания, получает ресурс на обслуживание. Аппаратурно этот алгоритм реализуется в “цепочечной” схеме подключения УВВ (рис.1.9, б).

Рис.1.9. Схемы подключения УВВ к МП МПС

Векторное прерывание возникает в том случае, когда УВВ, выставившее запрос на прерывание, посылает после выполнения запроса адрес ячейки, где расположена программа прерывания данного УВВ (рис.1.9, в).

Многоуровневые групповые системы (рис.1.9, г) прерывания требуют наличия в МП несколько входов и могут быть векторными, приоритетными или обзорными.

Принципиальные отличия в организации структуры микропроцессора МПС от организации структуры процессора классической ЭВМ (наличие нескольких внутренних шин, РОН, стека и т.п.) приводят к особенностям функционирования МП при организации процессов обработки информации и управления этими процессами.

Процесс обработки информации осуществляется в МПС с помощью его центрального устройства микропроцессора, типовая структура которого в самом общем случае состоит из АЛУ (см. рис. 1.10, а), набора регистров общего назначения (РОН), буферного регистра (БР) и регистра сдвига (Рсдв).

Представленная структура обладает очень широкими возможностями: содержимое любого РОН может быть передано на БР и на Рсдв, а стандартное четырехразрядное АЛУ (рис. 1.10, б) может выполнить 16 логических и 32 арифметических операции над содержимым обоих регистров; результат может быть записан в любой из РОН.

Рис. 1.10. Типовая структура МП

При подаче соответствующих управляющих сигналов в этой системе, например, возможны:

- передача данных из одного РОН в другой (транзитом через БР и АЛУ);

- увеличение или уменьшение на единицу содержимого любого из РОН путем изменения в АЛУ выбранного из РОН значения на единицу и засылки полученного результата в тот же регистр;

- сдвиг содержимого любого РОН путем передачи любого выбранного из РОН числа в Рсдв, сдвига этого числа и записи через АЛУ в тот же РОН.

Очевидно, что для выполнения этих и других операций очень важно распределение подаваемых управляющих сигналов во времени. Например, для передачи данных из одного РОН в другой требуется два такта: 1 такт: адресация РОН, выборка содержимого РОН, прием выбранного слова в БР; 2 такт: адресация РОН, запись в РОН информации через АЛУ. Из этого примера видно, что при определенной последовательности управляющих сигналов будет выполняться определенная операция над данными, хранимыми в РОН. При этом необходимо выполнять два требования (см. рис. 1.11): обеспечение анализа логических условий и ветвление процесса; сохранение сигнала арифметического переноса из АЛУ (триггер Т1) и выходного бита Рсдв (триггер Т2) , т.к. они могут понадобиться при выполнении следующей операции.

С этими изменениями становятся возможными операции над словами с разрядностью, большей, чем разрядность АЛУ, РОН и вспомогательных регистров.

Рис. 1.11. Структура обрабатывающей части МПС

Наиболее полно организацию процесса обработки информации в МПС отображает структурная схема МП, приведенная на рис. 1.12. Для упрощения структуры МП и организации его работы признаки условий обычно хранятся на специально выделенном регистре регистре признаков, разрядность которого не превышает разрядности внутренних шин МП.

Рис. 1.12. Структурная схема МП

В состав МП, помимо ранее рассмотренных устройств, введены регистр результата (РР), мультиплексоры M1 M4, цепи анализа значений логических условий и необходимые управляющие входы.

Рассмотрим назначение введенных мультиплексоров и соответствующих управляющих сигналов, с помощью которых организован процесс обработки информации в МПС.

Мультиплексор M1 мультиплексор цепи переноса: в зависимости от назначения управляющего сигнала У6 (0 или 1) к входу переноса АЛУ подключается или внешний вход, или выход триггера переноса T1.

Мультиплексор M2 мультиплексор цепи сдвига, подключающий к входу триггера сдвига T2 в зависимости от значения сигнала У14 выход старшего или младшего разряда регистра Рсдв.

Мультиплексор M3 мультиплексор цепи сдвига, подключающий к входам старшего или младшего разрядов регистра Рсдв один их четырех выходов в зависимости от комбинации значений сигналов У15 и У16 : выход М2 (У15 =У16 =0), выход триггера Т2 (У15 = 0, У16 =1), логическую единицу (У15 =1, У16 = 0), логический нуль (У15, У16 =1,). Первая комбинация соответствует организации циклического сдвига, оставшиеся отличаются тем, что при сдвиге содержимого Рсдв влево или вправо в освобождающийся заряд записывается, соответственно, содержимое триггера T2, логическая единица или нуль.

Мультиплексор M4 мультиплексор анализа условий, подключающий к выходу P в зависимости от комбинаций сигналов У8 и У9: выход старшего разряда регистра PP; выход схемы ИЛИ-НЕ, единичное значение на котором будет только при нулевом содержимом регистра PP; логическую единицу.

Устройство управления МПС должно выполнять две основные функции: управление выполнением операций и выборку команд программы в нужной последовательности, их дешифрацию и обработку. Существуют два подхода к организации управления выполнением операций.

Первый заключается в том, что n управляющих входов МП объединяются в отдельную n-разрядную шину, на которую для выполнения передачи и (или) обработки информации на каждом шаге алгоритма необходимо подавать n-разрядный вектор (микрокоманду). Этот способ позволяет легко реализовать любой алгоритм, но поскольку на каждом шаге только некоторая часть сигналов имеет единичное значение, а большинство - нулевое, то используется лишь незначительная часть всех n разрядов. Проанализировав архитектуру и назначение МПС, можно выделить группы сигналов, которые никогда одновременно не вырабатываются, и использовать в каждой группе для формирования управляющих сигналов дешифраторы. Такой способ организации управления называется микропрограммным. Структурная схема МП с микропрограммным устройством управления выполнением операций приведена на рис. 1.13, а.

а б

Рис. 1.13. Структура устройств управления МП

В управляющем ЗУ для каждой операции хранится набор микрокоманд (МК), называемых микропрограммой, последовательная выборка и выполнение которых обеспечивает в обрабатывающей части МП преобразование информации, соответствующее коду операции. По коду операции из ЗУ выбирается первая МК микропрограммы выполнения этой операции и поступает на дешифратор микрокоманд ДСМК и схему управления их выполнением. Дешифратор МК расшифровывает код операционной части МК и вырабатывает управляющие сигналы, поступающие в обрабатывающую часть МП. Схема управления выполнением МК по коду адресной части МК и признакам условий формирует адрес следующей МК, который подается на ЗУ. Таким образом будут выбраны и выполнены все МК микропрограммы, что обеспечивает выполнение нужной операции.

Второй подход заключается в том, что все управляющие входы сводятся в один управляющий блок, который расшифровывает приходящую команду и в соответствии с ней вырабатывает необходимую последовательность сигналов (см. рис. 1.13, б). Такой способ организации управления получил название схемного или “жесткого” управления. «Жесткость» и сложность структуры этого типа управления являются его недостатком, высокое быстродействие главным преимуществом. Таким образом, МП должен обеспечивать выборку команд, их дешифрацию, выполнение требуемых операций в соответствии с содержанием полей команды и передачу кода операции в устройство управления. Для выполнения этих функций МП имеет (рис. 1.14): программный счетчик (ПС), регистр команды (РК), схемы выдачи адресов, операндов и содержимого ПС на адресную шину МП, схему приема данных и команд с внешней шины данных на РК; дешифратор команд ДСК.

Рис. 1.14. Структура МП

Адрес

подлежащей выполнению команды хранится

в ПС, с выхода которого он поступает

через буфер адреса (БА) на адресные входы

внешнего ЗУ команд. Выбранная по сигналу

Уi команда поступает через буфер данных

(БД) на РК. Код команды расшифровывается

дешифратором команд (ДСК), который

передает код операции в УУ. Последнее

вырабатывает требуемую последовательность

управляющих сигналов Уi, обеспечивающих

выполнение нужной операции в МП. Если

в процессе выполнения операции требуется

обращение к РОН, то ДСК выставляет адрес

регистра на адресных входах РОН

(см. рис. 1.12).

(см. рис. 1.12).

Упражнения

1. Дополните структуру МП на рис.1.12 схемами для ввода и вывода информации, используя в качестве УВВ регистры. Необходимо предусмотреть соответствующие комбинационные схемы.

2. Применительно для МП, представленного на рис.1.12, описать потактовое выполнение следующих команд: 1) запись содержимого регистра Р1, входящего в состав РОН, в другой РОН – Р2; 2) сложение содержимого регистров Р1 и Р2 РОН с занесением результата в Р2.

Контрольные вопросы

1. Как можно выполнить сложение двух восьмиразрядных чисел на четырехразрядном МП?

2. Укажите основные преимущества и недостатки микропрограммного и схемного (жесткого) устройства управления МПС.

3. Когда целесообразно использовать одношинную и трехшинную организацию МП в МПС?

4. Почему значения отдельных признаков сводят в один регистр?

5. Чем отличается микроЭВМ от МПС?

6. Перечислите преимущества, обеспечиваемые вводом-выводом данных в канале прямого доступа в память.

7. Какое расширение возможностей МПС можно получить с помощью дополнительных проблемно-ориентированных процессоров?

8. Какие возможности открывают МП для реализации параллельных вычислительных процессов?

2. АРХИТЕКТУРА МИКРОЭВМ И МИКРОПРОЦЕССОРНЫХ СИСТЕМ

Реальная система на основе микропроцессора содержит значительное число функциональных устройств, одним из которых является микропроцессор. Все устройства системы имеют стандартный интерфейс и подключаются к единой информационной магистрали.

Микропроцессор выполняет в системе функции центрального устройства управления и устройства арифметико-логического преобразования данных. В качестве устройства управления он генерирует последовательность синхронизирующих и логических сигналов, которые определяют последовательности срабатывания всех логических устройств системы. Кроме этого микропроцессор задает и последовательно осуществляет микрооперации извлечения команд программы из памяти системы, их расшифровку и исполнение, тем самым выполняя арифметические, логические или иные операции над числами.

Для подключения разнообразных устройств ввода или вывода данных (а также комбинированных аппаратов ввода-вывода) необходимо привести все их связи и сигналы к стандартному виду, т.е. провести согласование интерфейсов. Для этого используется специальный аппаратурный блок – информационный контроллер (ИК), имеющий стандартный интерфейс со стороны подключения к информационной магистрали и нестандартный интерфейс со стороны устройства ввода-вывода, т.е. являющийся преобразователем интерфейсных сопряжений.

МП, ОЗУ и ПЗУ вместе с УВВ, называется микроЭВМ. МикроЭВМ – это ЭВМ, центральная часть которой в составе процессора, ОЗУ, ПЗУ, информационного контроллера построена на основе БИС. Применение БИС в качестве основных элементных компонентов обеспечивают микроЭВМ такие преимущества перед другими типами ЭВМ, как компактность, надежность, малая материалоемкость, низкие мощность потребления и стоимость. Но магистральная структура микроЭВМ и скоростные ограничения микропроцессора определяют умеренные характеристики производительности микроЭВМ. Это относится к микроЭВМ на основе микропроцессоров на одном или нескольких кристаллах. В микроЭВМ на основе биполярных микропроцессорных секций можно получить высокое быстродействие за счет реализации конвейерной обработки данных и высокоэффективного скоростного управления вычислительным процессом даже при магистральной структуре.

При использовании микроЭВМ в контуре управления некоторого объекта (процесса) она становится центральной частью системы контроля, управления и вычисления. Для сопряжения с микроЭВМ объект (процесс) должен быть оснащен датчиками состояния и исполнительными механизмами. Датчики выступают как источники вводимой для микроЭВМ информацией, а исполнительные механизмы – как приемники выводимой информации. Для согласования интерфейсов подключение датчиков и исполнительных механизмов в системе осуществляется через блоки сопряжения датчиков и исполнительных механизмов.

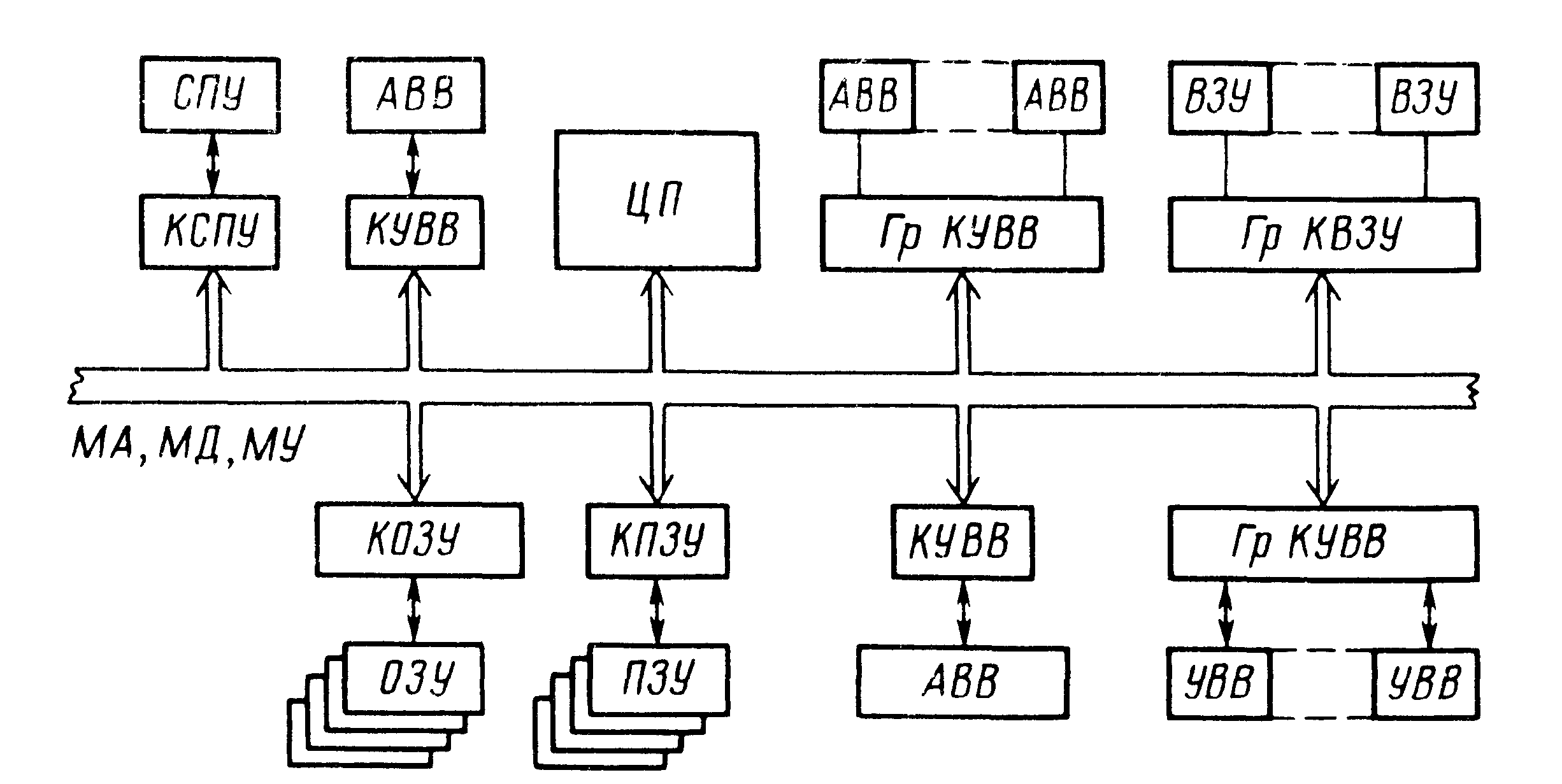

На рис.2.1 приведена обобщенная логическая структура микроЭВМ, в которой в качестве всех управляющих блоков и устройств используются программируемые контроллеры (например, контроллер системного пульта управления КСПУ).

Все устройства ввода-вывода управляются контроллерами устройств ввода-вывода (КУВВ) или групповыми контроллерами устройствами ввода-вывода (ГрКУВВ). Оперативное (ОЗУ) и постоянное (ПЗУ) запоминающие устройства управляются с помощью соответствующих контроллеров (КОЗУ и КПЗУ). При такой организации центральный процессор (ЦП) обеспечивает программируемые контроллеры только управляющей информацией высокого уровня, детализируемой контроллерами. Поэтому количество управляющей информации на информационной магистрали системы резко уменьшается, что позволяет увеличить скорость передачи данных. По существу в этой схеме приведена многопроцессорная вычислительная система, в которой в пределе контроллер имеет те же возможности, что и центральный процессор. Низкая стоимость и высокая надежность БИС позволяют для достижения желаемых параметров ввести распределенное управление и распределенную обработку во всех подсистемах системы, что определяет новые способы организации вычислительных процессов в системах с децентрализованным управлением и обработкой информации.

Рис 2.1. Обобщенная логическая структура микроЭВМ с микропроцессорными контроллерами.

Для включения МП в любую МПС необходимо установить единые принципы и средства его сопряжения с остальными устройствами системы, т.е. создать унифицированный интерфейс.

Унифицированный интерфейс – совокупность правил, устанавливающих единые принципы взаимодействия устройств МПС. В состав интерфейса входят аппаратурные средства соединения устройств (разъемы и связи), номенклатура и характер связей, программные средства, описывающие характер сигналов интерфейса и их временную диаграмму, а также описание электрофизических параметров сигналов.

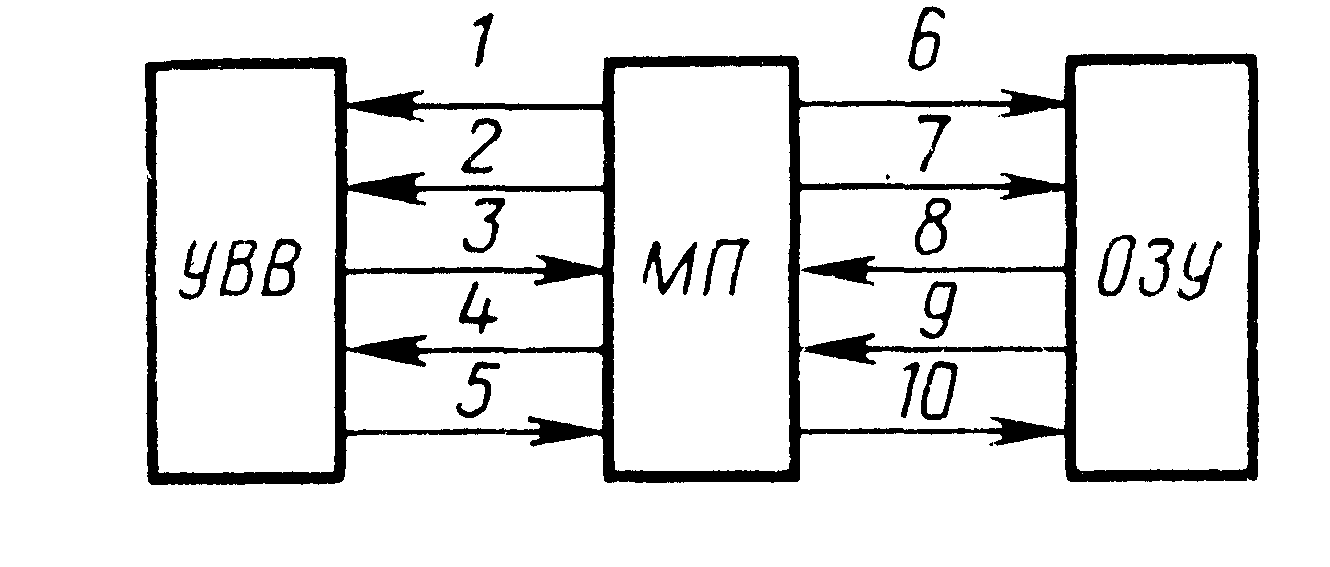

На рис. 2.2 представлена общая схема сопряжения МП с устройствами ввода-вывода УВВ и ОЗУ в микропроцессорной системе.

Рис 2.2. Схема интерфейсных связей микропроцессора

Связь МП с УВВ требует пять групп связей, обеспечиваемых через выводы корпуса МП. По группе шин 1 передается код выбора (адреса) устройства, по шине 2 – сигнал управления считыванием – записи, по шине 3 – сигнал запроса на прерывание, шины 4 и 5 используются для передачи данных от МП к УВВ и от УВВ к МП. Связь МП с ОЗУ также содержит пять групп связей, которые необходимо обеспечить через выводы корпуса МП. По группе шин 6 передается адрес в ОЗУ, шина 7 нужна для управления чтением/записью, по сигналам на шине 8 принимаются команды в МП, а шины 9 и 10 обеспечивают передачу данных из ОЗУ в МП и обратно.

Совершенствование технологии БИС оказывает влияние на архитектуру МПС: создаются принципиально новые функциональные модули на СБИС, что, в свою очередь, обуславливает изменение в архитектуре систем из микроЭВМ. К преимуществам этих МПС относятся: невысокая стоимость, эксплуатационная надежность, расширение функциональных возможностей, повышение производительности и, как следствие, расширение класса решаемых задач и областей применения. В результате сформировался новый подход к построению МПС и их архитектур.

Традиционная последовательная обработка информации предполагает последовательную архитектуру МПС. В этом случае говорят, что архитектура МПС является архитектурой типа ОКОД: Один поток Команд предназначается только для обработки Одного потока Данных (SISD Simple Instructions Simple Dates).

Наряду с этой появились следующие типы организации вычислительного процесса и, соответственно, следующие типы архитектур МПС:

- магистральные - Много потоков Команд обрабатывают Один поток Данных (МКОД или MISD Many Instruction Simple Dates);

- ассоциативная и матричная Один поток Команд обрабатывает Много потоков Данных (ОКМД или SIMD Simple Instruction Many Dates);

- мультимикропроцессорная Много потоков Команд обрабатывает Много потоков Данных (МКМД или MIMD Many Instruction Many Dates).

На основе организации SIMD и MIMD создан вариант архитектуры МПС типа SMIMD несколько потоков команд и данных с коммутацией.

Современные МПС условно можно подразделить по назначению на два класса, осуществляющие решение: локальных задач отдельными процессорными элементами; глобальных задач системой в целом. Локальные задачи, как правило, невелики по объему и могут быть решены с помощью МПС, состоящих из отдельных микроЭВМ. Глобальные задачи достаточно сложны и требуют для решения МПС высокой производительности.

Выбор эффективных способов взаимосвязи микроЭВМ в МПС относится к актуальным проблемам теории построения систем обработки данных. При этом выбираются не связи между микроЭВМ, а между реализуемыми программами. Кроме этого на каждую микроЭВМ в системе с распределенными функциями возлагается управление вводом-выводом и межпроцессорным обменом.

Все возможные способы межпроцессорного обмена в распределенных МПС можно реализовать с помощью следующих основных методов: метод общей шины, метод переключающей матрицы и метод иерархии.

В первом случае через одну шину данных выполняется несколько команд всех микроЭВМ, ЗУ и периферийных устройств (см. рис. 2.3).

Рис. 2.3. Метод общей шины

Во втором случае (см. рис. 2.4) переключающая коммутирующая матрица соединяет любую микроЭВМ системы с любым ЗУ и периферийным устройством с помощью специальной программы коммутации.

Рис. 2.4. Метод коммутирующей матрицы

В иерархической структуре (см. рис.2.5) управляющая микроЭВМ (УµЭВМ) организует опрос микроЭВМ (µЭВМ) нижних уровней и выдачу им команд данных.

Рис. 2.5. Метод иерархии

Обмен данными между микроЭВМ системы может быть регулярным и нерегулярным. В первом случае функционирование МПС можно расписать по времени и применить метод разделения, при котором период работы каждого канала разбивается на интервалы времени, закрепленные за каждой микроЭВМ системы. При нерегулярном информационном обмене во избежание прерывания работы микроЭВМ используют общее для всех микроЭВМ ЗУ, связанное также с устройством управления каналами, которое при наличии свободного канала закрепляет его за микроЭВМ и извещает ее об этом.

Контрольные вопросы

1. Дайте определение микроЭВМ, укажите назначение и состав ее основных узлов и блоков.

2. Перечислить основные типы архитектур МПС и указать особенности их функционирования.

3. Перечислите способы организации межпроцессорного обмена в распределенных МПС.

3. ЭТАПЫ ПРОЕКТИРОВАНИЯ МИКРОПРОЦЕССОРНЫХ СИСТЕМ

Качественные и количественные изменения элементной базы средств ВТ привели к изменению сложившихся принципов их проектирования (таких, как жесткая структура, последовательное центральное управление, линейная организация памяти и отсутствие возможности адаптации структуры ЭВМ к особенностям решаемой задачи).

На смену классическим фоннеймановским принципам организации вычислительных систем пришли идеи проблемной ориентации МПС, параллельной и конвейерной обработки информации, использование табличных методов обработки данных, принципы регулярности и однородности структур МПС; становится реальной возможностью идея создания адаптивно-перестраиваемых систем, а также аппаратная реализация функций программного обеспечения. Поэтому в настоящее время при проектировании вычислительных систем на основе МПС получил применение так называемый принцип «3М»: модульность, магистральность, микропрограммируемость.

Принцип модульной организации предполагает построение вычислительных и управляющих МПС на основе набора модулей: конструктивно, функционально и электрически законченных вычислительных устройств, позволяющих самостоятельно или в совокупности с другими модулями решать задачи данного класса. Модульный подход при проектировании микроЭВМ и систем позволяет (при реализации как универсальных, так и специализированных модулей) обеспечить создание семейств (рядов) МПС, отличающихся функциональными возможностями и характеристиками, перекрывающими значительный диапазон применений, способствует сокращению затрат на проектирование, а также упрощает наращивание мощности и реконфигурацию систем, отодвигает время морального старения вычислительных средств.

Магистральный способ обмена информацией в отличие от способа организации произвольных связей (по принципу «каждый с каждым») позволяет упорядочить и минимизировать число связей в МПС. Он обеспечивает обмен информацией между функциональными и конструктивными модулями различного уровня с помощью магистралей, объединяющих входные и выходные шины. Различают одно-, двух-, трех- и многомагистральные связи. Необходимо отметить взаимосвязь схемотехнических и структурных решений, которые проявляются при реализации данного способа обмена в виде создания специальных двунаправленных буферных каскадов с тремя устойчивыми состояниями и использовании временного мультиплексирования каналов обмена.

Микропрограммное управление обеспечивает наибольшую гибкость при организации многофункциональных модулей и позволяет осуществить проблемную ориентацию МПС, а также использовать в них макрооперации, что эффективнее использования стандартных подпрограмм. Кроме этого, передача управляемых слов в виде зашифрованных кодовых последовательностей соответствует условиям минимизации числа выводов СБИС и сокращению числа межсоединений в модулях.

Кроме перечисленных выше основных особенностей проектирования МПС, следует отметить принцип регулярности, который предполагает закономерную повторяемость элементов структуры МПС и связей между ними. Применение данного принципа позволяет увеличить интегральную плотность, уменьшить длину связей на кристалле, сократить время топологического и схемотехнического проектирования БИС и СБИС, уменьшить число пересечений и типов функциональных и конструктивных элементов.

При разработке архитектуры МПС (системный этап) необходимо решить следующие задачи:

- дать описание концептуальной структуры функционального поведения системы с позиций учета интересов пользователя при ее построении и организации вычислительного процесса в ней;

- определить структуру, номенклатуру и особенности построения программных и микропрограммных средств;

- описать характеристики внутренней организации потоков данных и управляющей информации;

- провести анализ функциональной структуры и особенности физической реализации устройств системы с позиции сбалансированности программных, микропрограммных и аппаратурных средств.

Основные этапы проектирования МПС приведены на рис. 3.1.

На начальной стадии проектирования МПС может быть описана на одном из следующих концептуальных уровней: “черный ящик”, структурный, программный, логический, схемный.

На уровне “черного ящика” МПС описывается внешними спецификациями, где перечисляются внешние характеристики.

Рис. 3.1. Этапы проектирования МПС

Структурный уровень создается аппаратными компонентами МПС, которая описывается функциями отдельных устройств, их взаимосвязью и информационными потоками.

Программный уровень разделяется на два подуровня (команд процессора и языковый) и МПС интерпретируется как последовательность операторов или команд, вызывающих то или иное действие над некоторой структурой данных.

Логический уровень присущ исключительно дискретным системам и разделяется на два подуровня: переключательных схем и регистровых пересылок. Первый подуровень образуется вентилями (комбинационные схемы и элементы памяти) и построенными на их основе операторами обработки данных. Второй подуровень характеризуется более высокой степенью абстрагирования и представляет собой описание регистров и передачу данных между ними. Он включает в себя две части: информационную и управляющую: первая образуется регистрами, операторами и путями передачи данных, вторая обеспечивает зависящие от времени сигналы, инициирующие пересылку данных между регистрами.

Схемный уровень базируется на описании работы элементов дискретных устройств.

В жизненном цикле МПС, как и любой дискретной системы, выделяются три стадии: проектирование, изготовление и эксплуатация. Каждая из стадий подразделяется на несколько фаз, для которых существуют вероятности возникновения конструктивных или физических неисправностей. Неисправности классифицируют в соответствии с их причинами: физическая, если причиной ее служат дефекты элементов, и субъективная, если ее причиной служат ошибки проектирования.

Субъективные неисправности делят на проектные и интерактивные. Проектные неисправности вызваны недостатками, вносимыми в систему на различных стадиях реализации исходного задания. Интерактивные неисправности возникают в процессе работы по вине обслуживающего персонала (оператора). Результатом проявления неисправности является ошибка, причем одна неисправность может служить причиной целого ряда ошибок, а одна и та же ошибка может быть вызвана множеством неисправностей.

Существует также понятие дефекта - физическое изменение параметров компонентов системы, выходящих за допустимые пределы. Дефекты называют сбоями, если они носят временный характер, и отказами, если они постоянны. Дефект не может быть обнаружен до тех пор, пока не будут созданы условия для возникновения из-за него неисправности, результат которой должен быть, в свою очередь, передан на выход исследуемого объекта для того, чтобы сделать неисправность наблюдаемой.

Диагностика неисправности – процесс определения причины появления ошибки по результатам тестирования. Отладка – процесс обнаружения ошибок и определения источников их появления по результатам тестирования при проектировании МПС. Средствами отладки являются приборы, комплексы и программы. Иногда под отладкой понимают обнаружение, локализацию и устранения неисправности. Успех отладки зависит от того, как спроектирована система, предусмотрены ли свойства, делающие ее удобной для отладки, а также от средств, используемых для отладки. Для проведения отладки проектируемая МПС должна обладать свойствами управляемости, наблюдаемости и предсказуемости.

Управляемость – свойство системы, при котором ее поведение поддается управлению, т.е. имеется возможность остановить функционирование системы в определенном состоянии и заново запустить систему.

Наблюдаемость – свойство системы, позволяющее проследить за поведением системы, за сменой ее внутренних состояний.

Предсказуемость – свойство системы, позволяющее установить систему в состояние, из которого все последующие состояния могут быть предсказуемы.

МПС по своей сложности, требованиям и функциям могут значительно отличаться эксплуатационными параметрами, объемом программных средств, типом микропроцессорного набора и т.д. В связи с этим процесс проектирования может видоизменяться в зависимости от требований, предъявляемых к системе. Например, процесс проектирования МПС, отличающихся одна от другой содержанием ПЗУ, будет состоять из разработки программ и изготовления ПЗУ. При проектировании многопроцессорных МПС, содержащих несколько типов МПК, необходимо решать вопросы организации памяти, взаимодействия с процессорами, организации обмена между устройствами системы и внешней средой и т.п.

Наиболее типичными этапами проектирования и разработки МПС являются: формализация требований к системе; разработка структуры и архитектуры МПС; разработка и изготовление аппаратурных средств и программного обеспечения системы; комплексная отладка и приемосдаточные испытания.

Процесс проектирования – итерационный процесс. Неисправности, обнаруженные на этапе приемосдаточных испытаний, могут привести к коррекции спецификации, а следовательно, к началу проектирования всей системы. Обнаруживать неисправности необходимо как можно раньше; для этого надо контролировать корректность проекта на каждом этапе разработки. Существуют следующие методы контроля правильности проектирования: верификация (формальные методы доказательства корректности проекта); моделирование; тестирование.

В последнее время появилось много работ по верификации программного обеспечения, микропрограмм, аппаратуры. Однако эти работы пока носят теоретический характер. Поэтому на практике чаще используют моделирование поведения объекта и тестирование на различных уровнях абстрактного представления системы.

На этапе формализации требований к системе контроль корректности проекта особо необходим, поскольку многие цели проектирования не формализуются или не могут быть формализованы в принципе. Функциональная спецификация может анализироваться коллективом экспертов или моделироваться и проверяться в опытном порядке для выявления достижения желаемых целей. После утверждения функциональной спецификации начинается разработка тестовых программ, предназначенных для установления правильности работы системы в соответствии с ее спецификацией. В идеальном случае разрабатываются тесты, целиком основанные на этой спецификации и дающие возможность проверки любой реализации системы, которая объявляется способной выполнять функции, оговоренные в спецификации. Этот способ – полная противоположность другим, где тесты строятся применительно к конкретным реализациям. Однако на практике разработке тестов часто присваивают более низкий приоритет по сравнению с проектом, поэтому тестовые программы появляются значительно позже его завершения.

Контрольные вопросы

1. Поясните понятия модульности, магистральности и микропрограммируемости МПС при проектировании.

2. Перечислите задачи, решаемые разработчиками при проектировании МПС.

3. Перечислите основные этапы проектирования МПС.

4. Назовите концептуальные уровни описания МПС при проектировании и разработке.

5. Перечислить основные методы контроля правильности проектирования МПС.

6. Какими свойствами должна обладать проектируемая МПС для выполнения этапа ее отладки?

7. Перечислите виды неисправности при проектировании МПС.

8. Назовите причины физической и субъективной неисправностей МПС.

9. Поясните понятия: диагностика неисправности, отладка.

4. ОРГАНИЗАЦИЯ И ОСОБЕННОСТИ ПРОЕКТИРОВАНИЯ МПС НА ОСНОВЕ ОДНОКРИСТАЛЬНЫХ МИКРОЭВМ

4.1. Общие принципы организации однокристальных микроЭВМ

С повышением степени интеграции микросхем стало возможным реализовать на одном кристалле сложные функциональные блоки. Зa недолгую историю развития элементной базы микропроцессорных вычислительных устройств были разработаны принципиально новые структуры БИС. Такие микросхемы, имеющие высокую степень интеграции и работающие согласно заданной программе, получили название микропроцессорных БИС (МП БИС). Стало возможным реализовать ЭВМ на нескольких типах МП БИС, объединенных в так называемые микропроцессорные комплекты (МПК) БИС, которые отличаются друг от друга функциональными возможностями, технологией изготовления, конструктивными особенностями, быстродействием, потребляемой мощностью и т.п.

Микропроцессорные БИС принято разделять на три основных класса: секционированные с наращиванием разрядности и микропрограммным управлением; модульные МП - на основе однокристальных МП БИС с фиксированным набором команд и разрядностью; однокристальные микроЭВМ.

Секционированные МП БИС включают совместимые микросхемы различного функционального назначения, на основе которых можно реализовать MПC различной структуры и разрядности, кратной разрядности секции. В зависимости от назначения разрабатываемой аппаратуры выбирается структура секционированных БИС и система команд. Эти БИС широко применяются при проектировании высокопроизводительных мультимикропроцессорных систем.

МП БИС на основе однокристальных МП и однокристальных микроЭВМ, обладающие меньшей производительностью, но гибкой системой команд и большими функциональными возможностями, ориентированы на широкое применение в различных областях науки, техники и производства - от контроллеров и калькуляторов, до МПС управления, цифровой обработки сигналов и интеллектуальных робототехнических систем.

В настоящее время наибольшее распространение получили МП БИС на основе разновидностей МОП- технологии и интегральной инжекционной логики(И2Л). Требования к быстродействию предопределили развитие биполярных МП БИС на основе транзисторно-транзисторной логики с диодами Шотки(ТТЛШ) и эмиттерно-связанной логики (ЭСЛ).

Следует отметить, что при проектировании МПС для различных применений обязательным условием эффективного использования МП БИС является конструктивная и технологическая совместимость всей элементной базы системы - микросхем малой, средней и большой степени интеграции, используемых в центральном процессоре, блоках памяти, устройствах ввода-вывода.

Как правило, в состав однокристальных МП БИС, служащих для реализации однокристальных микроЭВМ и МПС на их основе, входят следующие БИС: микропроцессор с памятью, последовательный или параллельный интерфейс, контроллеры (ПДП, прерываний, клавиатуры и т.п.).

В последние годы получила новое развитие номенклатура однокристальных микроЭВМ и специализированных МПК цифровой обработки сигналов, которые имеют большую перспективу применения в силу своих функциональных возможностей и характеристик.

Состав и структура МПК БИС зависят от областей применения и, как правило, имеют минимально необходимое число БИС для организации микроЭВМ и МПС.

Типичным представителем МПС с однокристальным МП является отечественный микропроцессорный комплект серии К1810, в котором реализуются и находят дальнейшее развитие идеи построения одно- и многопроцессорных систем на базе МП БИС с фиксированным набором команд. В комплект входят как универсальные и специализированные процессоры (процессор ввода-вывода, арифметический процессор), так и схемы, позволяющие сформировать магистрали микроЭВМ. Комплект может расширяться за счет разработки новых схем, программно и аппаратно совместимых с МП БИС.

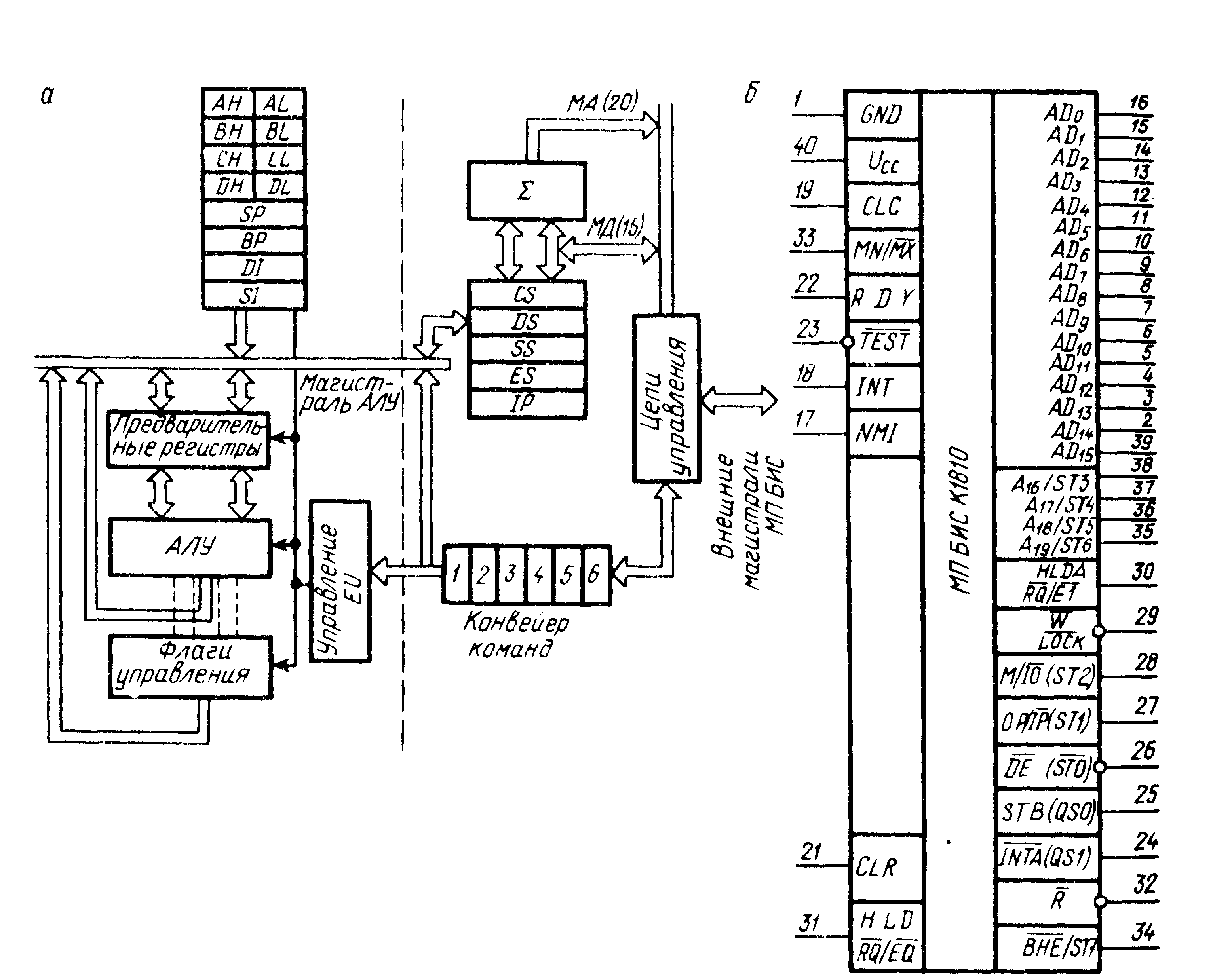

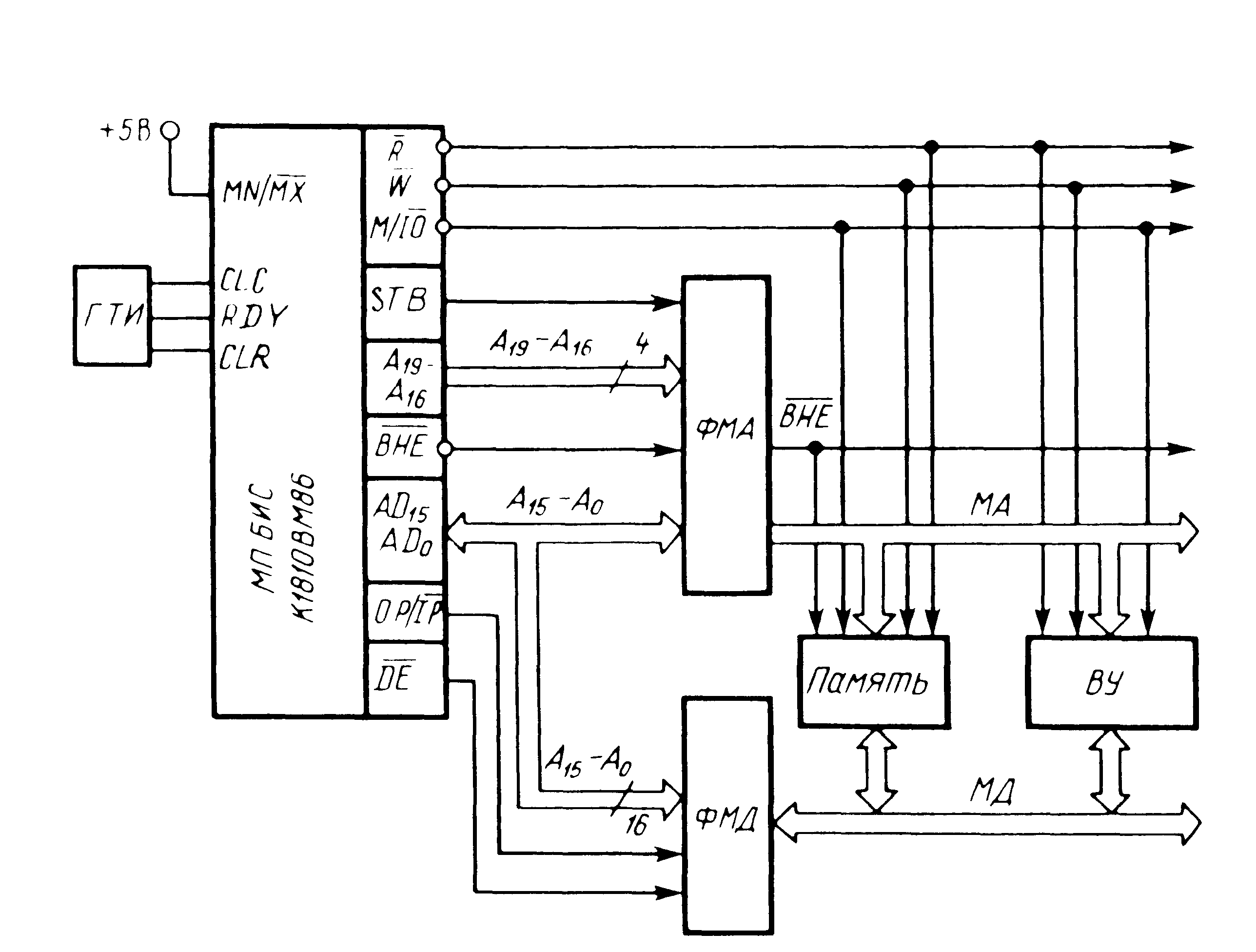

Основной схемой в комплекте является МП БИС К1810ВМ86, которая представляет собой однокристальный 16-разрядный МП с мультиплексной 20-разрядной магистралью адреса и 16-разрядной магистралью данных и рассчитана на работу как в одно-, так и в многопроцессорных системах. Схема выпускается в 40-выводном корпусе (рис. 5.1). Ряд выводов схемы используется для выдачи импульсов управления, синхронизирующих работу микроЭВМ. Питание схемы осуществляется от источника с напряжением 5 В. Синхронизация работы МП БИС осуществляется импульсами внешнего тактового генератора, подаваемыми на вход CLK.

Эффективность работы МП БИС К1810ВМ86 существенно повышена за счет введения команд математических операций (включающих умножение и деление) над 8- и 16-разрядными числами, команд побитовой обработки чисел, команд работы с массивами данных, расширения видов прерываний работы МП БИС, а также реализации конвейерного типа выполнения команд в самой БИС. Микропроцессорная БИС может работать с памятью объемом до 1 Мбайта, обмениваться информацией с 64 Кбайтами внешних устройств, имеет 256 типов различных прерываний.

Обычно процесс выполнения команд программы в МП включает в себя следующие этапы: извлечение кода команды (операндов команды, если этого требует код команды) из памяти; выполнение команды; запись результата (если этого требует команда). Как правило, в МП все эти этапы выполняются последовательно, что приводит к недоиспользованию по временной загрузке магистралей микроЭВМ. В МП БИС К1810ВМ86 процесс выполнения команд состоит из тех же этапов, однако проводится в двух раздельных процессорных блоках (см. рис. 4.1, а): блоке выполнения команд (execution unit – EU) и блоке сопряжения с магистралями (Bus Interface Unit – BIU). В функции BIU входит извлечение из памяти кода команд и их операндов, а также запись результата в память. Блоки могут работать независимо друг от друга, и, следовательно, процессы преобразования и передачи информации в них могут идти параллельно.

Блок выполнения команд имеет 16-разрядное АЛУ с регистром состояния и флагами управления, а также регистры общего назначения. Все регистры и внутренние магистрали блока 16-разрядные. Блок не имеет связи с внешними магистралями МП БИС. На АЛУ поступают коды команд из конвейера команд, расположенного в BIU. Если в результате дешифрации кода команд в АЛУ необходимо получение одного или нескольких операндов по внешним магистралям МП БИС, то EU запрашивает BIU на получение и размещение необходимых данных в BIU. Несмотря на то, что все адреса, с которыми оперирует EU, 16-разрядные, BIU производит необходимое преобразование адресов так, чтобы EU имел возможность обращаться ко всему возможному адресному пространству (1 Мбайт) микропроцессорной системы.

Рис. 4.1. Упрощенная схема МП БИС КР1810 ВМ86

Блок сопряжения с магистралями производит все пересылки данных и кодов для EU. Пересылки между МП БИС и памятью или внешними устройства-ми осуществляются по требованию EU. В то время как EU занят выполнением команды, блок BIU получает последующие в программе коды команд из памяти и сохраняет их в конвейере команд. В конвейере может быть записано до шести кодов команд. Это позволяет BIU выдавать в EU сохраненные команды по мере необходимости без загрузки внешних магистралей МП БИС. Блок BIU организует получение нового кода команды, как только два байта в конвейере команд будут переданы в EU. За один цикл получения кода команды в блок BIU записываются с МД два байта команды.

В большинстве случаев в BIU находится хотя бы одна команда и EU не ждет, пока очередная команда будет извлечена из памяти.

Коды команд подаются в EU последовательно так, как они записаны в программе. Если EU выполняет команду передачи управления в другое место программы, то BIU очищает конвейер команд, получает код команды из нового адреса, передает его в EU и начинает заполнять конвейер заново. Если EU требует обращения к памяти или внешнему устройству, то BIU приостанавливает процесс получения команд в конвейер и организует необходимый цикл обмена данными.

На рис. 4.2 приведен пример построения однопроцессорной системы.

Рис. 4.2. Структура микроЭВМ на базе МП БИС КР1810ВМ86

Основная задача, решаемая в многопроцессорных системах, заключается в обеспечении распределения времени доступа каждого из процессоров к общей системной магистрали. Магистрали микроЭВМ представляют собой систему MULTIBUS, в состав которой входят 16-разрядная МД, 20-разрядная МА, восемь входов прерываний, шины управления и шины арбитража. Последние позволяют осуществить синхронизацию процесса использования системных магистралей при параллельной работе нескольких процессоров в системе. Для формирования шин управления и арбитража в таких системах применяются специальная схема системного контроллера и схема арбитража работы процессоров. Схемы используют следующие выводы МП БИС: RQ/EQ, RQ/E1, позволяющие сопроцессорам брать управление магистралями системы; QS0 и QS1, отображающие состояние конвейера команд и позволяющие внешним устройством или сопроцессорам системы следить за выполнением команд МП БИС; LOCK – сигнал, используемый для запрета доступа к магистралям на время выполнения текущей команды.

4.2. Особенности проектирования МПC на основе однокристальных микроЭВМ и контроллеров.

Так же, как и при выполнении системного этапа проектирования любых ЭВМ, при проектировании МПC на основе однокристальных микроЭВМ с самого начала должны быть определены и документированы основные функциональные характеристики разрабатываемой системы: разработчики и изготовители МПС могут интерпретировать характеристики не так, как заказчик и это может привести к необходимости переделки уже выполненной работы.

Результатом этого этапа должна быть структурная схема МПС с определением всех входных и выходных сигналов и их электрических и временных характеристик. На этом же этапе желательно составить так называемый "служебный обзор", в котором форма задания функциональных характеристик заказчика заменяется на более удобную для разработчика. Толкование этого документа должно иметь полное понимание и однозначность. Можно также внести предложения по улучшению характеристик и параметров МПС, которые заинтересуют заказчика. Выбор MП MПC - достаточно сложная процедура, при которой надо учитывать множество факторов. Если, например, доступна только одна модель однокристального МП, то проблема выбора сводится к ответу на вопрос: можно ли построить МПС с требуемыми характеристиками на основе этого МП. При разработке МПС с предполагаемым большим объемом выпуска выбор и проверка правильности принятого решения требуют значительного времени.

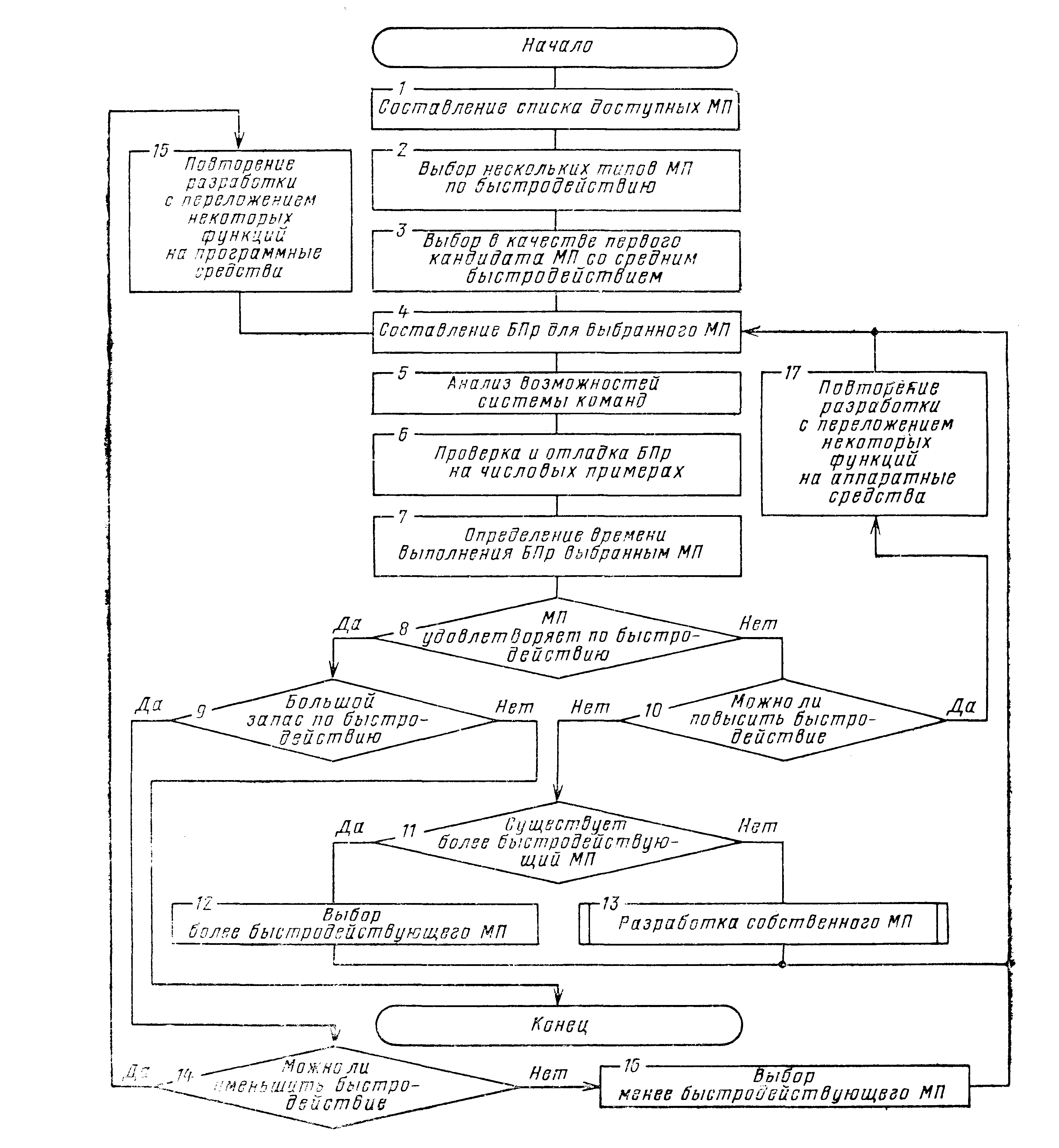

Так как одним из главных критериев при выборе MП является требуемое быстродействие, наиболее распространенным методом его оценки является использование так называемых б е н ч м а р к о в с к и х программ (БПр). БПр - это программа решения на анализируемом МП такой задачи, которая по составу операций соответствует классу задач предполагаемого применения. Обычно длина БПр – 100-200 команд. В состав ее обязательно должны входить операции по вводу-выводу.

Важным достоинством выбора МП на основе БПр является то, что она не только определяет время решения задачи на конкретном MП, но и вскрывает достоинства и недостатки его системы команд для заданной области применений. Если проверка правильности составления БПр на конкретных числовых примерах покажет, что БПр не дает удовлетворительных временных показателей ее выполнения, следует использовать один из следующих подходов:

- повторить разработку для этого же МП, но перераспределить при этом программные и аппаратные средства таким образом, чтобы обеспечить требуемые характеристики по быстродействию;

- выбрать более быстродействующий МП.

Процедура выбора МП с помощью БПр приведена на рис. 4.3.

Разработка аппаратной части МПС должна начинаться с разработки ее процессора, поскольку в дальнейшем он может использоваться для проверки других устройств. Обычно в процесс разработки процессора входят этапы по разработке вспомогательного оборудования, которое позволяет упростить проверку и отладку процессора.

В состав МПК БИС в ряде случаев не входит генератор тактовых импульсов, поэтому он должен быть разработан и изготовлен в первую очередь, так как он может быть единственным элементом, необходимым для запуска процессора.

Если МПС реализуется на сравнительно большом числе ИС, а рабочая программа достаточно сложна, то потребуется разработка и изготовление пульта. Он должен иметь индикацию состояния адресной шины и шины данных. Кнопки и переключатели должны обеспечивать управление пуском и остановкой, шаговым режимом и вводом данных и команд в ОЗУ МПС.

Правильность функционирования процессора МПС должна проверяться в режиме выполнения программы. Поскольку платы памяти изготавливаются обычно позже, для проверки процессора необходимо разработать и изготовить макет небольшого ЗУ.

Рис. 4.3. Процедура выбора МП

Проверку рекомендуется начать с выполнения команды условного перехода, которая передает управление самой себе. Это позволит, во-первых, убедиться в работоспособности МП, а, во-вторых, исследовать временную диаграмму работы процессора MПС с помощью осциллографа. На основе макета памяти можно проверить выполнение всех команд, а позже проверить работоспособность остальной аппаратуры МПС.

Характеристики МПС в значительной степени определяются организацией обмена информацией между МП, основной памятью и внешними устройствами. Поэтому разработка интерфейса системы является одним из наиболее ответственных этапов разработки. Сложностъ этого этапа обуславливается тем, что связь БИС, входящих в MПK, обычно функционально и структурно строго регламентирована руководящим техническим материалом, спецификой МПС, предназначенной для конкретного применения, и определяется исключительно внешними устройствами МПС и их связью с МП и основной памятью. На аппаратуру, обеспечивающую этот интерфейс, в некоторых случаях приходится 60-80% общих аппаратурных затрат. В функции интерфейса обычно входят операции по дешифрации адреса устройства, синхронизации обмена, согласование информационных и управляющих сигналов, дешифрация кода команды, генерирование запросов на прерывание процессора и др.

Для того, чтобы МПС могла выполнять задачи обработки данных, ее необходимо снабдить соответствующим программным обеспечением (ПО), которое подразделяется на две части: системное и прикладное. Основой системного ПО служит, как правило, некоторая операционная система, которая включается в состав МПС при ее поставке потребителю. Прикладное ПО содержит комплекс программ, соответствующих специфике области применения системы. И системное, и прикладное ПО создаются с помощью подходящих языков программирования, включая язык Ассемблера данной МПС и языки высокого уровня.

Составляя программу для МПС (или микроЭВМ) в машинных кодах или на языке Ассемблера, программист абстрагируется от всего многообразия элементов МПС и имеет дело лишь с системой команд и ограниченным числом ее регистров, называемых программно-доступными регистрами. Эти регистры характеризуются тем, чти их имена или условные обозначения (номера) могут применяться в машинных командах, а содержимое регистров может быть изменено, прочитано или использовано с помощью соответствующих команд по желанию программиста. Программно-доступные регистры обычно составляют лишь небольшую часть всех регистров MП. Никакие другие элементы МП, кроме его программно-доступных регистров, не находят отражения в программах, написанных в кодах системы или на языке Ассемблера. Следовательно, с точки зрения программиста МП МПС представляет собой совокупность программно-доступных регистров, которые каким-то образом связаны с остальными компонентами и элементами процессора с целью выполнения операций, соответствующих системе команд данного МП. Можно, таким образом, полагать, что набор программно-доступных регистров и система команд – это главное, что нужно знать программисту о микропроцессоре, чтобы приступить к написанию программы.

4.3. Обзор перспективных проектов МПС на основе однокристальных комплектов БИС

В данном подразделе рассматриваются проекты МПС, созданные в 80-90х годах и послужившие основой для современных МПС на основе однокристальных МП.

В рассматриваемых классах МПС были применены новейшие достижения как технологий, так и новых принципов организации архитектур самих МП и МПС в целом.

МПС на основе 32-разрядного МП NS32032 представляет собой результат развития разработок фирмы National Semuiconductor в области МП, для которых характерна 32-разрядная внутренняя архитектура при 8- или16-разрядных шинах данных и интерфейса. Структура МПС на основе МП NS32032 представлена на рис. 4.4.

Рис. 4.4. Структура МПС на основе МП NS32032

МПС кроме МП NS32032 содержит следующие вспомогательные микросхемы:

- устройство управления временными состояниями(УУВС) NS32201;

- устройство управления памятью (УУП) NS32082;

- устройство обработки с плавающей запятой (УОПЗ) NS32081;

- устройство управления прерываниями (УУПр) NS32202;

В отличие от ситуаций с сопроцессорами, которые не способны декодировать свои собственные команды, при работе со вспомогательными процессорами УОПЗ и УУП центральный МП (ЦПУ) декодирует коды операций и останавливается на время пересылки команд и данных в эти процессоры, причем дополнительные строки программы на это не затрачиваются.

МПС на основе МП 80386 (рис. 4.5), представляющего собой 32-разрядную версию 16-разрядного МП 80286, содержит также сопроцессор математической обработки 80387, внутриплатную кэш-память с прямым отображением и двух- портовый контроллер памяти, обеспечивающий ЦПУ и системной шине возможность доступа к памяти через расширитель 32-разрядной локальной шины. В данной МПС реализуется обработка данных всех типичных видов (16-и 32-разрядных целых чисел, битовых команд, цепочек байтов, двоично-десятичных чисел), а если в состав системы включен сопроцессор 80387 – обработка 32-, 64- и 80-разрядных действительных чисел.

Рис. 4.5. Структура МПС на основе МП 80386

МПС на основе МП NCR/32 (рис. 4.6). Данный МП обладает уникальной способностью, заключающейся в возможности микропрограммного управления им с целью эмуляции набора команд других МП или МПС с использованием внешнего ППЗУ.

Рис. 4.6. Структура МПС NCR/32.

ЦПУ имеет две независимые мультиплексированные шины: 32-разрядную шину процессор-память, служащую для интерфейса основной памяти, портов ввода-вывода и других устройств, обеспечивающих работу системы, и 16-разрядную шину устройства хранения команд, которая осуществляет интерфейс с ППЗУ микропрограмм. Диапазон адресации составляет 16Мбайт прямо адресуемой реальной памяти и 128Кбайт прямо адресуемой памяти микрокоманд. Скорость пересылки данных по шине процессор-память превышает 50Мбайт/с. Доступном к шине управляет устройство арбитража приоритетов.

Устройство преобразования адресов выполняет функции управления при работе с реальной и виртуальной памятью, ведения учета астрономического времени, а также обнаружения и коррекции ошибок в системной памяти. Диапазон адресации виртуальной памяти составляет 4Гбайта. Устройство расширенной арифметики располагает полным набором арифметических операций ЭВМ класса IBM.

МПС ARM фирмы Accorn (Англия) предназначена для решения задач искусственного интеллекта и работы с языками высокого уровня и обладает наиболее характерными признаками компьютеров с сокращенным набором команд: небольшой аппаратно-реализованный набор команд; конвейеризация в архитектуре процессора; небольшие размеры СБИС; высокая пропускная способность памяти. МПС ARM (рис. 4.7) имеет 26-разрядную адресную шину и отдельную 32-разрядную шину данных с пропускной способностью памяти 18 Мбайт/c (при использовании пакетного режима скорость пересылки данных увеличивается на 30 %). Диапазон адресации составляет 64 Мбайт.

Рис. 4.7. Структура МПС ARM

Пересылками данных управляет ряд отдельных блоков, а не ПЗУ микропрограмм; дешифратор команд – программируемая логическая матрица. Благодаря широкому использованию конвейерных принципов обработки и налично группового сдвигателя производительность МПС достигает 3 млн. оп/с. Набор команд – это основные 44 команды пяти типов: “регистр-регистр”, арифметика и логика, загрузки и записи в память содержимого одиночного регистра и множества регистров, переходов.

МПС на основе МП μРD7281 NEC. ЦПУ данной МПС представляет собой конвейерный МП для обработки цифровых сигналов, специально предназначенный для этого вида обработки (восстановление, заполнение, сжатие, распознавание образов), а также для реализации быстрых преобразований Фурье и числовой обработки.

Этот МП является СБИС, в которой впервые воплощена потоковая архитектура. За счет применения ленточного принципа управления прохождением потоков и конвейерной архитектуры в МП достигается скорость обработки 5 млн. оп/с и при последовательном соединении нескольких МП производительность МПС возрастает почти линейно. Внутренний круговой конвейер состоит (рис. 4.8) из таблицы связей, функциональной таблицы, памяти данных, очередей и процессорного устройства.

Рис. 4.8. Структурная схема процессора μРD728

Метки, поступающие через контроллер ввода, передаются в таблицу связей и обрабатываются необходимое число раз в конвейере.

МПС “Канальная Лисп-машина (CLM )” фирмы “Texas Instrument”, являясь одним из первых 32-разрядных процессоров языков высокого уровня (Лисп), реализованных в виде одного кристалла, предназначена для решения задач искусственного интеллекта и баз данных. Как показано на рис. 4.9, CLM имеет традиционную фон-неймановскую структуру. Для обработки битовых полей предусмотрены сдвигатель и маскировщик, позволяющие осуществить циклические сдвиги на количество позиций до тридцати двух.

Рис. 4.9. Структурная схема машины CLM.

Около половины кристалла занимает встроенное ЗУПВ объемом более 114 Кбит. Микропрограммная память CLM имеет 16К 64-битовых слов, поэтому вместе с устройством отображения память размещена вне кристалла процессора.

На основе микропроцессора CLM могут быть построены системы обработки символов, которые могут быть использованы в качестве встроенных экспертных систем, таких, например, как интеллектуальные системы, принимающие решения при интерпретации изменяемых данных и диагностике своих собственных неисправностей.