Вычислитель аналогового сигнала

Министерство Образования Российской Федерации

Марийский Государственный Технический Университет

Кафедра ПП ЭВС

Вычислитель аналогового сигнала

Пояснительная записка к курсовому проекту

по предмету ПЦ и ПУ ЭВС

Выполнил: ст. гр. ЭВС-32у

Казанцев С.В.

Проверил:

Кошкин В.В.

Йошкар-Ола

2003

Аннотация

вычислитель аналоговый сигнал протокол

В настоящем курсовом проекте был разработан специализированный вычислитель для обработки аналогового сигнала. Данный вычислитель реализует ввод сигнала, отображение результата на индикаторе, накопление по каждому из каналов с усреднением по времени на интервале, определение среднеквадратического значения параметра, отбрасывание крайних значений, сравнение каждого сигнала по уровню с тремя значениями, вывод результатов по стандартному протоколу. Основанием для разработки является задание на курсовое проектирование.

Курсовой проект выполнен на листах, содержит чертежей.

Summary

In the present course project the specialized calculator for processing an analog signal was developed. The given calculator realizes input of a signal, display of result on the indicator, accumulation on each of channels with averaging on time on an interval, definition of meaning of parameter, rejection of extreme meanings, comparison of each signal on a level with three meanings, conclusion of results under the standard protocol. The basis for development is the task for course designing.

The course project is executed on sheets, contains of the drawings.

Задание на курсовой проект

Разработка специализированного вычислителя для обработки аналогового сигнала.

Число входных сигналов: аналоговых 2

Величина входного аналогового напряжения Uвх ±0,5 В

Максимальная основная частота входного сигнала 10 кГц

Максимальная длинна проводников до источника

первичного сигнала – не более 0,3 метров

Вывод информации – на цифровое табло,

число строк 2

число столбцов 6

Элементы индикации семисегментные индикаторы

Время формирования сигнала на выходе – не более 0,1 сек

Точность представления информации – не хуже 0,1%

Функциональная клавиатура.

Функции системы:

- ввод сигнала

- отображение результата на индикаторе

- накопление по каждому из каналов с усреднением по времени на интервале

- определение среднеквадратического значения параметра

- отбрасывание крайних значений

- сравнение каждого сигнала по уровню с тремя значениями

- вывод результатов по стандартному протоколу.

Содержание

1. Техническое задание

1.1 Введение

1.2 Основание для разработки

1.3 Технические требования

1.3.1 Состав изделия

1.3.2 Технические параметры

1.3.3 Принцип работы

1.4 Технические требования

1.4.1 Требования к надежности

1.4.2 Условия эксплуатации

1.4.3 Требования безопасности

2. Техническое предложение

2.1 Обзор литературы

3. Техническое проектирование

3.1 Разработка принципиальной схемы

3.1.1 Структурная схема устройства

3.1.2 Функциональная схема устройства

3.1.3 Принципиальная схема устройства

3.2 Проверочные расчеты

3.2.1 Расчет на потребляемую мощность

3.2.2 Расчет на нагрузочную способность

3.2.3 Расчет на задержку формирования сигнала

4. Программная часть

4.1 Разработка программы

4.2 Текст программы

Заключение

Список литературы

1. Техническое задание

1.1 Введение

Данное техническое задание распространяется на разработку схемы электрической принципиальной системы вычислителя, предназначенного для обработки аналогового сигнала и вывод результатов на цифровое табло.

1.2 Основание для разработки

Основанием для разработки является задание на курсовой проект по дисциплине "Проектирование центральных и периферийных устройств ЭВМ". Тема: "Вычислитель для обработки аналогового сигнала".

1.3 Технические требования

1.3.1 Состав изделия

Проектируемое изделие должно содержать следующие устройства:

Микроконтроллер, ОЗУ, ПЗУ, АЦП, табло 2 строки по 6 столбцов, должен содержать клавиатуру (12 клавиш), 2 входных аналоговых канала.

1.3.2 Технические параметры

Величина входного аналогового напряжения Uвх ±0,5 В

Максимальная основная частота входного сигнала 10 кГц

Время формирования сигнала на выходе – не более 0,1 сек

Точность представления информации – не хуже 0,1%

Объем памяти: ОЗУ – 128 Кбайт, ПЗУ – 32 Кбайт

Используемый тип микроконтроллера MCS–196

1.3.3 Принцип работы

Принцип работы данного устройства заключается в считывание информации в аналоговой форме по двум каналам, ее преобразовании, обработке (усреднение на интервале 5 сек, вычисление максимального и минимального разброса от среднего значения), хранении цифровых сигналов и выводом результатов на цифровое табло.

1.4 Технические требования

1.4.1 Требования к надежности

Надежность - это физическое свойство, которое зависит от количества и качества, входящих в изделие элементов, условий, в которых оно эксплуатируется. Надежность - это свойство прибора выполнять заданные функции и при этом сохранять свои параметры в заданных условиях эксплуатации и в течение определенного промежутка времени.

Показатели надежности должны соответствовать ГОСТ 25359-82.

1.4.2 Условия эксплуатации

Разрабатываемый вычислитель на базе контроллера MCS 8ХС196NT предполагается эксплуатировать в условиях УХЛ 4.2 ГОСТ 15150 - 69 при следующих условиях:

-температура окружающей среды от +1 до +50°С

-относительная влажность воздуха при температуре +50°С и ниже без конденсации влаги до 90%

-циклическое воздействие температур от +1 до +50°С

-атмосферное давление от 5.3 до 7.7 кПа от 400 до 790 мм.рт.ст.

Примечание: механические воздействия в данной курсовой работе не рассматриваются.

1.4.3 Требования безопасности

Требования безопасности должны соответствовать ГОСТ 12.2.006-87. Надежная работа вычислителя должна обеспечиваться выбором условий эксплуатации.

При эксплуатации вычислителя необходимо следить за правильностью распайки выводов разъемов и обеспечением их механического крепления, а также надежного заземления всего изделия в целом.

При пайке выводов микропроцессора и других микросхем следует принимать меры исключающие повреждение из-за перегрева, механических усилий, статического напряжения.

2. Техническое предложение

2.1 Обзор литературы

Рассмотрим несколько информационно-вычислительных систем, послуживших при проектировании аналогами создаваемой системы сбора информации. Пример опроса MIDI-клавиатуры, обрабатываемой однокристальной микро-ЭВМ К1816ВЕ35.

Микро-ЭВМ – это устройство, занимающееся обработкой информации и управлением работы частей MIDI-клавиатуры. Она имеет специальные двунаправленные выводы, позволяющие создать совмещенную шину адреса/данных, и порт ввода/вывода, к которому подключен блок клавиатуры.

Блок клавиатуры состоит из набора клавиш, которые последовательно опрашиваются сигналами с порта ввода/вывода микро-ЭВМ. При нажатии клавиши выставляется сигнал, вызывающий прерывание программы микро-ЭВМ. По этому прерыванию сигналы, установленные на выводах порта, запоминаются в памяти микро-ЭВМ, и далее используются как код нажатой клавиши.

Генератор вырабатывает и выдает на соответствующие входы микро-ЭВМ тактовые сигналы заданной частоты.

Схема выборки адреса выделяет и сохраняет сигналы адреса во время цикла совмещенной шины адрес/данные.

Считывание с ППЗУ производится через шину адреса/данных под управлением специальных сигналов микро-ЭВМ.

Через MIDI-выход осуществляется передача цифровой кодированной информации на проигрывающее устройство.

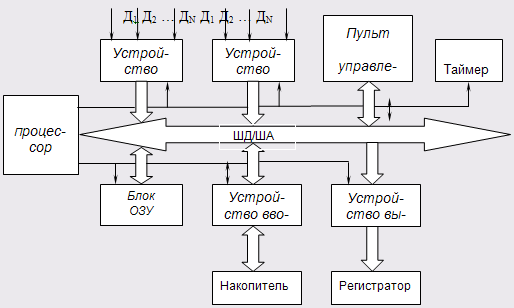

В качестве первого примера структурной схемы контроллера была выбрана структурная схема автоматизированной системы контроля (АСК) [1].

В таких системах необходимая информация об объекте контроля, формируется с помощью измерительных датчиков, установленных на нем. В микропроцессорных автоматизированных системах контроля выполняется обработка и промежуточное хранение информации, как в едином измерительном блоке системы, так и в местах, максимально приближенных к источнику информации.

Структурная схема АСК централизованного типа с внутренней магистралью приведена согласно рисунку 1.

Принцип объединения компонентов микроЭВМ и периферийных устройств с помощью общей магистрали позволяет легко модифицировать систему в соответствии с конкретными потребителями. Каждое устройство подключается к магистрали с помощью стандартного интерфейса. Основу схемы АСК составляет процессор, выполняющий функции преобразования поступающей с внешних датчиков (Д>1>…..Д>N>) информации и ее распределение по оконечным узлам.

АСК может быть выполнена на основе серийно выпускаемой микроЭВМ с собственной памятью данных, либо специализированная микроЭВМ, которая дополняется блоком ОЗУ, где хранятся информационные массивы, участвующие в обработке. Тип микропроцессорных схем и конкретные характеристики проектируемой системы накладывают особенности на структуру процессора.

Интерфейсные блоки - устройства ввода и устройство вывода ориентируются на стандартную форму обмена информацией по магистрали. В накопителе полученная информация сохраняется длительное время, а при регистраторе документируется. Пульт управления и контроля необходим для задания режима работы АСК, оперативного контроля хода измерений и, при необходимости, вмешательства в процедуру обработки информации.

Таймер синхронизирует работу всей системы, и его сигналы могут служить метками реального времени.

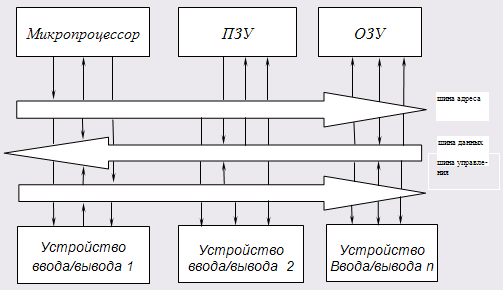

В качестве второго примера была выбрана схема одноплатного микроконтроллера мМС1204 [2], которая приведена согласно рисунку 2.

Рисунок 1 - Структурная схема АСК централизованного типа.

Базовой моделью семейства является микроконтроллер мМС1200 [3], который представляет собой законченную одноплатную МС общего назначения с магистрально-модульной архитектурой открытого типа. Основой МС служит шина И41 [3]. На плате отсутствуют какие-либо средства для реализации специальных функций, ориентированных на конкретные применения. Специфичность и разнородность таких средств привели бы к перегрузке платы и ее не эффективному использованию. Поэтому основное внимание было уделено интегрированию действительно универсального базового набора программно-аппаратных средств, обладающего функциональной завершенностью и обеспечивающего применение микроконтроллера в качестве ядра информационных систем.

Рисунок 2 - Схема одноплатного микроконтроллера мМС1204

В состав микроконтроллера входят: 8-разрядный процессор, ПЗУ, ОЗУ, два последовательных интерфейса типа ИРПС и параллельный интерфейс типа ИРПР. Системный таймер (СТ) совместно с 8-уровневой системой прерываний (СП) обеспечивает поддержку режима реального времени, который характерен для многих применений микроконтроллера. Внутрисистемная магистраль организует многоплатные расширения микроконтроллера с помощью специальных и системных модулей, таких как модуль аналогового ввода или системная память соответственно.

В [1] найдена структурная схема вычислителя на базе заданного процессора поясняющая принцип действия микроЭВМ, которая представлена согласно рисунку 3.

Схема включает следующие узлы:

-микропроцессор;

-блоки ПЗУ и ОЗУ;

-блоки устройств ввода/вывода.

Микропроцессор выставляет на шину адреса (ША) адрес того блока, к которому необходимо обратиться во время той или иной фазы. Вместе с этим на шину управления (ШУ) выставляется управляющий код, необходимый для настройки блока по выставленному адресу. Например, для задания режима чтения ОЗУ необходимо на шину адреса выставить адрес необходимой ячейки ОЗУ, а на шину управления подать сигнал RD.

Рисунок 3

По шине данных (ШД) происходит обмен данных между микропроцессором и блоками вычислителя. Данные пересылаются после установки адреса на шине адреса и сигналов управления на шине управления.

Количество устройств ввода-вывода в вычислителе может быть различным. Их присутствие в микроЭВМ обязательно, так как при их отсутствии отпадает необходимость в самом вычислителе. Для обмена информацией между микроЭВМ и устройствами ввода-вывода также необходимо адресовываться к ним и посылать управляющие коды по шинам.

Ввод сигнала, его представление в дискретную форму, проводится с учетом требуемого интервала дискретизации, определяемого теоремой Котельникова, согласно формуле (1). Величина t определяет временной интервал только для одного сигнала.

(1)

(1)

где f>B> - верхняя гармоника сигнала, Гц

(2)

(2)

где f>0> - частота сигнала, Гц

Быстродействие АЦП составит 25 мкс. Разрядность АЦП определим исходя из погрешности представления информации >ПР>

(3)

(3)

Определим число разрядов АЦП исходя из формулы (4)

(4)

(4)

где n - число разрядов

Тогда

Выбираем АЦП с разрядностью n=12 и частотой f МГц.

Выбираем АЦП AD 1671 по [9], у которого n=12, f= МГц.

Расчет ОЗУ произведем следующим образом

(5)

(5)

где m - количество каналов;

t - временной интервал накопления, с

t зададимся 0,1 с., тогда количество измерений на интервале будет состовлять 0,1/25 10 -6=4000.

Таким образом, ОЗУ составит 128 КБайт. Выбираем микросхему

В соответствии с техническим заданием информационно-вычислительная система обработки сигналов должно состоять из следующих устройств: микроконтроллер, ПЗУ, ОЗУ. Клавиатура - 12 функциональных клавиш, устройство ввода аналогового сигнала (подсистема ввода сигнала), LPT-порт и семисегментная индикация, состоящего из 6 столбцов, 2 строк.

Устройство ввода аналогового сигнала имеет два входа, где аналоговый сигнал преобразуется в цифровой код, выставляется на шину данных. Далее эти данные записываются в ячейку памяти ОЗУ для накопления и хранения информации. Сигналы шины адреса фиксируется в регистре адреса. После обработки информации выводится на информационное табло собранное на семисегментных индикаторах.

ПЗУ предназначено для хранения команд программы.

Оперативное управление работой системы осуществляется с клавиатуры.

3. Техническое проектирование

3.1 Разработка принципиальной схемы

3.1.1 Структурная схема устройства

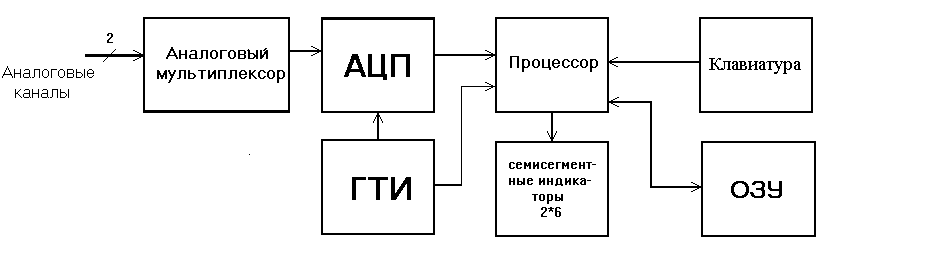

Структурная схема представлена на рисунке 1.

Рисунок 1. Схема структурная.

Устройство содержит процессорный блок, к встроенным портам которого подключен порт клавиатуры. Через совмещенную шину адреса/данных подключается АЦП - имеющий 2 аналоговых входа, внешнее ОЗУ и блок отображения информации. Сигналы шины адреса фиксируются в регистрах адреса по сигналу ALE.

АЦП управляется специальными сигналами микроконтроллера, ОЗУ – встроенным в микроконтроллер блоком управления внешней памяти, блок отображения – непосредственно сигналами с шины адреса и шины данных.

3.1.2 Функциональная схема устройства

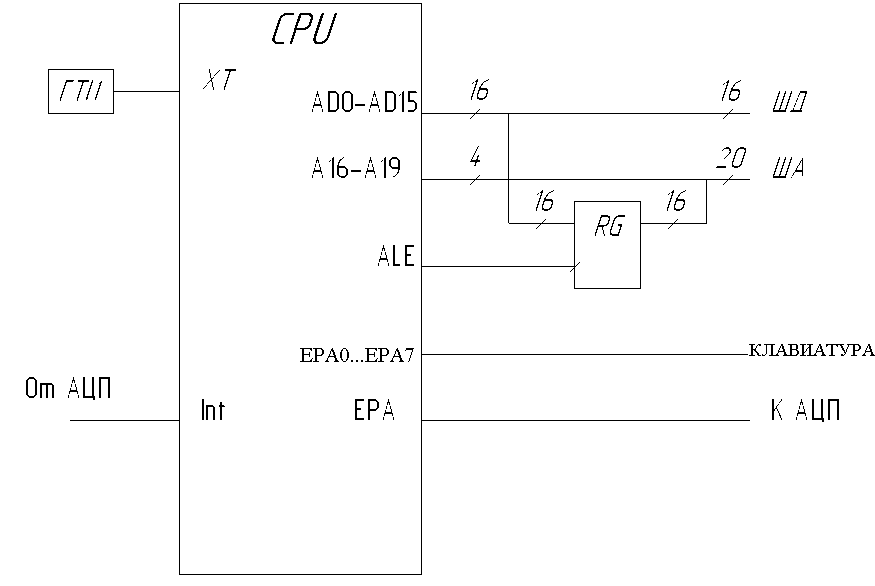

Процессорный блок (Рисунок 2) обеспечивает преобразование полученной информации, управление режимами работы периферийных устройств, инициализацию всего устройства по включении питания.

Основным устройством этого блока является микроконтроллер. Он включает в себя 20-битный центральный процессор, который соединен с контроллером прерываний и с контроллером памяти через 16-битную внутреннюю шину CPU. Расширение этой шины соединяет CPU со встроенными периферийными модулями Дополнительно: по 8-битной шине CPU передаются командные биты от контроллера памяти к регистру команд в регистровом арифметическом устройстве. Тактовую частоту микроконтроллера задает внешняя генерирующая цепочка с кварцевой стабилизацией. Она подключается к его входам XTAL1 и XTAL2. Сброс устройства осуществляется подачей низкого уровня напряжения на вход "RESET". Используемыми при построении системы сбора информации встроенными периферийными модулями микроконтроллера являются: один однонаправленный (вывод) и два двунаправленных восьмиразрядных порта ввода/вывода, программируемый таймер, модуль высокоскоростного ввода/вывода (HSIO), встроенное ПЗУ на 32Кбайт.

Рисунок 2. Процессорный блок.

Два порта ввода/вывода используются в качестве мультиплексированной 16-разрядной шины адреса/данных (сигналы AD0-AD15), которые сами настраиваются на этот режим при включении питания.

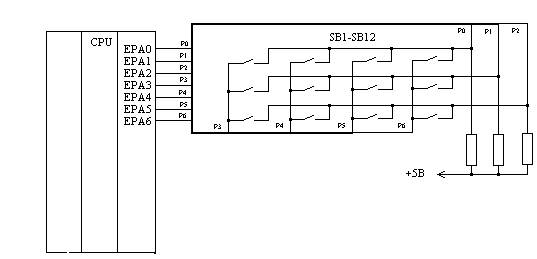

Для формирования сигнала адреса для ОЗУ и внешних устройств используется регистр адреса, запись в который происходит при активном уровне сигнала ALE. Блок клавиатуры подключается через встроенные порта ввода-вывода процессора.

Рисунок 3. Подключение клавиатуры.

Данные с них считываются при обращении вычислителя к порту.

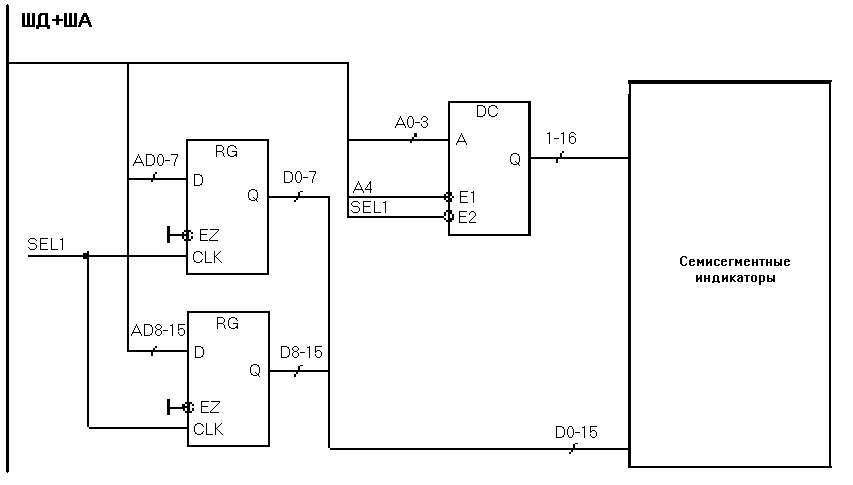

Блок отображения информации (Рисунок 4) осуществляет вывод данных на семисегментные индикаторы, состоящие из 2 строк и 6 столбцов.

Рисунок 4. Блок отображения информации.

Отображение производится следующим образом: при обращении к соответствующему порту, ПЛМ преобразует поступившую с регистра адреса информацию в сигнал управления SEL1, переводит в активное состояние регистры данных и тем самым разрешает включение разрядов отображаемого символа на индикаторах. Одновременно код с регистров адреса поступает на входы дешифраторов, работа которых также разрешается сигналом SEL1. Запись в дешифраторы осуществляется за два цикла обмена, в зависимости от состояния линии А4 включается дешифратор. В зависимости от поступившего адреса дешифраторы включают тот или иной индикатор.

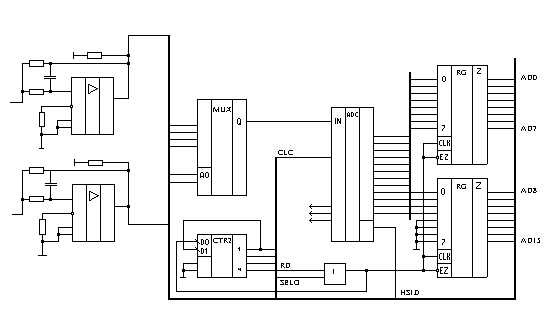

При работе с АЦП (Рисунок 5) микроконтроллер переходит на адрес 030000, по которому в адресном пространстве системы подразумевается 16-битная ячейка памяти, предназначенная для хранения преобразованного цифрового кода одного из входов АЦП.

Рисунок 5. Блок ввода аналоговой информации.

Сигналы адреса поступают на вход ПЛМ, которая отслеживает соответствие его диапазону адресов, выделенных для АЦП, и преобразует сигналы шины адреса в сигнал SEL0, управляющий счетчиком с одновременным чтением состояния АЦП, передающим адрес аналоговому мультиплексору. Аналоговый сигнал проходит через соответствующую схему коррекции, которая согласовывает уровень и форму входящего сигнала так, чтобы он имел наименьшие искажения, на вход АЦП.

На вход CLC АЦП поступает тактовая частота, получаемая с процессора. Происходит запуск подпрограммы обработки прерывания. Подпрограмма осуществляет проверку готовности данных АЦП по сигналу готовности преобразования (выход ГТ), который поступает на вход "HSI.0" блока HSIO. Если данные готовы, то по сигналу RDA (сигнал RD, разрешенный сигналом SEL0) происходит чтения с шины данных преобразованного значения, выставляется адрес следующего аналогового входа, и запускается программируемый таймер, который через несколько тактов обращается к порту запуска АЦП, разрешая тем самым преобразование входного сигнала. Процесс повторяется. Выходной регистр АЦП выдает преобразованный код на шину данных только по сигналу "RD" микроконтроллера.

При необходимости выборки и преобразования сигнала с максимальной заданной частотой со всех аналоговых входов микроконтроллер вынужден обращаться к АЦП через:

t=1/(2*fmax)=1/(2*100)=5 мкс;

где t-период обращения, рассчитывается по теореме Котельникова.

fмах=200кГц; - максимальная частота сигнала;

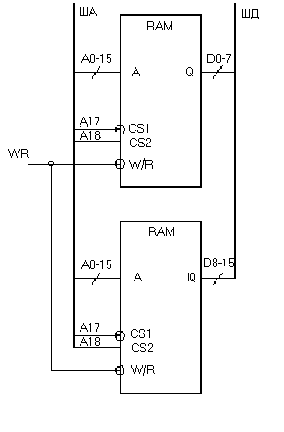

Работа микроконтроллера с внешней ОЗУ (рис.6) осуществляется с помощью встроенного контроллера внешней памяти, выставляющего сигналы записи WR, сигналы А17, А18 и сигнал ALE наличия на шине адреса/данных сигналов адреса.

Рисунок 6. Внешнее ОЗУ.

Обмен информацией между микроконтроллером и ОЗУ идет по шине адреса/данных частями, по машинному слову в 16 бит. При формировании адреса сигналы адреса фиксируются в регистре адреса и подаются на адресные входы микросхем ОЗУ. Чтение и запись данных в ОЗУ производится по одним и тем же выводам. Запись сопровождается подачей на соответствующий вход ОЗУ сигнала "WR", а его неактивное состояние подготавливает ОЗУ для считывания. Код адреса по сигналу ALE сохраняется в специальных регистрах, которые удерживают его на входах ОЗУ в то время, когда на совмещенной шине адреса/данных выставлены данные. ОЗУ активизируется только тогда, когда на шину выставляется адрес, содержащий в старшем, А17 разряде слова адреса "1" (выбора кристалла CS2) и в А18 (А19) разряде слова адреса "0". При установление иных значений А17 и А18 обмен с ОЗУ запрещается, тем самым предотвращая конфликты с дешифратором адреса. Карта распределения адресного пространства проектируемого устройства представлена в таблице 1.

Таблица 1. Карта распределения адресного пространства.

|

07FFFFH 040000H |

Память данных 128кбайт |

|

00FFFFH 00C000H |

Не используется |

|

00B002H 00B001H 00B000H |

Чтение цифровых входов Запуск АЦП Чтение АЦП |

|

00AFFFH 00A000H |

Порты индикатора |

|

009FFFH 002000H |

Внутреннее ПЗУ 32кбайт |

|

001FFFH 001F00H |

Внутренние спецрегистры |

|

001EFFH 000600H |

Не используется |

|

0003FFH 000100H |

Внутреннее ОЗУ |

|

0000FFH 000018H |

Регистровое ОЗУ |

|

000017H 000000H |

Спецрегистры процессора |

2.1.3 Принципиальная схема

Аналоговые сигналы поступают через разъем XS1 и резисторы R1, R5 на выводы 2 операционных усилителей DA1…DA2. Операционные усилители усиливают сигналы приблизительно в 10 раз, после чего они поступают на входы D аналогового коммутатора DD2. В зависимости от того, какой адрес выставлен на адресном входе А0..А3, один из 2 сигналов поступает на его выход Q (в.32 DD4). Резисторы R1…R4, R5…R8 предназначены для установки коэффициента усиления операционных усилителей. Резисторы R1…R6 служат для балансировки операционных усилителей.

Сигнал, поступающий на вход IN АЦП (в.15 DA3) преобразовывается в цифровой код. Преобразование происходит при поступлении импульсов на вход CLC от процессора DD4. После окончания преобразования на выходе RAD (в.7 DA3) появляется логическая "1", поступающая на вход SCO процессора. С выходов D0…D11 АЦП цифровой код поступает на регистры "защелки" выполненных на микросхемах DD5, DD6. Регистры записывают и содержат достоверную информацию при наличии на входах CLK и EZ (в.11, 1 DD5, DD6) сигнала RDA. Сигнал RDA формируется логическим сложением микросхемой DD1.2 сигналов RD (чтение процессором из внешнего источника) и SELO (выбор порта). Все остальное время выходы регистров находятся в третьем состоянии для устранения искажений информации. С выходов регистров информация поступает на входы AD для обработки и хранения в ОЗУ. Номер канала устанавливается циклически по сигналу чтения АЦП путем подачи на вход счетчика DD3. Разрешение записи в регистр осуществляется сигналом SELO и происходит во время действия сигнала чтения АЦП.

Накапливаемая контроллером информация хранится в шестнадцатиразрядном ОЗУ, организованной в две "страницы" объемом по 128 Кбайт. Обмен с ОЗУ производится за два шинных цикла. Во время первого цикла на выводы AD0…АD15 процессора DD4 выставляется адрес, который фиксируется в регистрах адреса выполненных на микросхемах DD7, DD8. Фиксация адреса происходит при выставлении процессором сигнала на выходе ALE, который подается на входы CLK микросхемы регистров адреса (в.11 DD9, DD10). После снятия сигнала CLK на выходах Z регистров остается адрес в ОЗУ, который подается на адресные входы микросхем памяти DD10, DD11. Во время второго цикла процессор выставляет сигнал WR, поступающий на входы W/R микросхем ОЗУ (в.29 DD10, DD11), на выводы AD0…АD15 информацию, которая подается на выводы DIO и производит запись информации в ОЗУ. Если сигнал WR не выставляется процессором, ОЗУ находится в режиме "чтение" и процессор может считывать данные, поступающие на выводы AD0…AD15. Сигналы с выводов А17…А19 так же подаются на входы ОЗУ CS2 и CS1 (DD3, DD7) и CS1 (DD8, DD14) соответственно. При наличии логической "1" на линии А17 и логического "0" на линии А18 разрешается чтение или запись в первую "страницу" памяти (DD3, DD7). При наличии логической "1" на линии А17 и логического "0" на линии А19 разрешается запись или чтение во вторую "страницу" памяти (DD8, DD14). При наличии логического "0" на линии А17, ОЗУ блокируется и производится запись адреса в дешифратор адреса DD2.

Дешифратор адреса собран на микросхемах DD2, DD1.1 и DD1.2. Сигналы с выходов процессора А17…А19 поступают на выводы 1, 2 DD1.1 и вывод 5 DD1.2 соответственно. При наличии на этих выводах логического "0", на выводе 6 DD1.2 появляется строб импульс обращения к порту, подающий на вход CS микросхемы DD2. На линиях AD0…AD15 процессор выставляет адрес порта, который подается на адресные входы DD2. На выходах D0 микросхемы DD4 появляется управляющий сигнал SEL0…3, соответствующий выбранному порту.

Индикатор собран на семисегментных индикаторах 2х6. Процессор выставляет адрес на линиях АD0-4, записывает его в регистр адреса. При обращении процессора к порту индикатора DD2 выставляет на выводе 17 сигнал SEL1. Параллельно сигналы с линий AD0-15 записываются как отображаемая информация в регистры DD13 и DD14. Запись производится при наличии на входах CLK регистров сигнала SEL1. Одновременно по сигналу SEL1 адрес из регистра адреса поступает на дешифратор DD12, который, дешифруя поступившую на вход информацию, выбирает необходимый столбец для отображения информации. Информация из регистров DD13 и DD14 подается на индикаторы, включение которого происходит от дешифратора.

Цепь питания +5В содержит семь блокировочных конденсаторов C3-9, по одному на каждые три микросхемы, предназначенных для фильтрации помех, свойственных цифровым схемам.

3.2 Проверочные расчеты

3.2.1 Расчет потребляемой мощности

Расчет потребляемой мощности производится по формуле:

где: P>n> – мощность, потребляемая микросхемой или иной радиодеталью, Вт; n – количество радиодеталей.

Таблица 2

|

Тип микросхемы |

Потребляемая мощность, мВт |

Количество корпусов |

|

AD1671 |

350 |

1 |

|

591КН3 |

30 |

1 |

|

140УД6 |

75 |

2 |

|

8XC196NT |

1000 |

1 |

|

61256 |

300 |

2 |

|

1533ИЕ5 |

75 |

2 |

|

1533АП6 |

120 |

1 |

|

1533ЛН1 |

270 |

1 |

|

155ЛЛ2 |

300 |

1 |

|

1533ИР22 |

275 |

7 |

|

1533ИД3 |

75 |

2 |

|

PPI |

200 |

1 |

|

PLM |

130 |

1 |

Р>max>=0,35*1+0,030*1+0,075*2+1*1+0,3*2+0,075*2+0,12*1+0,27*1+

0,3*1+0,275*7+0,075*2+0,2*1+0,13*1=5,375 Вт

Полученное значение потребляемой мощности является приемлемым.

3.2.2 Расчет на нагрузочную способность

Наиболее нагруженным элементом является процессор. Основное число потребителей его сигнала подключено к линиям AD. Максимальное число входов, подключаемых к одному выходу достигает 2 в двух режимах: отображение информации на индикаторе и обмен с ОЗУ. Максимальный ток, который может отдавать один выход процессора – 25 мА. Ток потребляемый входами микросхем: 1533ИД3 – 1,7 мА; 1533ИР22 – 1,5 мА; 61256 – 2 мА;

При отображении на индикаторе потребление от одного входа составляет: 1,5+1,7=3,2 мА что является удовлетворительным, так как значительно меньше максимально допустимого. При обмене с ОЗУ ток потребления составляет: 1,5+2=3,5 что также является удовлетворительным.

3.2.3 Расчет на время распространения сигнала

Важным и наиболее затратным по времени является обмен с портами. Сигналы распространяются по нескольким путям, при этом может возникнуть ситуация "гонки по тракту". Наиболее критичным выберем чтение информации из АЦП процессором, так как при несоблюдении ограничений, накладываемых используемой элементной базой возможны серьезные искажения информации. Тактовая частота процессора составляет 20МГц. Тогда период обмена по шине составляет 0.05 мкс. Расчет времени распространения сигнала по цепи производится по формуле:

;

;

где: t>З>>n> – время задержки прохождения сигнала через микросхему, нс.

;

;

где: t>Ф> – время нарастания сигнала, нс; t>В> – время выдержки информации, нс.

Время распространения сигнала по цепи обращения к порту составляет:

Время распространения сигнала от шины процессора до регистра АЦП превышает время шинного цикла. Так как чтение информации происходит во время второго шинного цикла, данная ситуация не противоречит условиям нормальной работы схемы.

3.3 Программная часть

3.3.1 Разработка программы

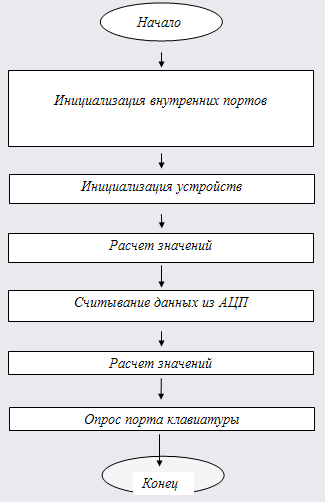

Рисунок 7 – алгоритм основной программы

Рисунок 8 – алгоритм обработки прерываний

3.3.2 Текст программы

Инициализация устройства

Init:

Ldb 2018H,#11000110b ; Загрузка конфигурации кристалла Ldb14H, 00H

Ldb P5_MODE, 00H ; Стандартный ввод/вывод

Ldb P5_DIR, FFH ; Выход с открытым стоком

Ldb P5_REG, #10010010 ; Направление ввода/вывода

Ldb P1_REG, #0001110b ;Настройка порта клавиатуры на в/в

Nop

Nop

EI

RET ;Конец инициализации;

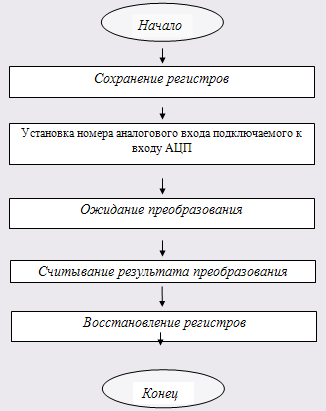

Обработка ввода с АЦП

Inp:

Pusha ;Сохранение регистров

Push AX, BX, CX, DX, FX

Stb B000H,#00000000b ;Установка номера входного канала

Nop ; Задержка на преобразование .

Nop

Ld AX,(B002H); Чтение данных из АЦП

Ld (10000H),AX; Запись в память данных

Nop

Pop FX, DX, CX, BX, AX; Восстановление регистров

Popa

RET;

Конец ввода

Заключение

В данной работе были рассмотрены разные варианты схемной реализации вычислителя выполненного на микропроцессоре MCS 8ХС196NT. Проведен анализ и выбор решения, соответствующего требованиям технического задания, а также его обоснование. На основании проведенного анализа можно сделать вывод, что принятое схематическое решение оптимально и соответствует всем требованиям, оговоренным в техническом задании на разработку.

Список использованной литературы

1. В.В. Кошкин и др. Микропроцессоры в конструкциях и технологии производства ЭВА//Учебное пособие; Й-Ола, 1987г.

2. Справочник "Отечественные микросхемы и зарубежные аналоги" Перельман Б.Л., Шевелев В.В.

3. М. Гук "Энциклопедия: Аппаратные средства IBM PC" Санкт-Петербург: Питер, 2000.

4. М. Айден "Аппаратные средства PC" Санкт-Петербург: Питер, 2-е изд.

5. Справочник "Применение цифровых микросхем серии ТТЛ и КМОП" Бирюков С.А.

6. "Проектирование цифровых устройств на однокристальных микроконтроллерах" В.В.Сташин, А.В.Урусов, О.Ф.Мологонцева.

7. Richard N. Evans, Christine Neffenger "Using the 8XC196NT: application note" Intel, 1994.

8. "8XC196NT Chmos microcontroller with 1 Mbyte linear address space" Advance information, Intel, 1996

9. Analog Digital//Справочник; 1997г.