Моделирование работы приемника циклового синхросигнала аппаратуры ЦСП

Пермский Государственный Технический Университет

Электротехнический факультет

Кафедра: Конструирование радиоэлектронных средств

КУРСОВОЙ ПРОЕКТ

по курсу Основы радиоэлектроники и связи

«Моделирование работы приемника циклового синхросигнала аппаратуры ЦСП»

Выполнил: ст. гр. КРЭС-06

Журавлёв А.А.

Проверил: Тунев Д. Г.

Пермь 2009г.

Оглавление

Введение

Структура цикла аппаратуры ИКМ-30

Приёмник циклового синхросигнала

САПР МАХ+plusII фирмы ALTERA

Работа над проектом

Описание элементов схемы

Сборка проекта

Моделирование работы схемы проекта

Выводы

Литература

Введение

В настоящее время всё более широкое распространение получают цифровые методы передачи и обработки информации. В большинстве развитых стран выпускается и постоянно совершенствуется оборудование для цифровых систем передачи (ЦСП), основанных на принципах импульсно-кодовой модуляции (ИКМ), предназначенных для передачи информации по городским соединительным линиям между АТС, а также по междугородним линиям связи.

Цифровой сигнал в отличие от аналогового нуждается в синхронизации, т.к. информация передаётся пакетами, для правильного приёма которых необходимо знать, где начало и конец очередного пакета. Неправильный приём пакета ведет к потере информации. Для обеспечения синхронизации применяются специальные приёмы кодирования и строятся дополнительные устройства. Одним из таких устройств является приёмник циклового синхросигнала. Он пропускает через себя ИКМ сигнал и отыскивает в нём синхропоследовательности, а также обеспечивает автоматический поиск синхронизма и выводит ошибки, если синхронизм не найден.

Раньше всё приемо-передающее оборудование строилось на отдельных цифровых логических микросхемах, размещенных на печатных платах, которые выполняли каждая свою функцию и размещались на стойке. Сейчас, с появлением программируемых логических интегральных схем (ПЛИС) высокой степени интеграции, стала возможна наиболее компактная реализация той же аппаратуры. Широко используются ПЛИС фирмы ALTERA как за рубежом, так и в нашей стране. С их помощью можно реализовать множество схем, как комбинационных, так и схем с памятью. Для разработки, отладки и прошивки схемы используется САПР ALTERA MAX+plusII и QuartusII. В настоящее время Altera поддерживает только QuartusII, но проектирование в MAX+plusII понятнее и проще для начинающих. Система может выполнять все операции, начиная от разработки идеи, до прошивки готового, отлаженного проекта в реальную микросхему, которая впоследствии будет выполнять заданную функцию.

Структура цикла аппаратуры ИКМ-30

Временной спектр многоканального цифрового сигнала Системы ИКМ-30 состоит из последовательно следующих друг за другом циклов длительностью 125мкс (чётных – ЦЧ и нечетных - ЦН).

Циклы разделяются на 32 канальных интервала (КИ), каждый из которых содержит по 8 тактовых интервалов (разрядов).

Один из КИ, нумеруемый КИ0, используется для передачи синхросигнала. Синхросигнал в системе ИКМ-30С-4 следует считать распределенным, состоящим из сосредоточенной группы 0011011, передаваемых в тактовых интервалах Р2-Р8 КИ0 в циклах называемых чётными, и символа «1», передаваемого в тактовом интервале Р2 КИ0 в циклах, называемых нечетными. Таким образом, имеет место чередование значений символа, передаваемого в тактовом интервале Р2 КИ0 каждого цикла. Использование такого синхросигнала рекомендовано МККТТ и позволяет резко уменьшить вероятность ложного синхронизма при передаче по цифровым каналам «медленно» изменяющейся информации.

В тактовом интервале Р3 КИ0 нечетных циклов передаётся на противоположную станцию аварийный сигнал – сигнал «Извещение».

Приёмник циклового синхросигнала

Система цикловой синхронизации предназначена для восстановления и удержания состояния циклового синхронизма между передающей и приёмной частями цифровых систем передачи. Она состоит из передатчика и приёмника синхросигнала. Передатчик формирует в передающей части кодовую группу определенной структуры, расположенную в начале цикла передачи. В приёмнике осуществляется распознавание кодовых групп, структура которых совпадает со структурой синхросигнала, и принимается решение о принадлежности опознанных кодовых групп передаваемому синхросигналу. При обнаружении циклового синхросигнала производится фазирование генераторного оборудования приёмной части. В соответствии с этим приёмник циклового синхросигнала включает в себя опознаватель синхросигнала, накопители по выходу из синхронизма и по входу в синхронизм, а также схемы управления генераторным оборудованием и накопителями.

Необходимо, чтобы восстановление состояния синхронизма происходило как можно быстрее, а затем удерживалось как можно дольше. Противоречивость этих требования заключается в том, что высокая помехоустойчивость системы цикловой синхронизации (определяется длительностью удержания состояния синхронизма) достигается включением накопительных устройств, которые замедляют процесс восстановления синхронизма. Следовательно, чем выше помехоустойчивость системы цикловой синхронизации, тем дольше длится процесс восстановления синхронизма. Поэтому в системах синхронизации выбирается минимальная ёмкость накопительных устройств, обеспечивающая требуемую помехоустойчивость.

Цифровая Система Передачи ИКМ-30 представляет собой комплект оборудования, состоящий из отдельных функциональных блоков. Так приёмник циклового синхросигнала данной системы выполнен на плате ЦО-12, которая входит в состав блока АЦО-11 и выполняет помимо поиска и удержания синхронизма следующие функции:

формирование цифровых сигналов с определенной сеткой частот, управляющих процессом обработки цифровых и аналоговых сигналов в приёмной части блока АЦО-11;

разделение принятого многоканального сигнала;

приём сигнала «СИАС», приём сигнала «Извещение» об аварийном состоянии противоположной станции;

формирование сигнала установки цифрового оборудования передачи ЦО-11;

Также плата ЦО-12 обеспечивает поиск состояния циклового синхронизма при включении блока АЦО-11. Коэффициент накопления по входу в синхронизм = 2; среднее время вхождения в состояние циклового синхронизма не более 2мс; коэффициент накопления по выходу из синхронизма = 4.

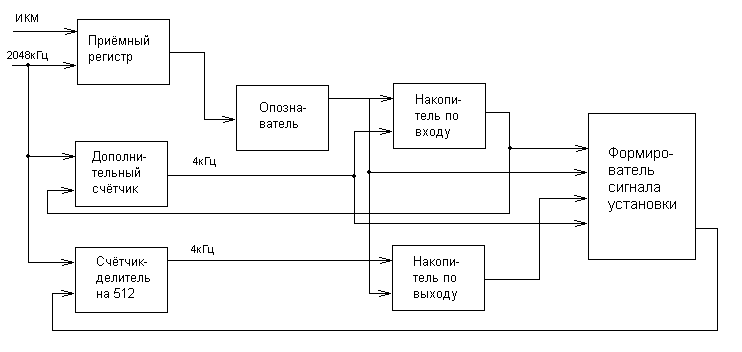

Рисунок 1

Рассмотрим подробно работу приёмника циклового синхросигнала ЦСП ИКМ-30(см. рис. 1). Многоканальный цифровой сигнал ИКМ и тактовая частота 2048кГц поступают с выходов платы BC-11 на входы восьмиразрядного последовательного регистра приёмника синхросигнала. С выходов регистра многоканальный цифровой сигнал в параллельном коде поступает на входы опознавателя.

Опознаватель осуществляет выделение из принятого сигнала синхрокомбинации вида 0011011. Вход опознавателя подключен к входам накопителей по входу и выходу, а также ко входу формирователя сигнала установки.

Накопитель по выходу представляет собой четырёхразрядный сдвиговый регистр, и сигнал с выхода опознавателя записывается в этот регистр с частотой 4кГц. Процесс записи формируется сигналом, формируемым счётчиком-делителем на 512, на вход которого поступает сигнал тактовой частоты 2048кГц.

При наличии циклового синхронизма все триггеры сдвигового регистра накопителя по выходу находятся в состоянии, соответствующему приёму четырех последовательно поступивших синхрокомбинаций. Если синхронизм по какой-либо причине потерян, в сдвиговый регистр накопителя по выходу записывается информация об отсутствии синхрокомбинации на должном месте, и, при накоплении четырёх сигналов об отсутствии синхрокомбинаций, на выходе накопителя по выходу появляется сигнал об отсутствии синхронизма, поступающий на вход формирователя сигнала установки и на вход устройства контроля.

Сигнал с выхода опознавателя записывается также в двухразрядный сдвиговый регистр накопителя по входу, частота записи 4кГц, но, в отличие от накопителя по выходу, сигнал записи формируется дополнительным счётчиком, аналогичным счётчику-делителю на 512.

При синхронной работе ЦО-12 счётчик-делитель на 512 и дополнительный счётчик работают синфазно, однако, при потере синхронизма, первая неправильно принятая синхрокомбинация (точнее отсутствие её на должном месте) вызывает процесс поиска синхронизма. При поиске синхронизма дополнительный счётчик останавливается, и на вход накопителя по входу поступает тактовая частота 2048кГц. Накопитель по входу анализирует выходной сигнал опознавателя, и, при поступлении на вход опознавателя синхрокомбинации, разрешает работу дополнительного счетчика. Через цикл (256 тактов с частотой 2048кГц) производится анализ на позиции Р2 принятой кодовой комбинации.

Если этот сигнал не равен «логической единице», то дополнительный счётчик сбрасывается, и процесс поиска начинается заново; в противном случае накопитель по входу анализирует выход опознавателя через два цикла после приёма синхрокомбинации. Правильно принятая синхрокомбинация означает, что дополнительный счётчик работает синхронно с принимаемым многоканальным цифровым сигналом.

После того, как накопитель по выходу зафиксирует выход из синхронизма, а накопитель по входу фиксирует нахождение нового положения синхросигнала, формирователь сигнала установки (при получении сигнала с выхода опознавателя) сформирует импульс, устанавливающий счётчик-делитель на 512 в нужную фазу и синхронизм ЦО-12 восстанавливается. Функциональная схема приёмника циклового синхросигнала аппаратуры ИКМ-30С-4 находится в приложениях(приложение №2).

САПР МАХ+plusII фирмы ALTERA

САПР MAX+plusII представляет собой архитектурно независимую среду проектирования, которая легко приспосабливается к конкретным проектным требованиям и может работать на различных компьютерных платформах. MAX+plusII предоставляет различные способы ввода проекта, быструю компиляцию и непосредственное программирование микросхем.

MAX+plusII предоставляет полный спектр возможностей для проектирования цифрового устройства: ввод проекта(различными способами), логический синтез, компиляцию с заданными временными ограничениями, функциональное и временное моделирование, разделение проекта на части и моделирование проекта, выполненного на нескольких микросхемах, временной анализ, автоматическое определение ошибок, программирование и верификацию микросхем. САПР MAX+plusII позволяет вводить и сохранять проекты в виде файлов AHDL(язык описания аппаратуры фирмы Altera), EDIF, Verilog HDL, VHDL, OrCAD.

MAX+plusII состоит из 11 полностью интегрированных программных модулей, каждый из которых выполняет свою функцию при создании проекта. Ввод проекта может осуществляться следующими способами: с помощью графического редактора(составление принципиальной схемы из заранее заготовленных символов путём соединения выводов), с помощью текстового редактора(ввод описания проекта на одном из выше перечисленных языков), а также с помощью редактора временных диаграмм. Проект MAX+plusII может содержать в себе различные типы файлов.

В данном проекте использовались графический и текстовый редакторы. Редактор временных диаграмм применялся исключительно для симуляции и отладки проекта.

Работа над проектом

В связи со сложностью поиска зарубежных аналогов отечественным микросхемам, применяемым в ИКМ-30, в библиотеках MAX+plusII, был выбран путь реализации этих микросхем с помощью текстового редактора.

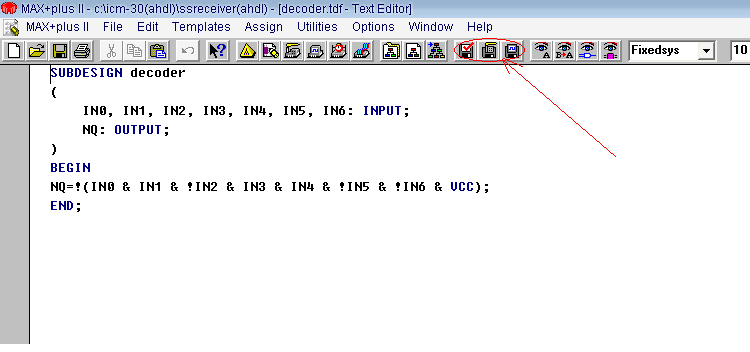

На языке AHDL были описаны только те элементы функциональной схемы, для которых не нашлось точных аналогов в серии 74. Такими элементами были выбраны: входной семиразрядный сдвиговый регистр(INPUT_Register); опознаватель, представляющий собой элемент 7И-НЕ с инверсиями на некоторых входах(DECODER); накопитель по входу(In_Case); дополнительный счётчик и счётчик-делитель на 512(Count512). Для написания программ, описывающих работу элементов, были использованы стандартные элементы кода AHDL Templates. Листинги этих программ находятся в приложениях. Накопитель по выходу строился путём добавления дополнительной логики к уже существующему библиотечному регистру.

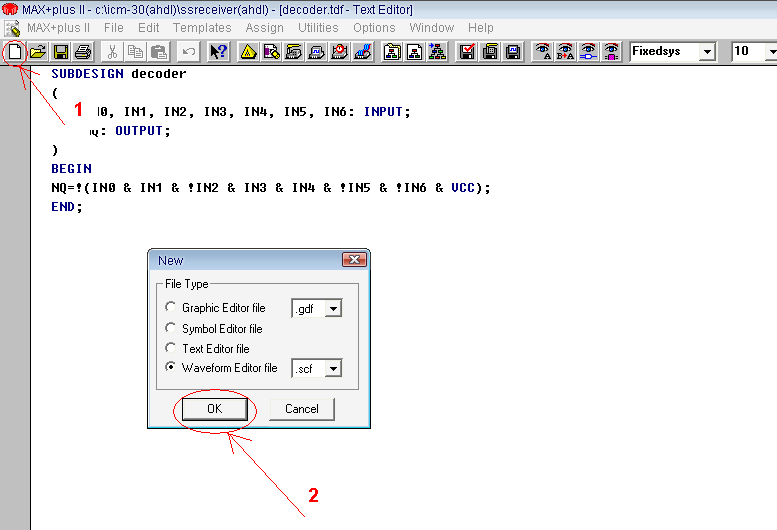

Все вновь созданные элементы были откомпилированы и проверены на симуляторе MAX+plusII. Для этого, при открытом файле программы(*.tdf):

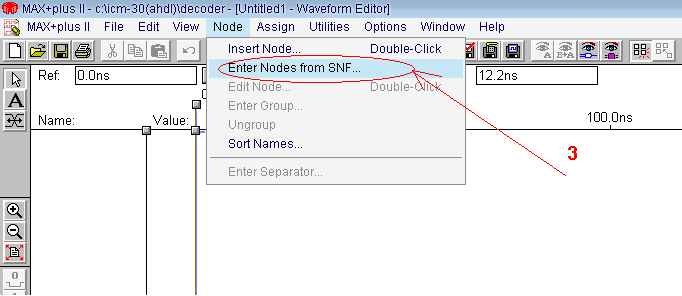

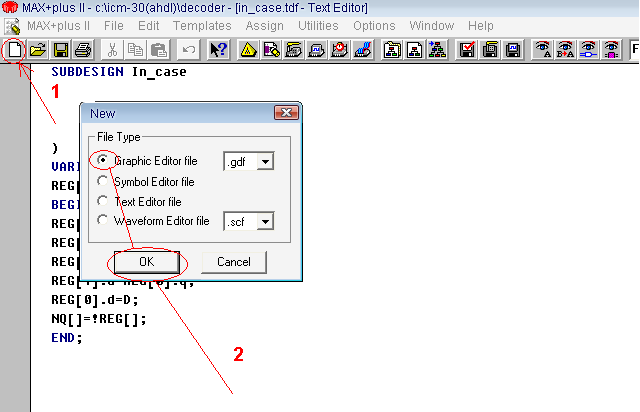

При последовательном нажатии указанных кнопок происходит проверка на ошибки, автоматический выбор микросхемы, компиляция в код ассемблера этой микросхемы, симуляция в симуляторе MAX+plusII. Перед симуляцией необходимо создать файл *.scf с аналогичным именем, что и *.tdf, который будет описывать на какие выводы вновь созданного элемента какие сигналы подавать при симуляции. Этот файл создаётся в редакторе временных диаграмм, который позволяет подавать сигналы любой структуры. Для создания файла *.scf:

Теперь необходимо добавить выводы:

Редактирование сигналов производится следующим образом. Необходимо выбрать вывод и при нажатой левой кнопке мыши выбрать редактируемый участок. Затем с помощью панели инструментов(слева) установить нужный уровень сигнала.

Описание элементов схемы

Input_Register представляет собой сдвиговый регистр, состоящий из 7 D-триггеров, соединенных последовательно. ИКМ сигнал подаётся на информационный вход триггера младшего разряда, а снимается в параллельном коде с выходов всех триггеров одновременно. Особенностью этого регистра является то, что он работает по заднему фронту сигнала тактовой частоты, которая подаётся на clk входы всех триггеров.

Decoder – это элемент 7И-НЕ, входы 2, 5, 6(нумерация с 0) включены с инверсией.

In_Case – сдвиговый регистр, состоящий из трёх D-триггеров. Работает по переднему фронту сигнала синхронизации, поступающему с дополнительного счётчика. Имеет вход асинхронной установки в 1 с активным уровнем LOG«0». Особенность: выходы разрядов инвертированы.

Count512 – восьмиразрядный счётчик со сложной структурой. Включает семиразрядный счётчик и дополнительный триггер. При переполнении семиразрядного счетчика выдаётся промежуточный сигнал BR, который и передаётся на выход, но через логическую схему, объединяющую его элементами И с выходными сигналами(прямым и инверсным) дополнительного триггера. Счётчик имеет асинхронную установку. Если на входе R LOG0, то счётчик делит тактовую частоту на 512 и выдаёт 4кГц, если на R LOG1, то счётчик выдаёт на выход сигнал тактовой частоты.

Out_Case – четырёхразрядный последовательно-параллельный регистр, параллельные входы которого соединены с общей шиной, а последовательный вход с шиной питания. Вход MODE выбирает режим работы(параллельная загрузка или сдвиг), в следствие чего изменяя MODE мы можем либо записывать последовательно LOG1 либо сбрасывать все триггеры регистра в 0.

С помощью D-триггера на входе асинхронной установки In_Case мы сбрасываем накопитель по входу в нужный момент. На нём организована проверка Р2 КИ0 нечетных циклов.

RS триггер выбирает режим работы дополнительного счётчика(деление на 512 или сброс и выдача тактовой частоты).

Элемент 4И-2ИЛИ-НЕ формирует сигнал установки счётчика-делителя на 512 в момент, когда накопитель по выходу зафиксировал выход из синхронизма, а накопитель по входу обнаружил новое место синхропоследовательности и есть сигнал отклика от опознавателя.

JK-триггер проверяет Р2 КИ0 нечетных циклов и выбирает режим записи для накопителя по выходу.

Счётчики работают по переднему фронту сигнала тактовой частоты, накопитель по выходу по заднему.

С 0 разряда накопителя по выходу выдаётся информация об ошибках. Третий разряд выдаёт сигнал о потере циклового синхронизма «Авария ЦС»

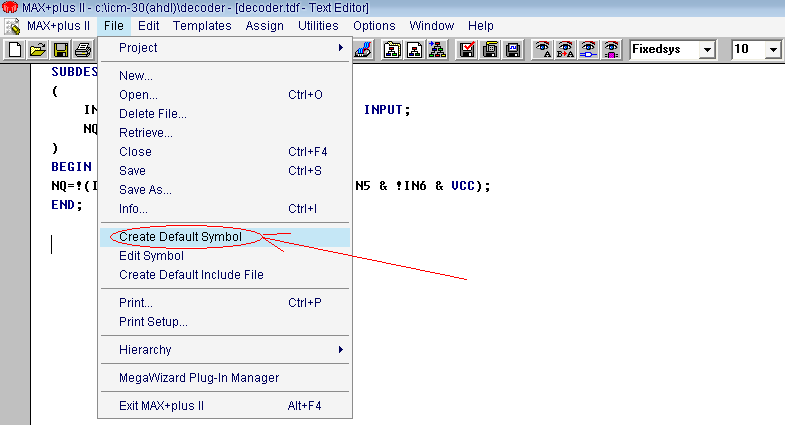

Для дальнейшего соединения элементов необходимо создать файлы символов (для каждого). Это делается следующим образом: открываем файл описания, а затем

Файл символа описывает графическую структуру элемента: имя, количество выводов, их наименование. Для библиотечных элементов эти файлы уже существуют.

Сборка проекта

Для сборки проекта из заготовленных элементов воспользуемся графическим редактором MAX+plusII.

Создадим графический файл *.gdf:

Добавлять элементы можно двойным щелчком на пустом пространстве. При этом появляется окно, в котором необходимо выбрать библиотеку и элемент или просто ввести имя элемента.

Когда все элементы размещены, нужно их соединить согласно схеме. Эта операция проводится точно так же как в любом графическом редакторе. Просто рисуем линии проводников. Однако большое количество проводников загромождает рабочее пространство. Чтобы это исключить в MAX+plusII используется привязка с помощью имён. В данном проекте этот приём тоже использован. Два проводника называются одинаково и они уже соединены. Т.е. проводники могут находиться в разных углах экрана и не соединяться графически.

Для того, чтобы проект был скомпилирован необходимо указать компилятору куда подавать входные и откуда снимать выходные сигналы. Для этого нужно добавить элементы INPUT и OUTPUT из стандартной библиотеки.

Теперь схема собрана. Для компиляции используем приём описанный выше. Схема приёмника циклового синхросигнала готовая для моделирования в симуляторе MAX+plusII находится в приложениях.

Моделирование работы схемы проекта

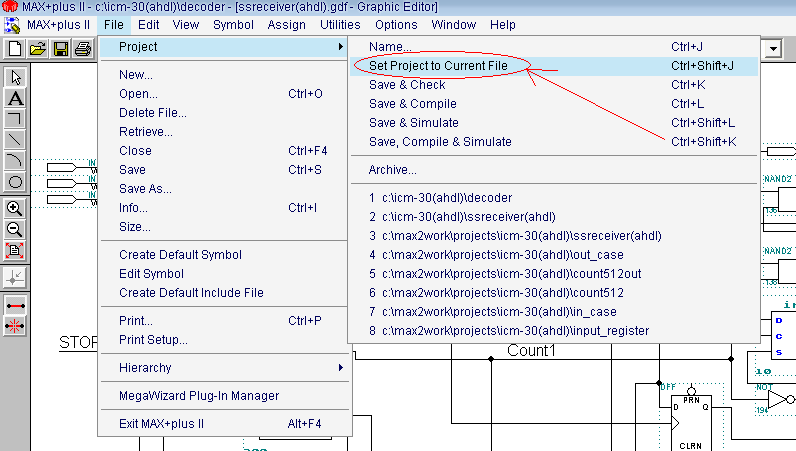

Чтобы выяснить правильно ли работает схема, её необходимо промоделировать. Воспользуемся редактором временных диаграмм MAX+plusII. Создаём файл *.scf точно так же как это делалось для каждого из элементов. Необходимо проинициализировать проект(определить какой из файлов будет главным в проекте). Для этого выбираем файл схемы *.gdf и:

Сохраняем файл *.scf под тем же именем, что и проект(в данном случае ssreceiver). Добавляем необходимые выводы на временную диаграмму: PRN, Clock, ICM, NAND7, Count1, In_Case[0..2], Count2, Out_Case[0..3].

PRN – сигнал предварительной установки триггеров

Clock – сигнал тактовой частоты 2048кГц

ICM – сигнал, в соответствии со структурой реального сигнала ИКМ

NAND7 – сигнал с выхода опознавателя

Count1, Count2 – сигналы с выходов дополнительного счётчика и счётчика-делителя на 512 соответственно.

In_Case[0..2],Out_Case[0..3] – выходы разрядов накопителей по входу и по выходу соответственно.

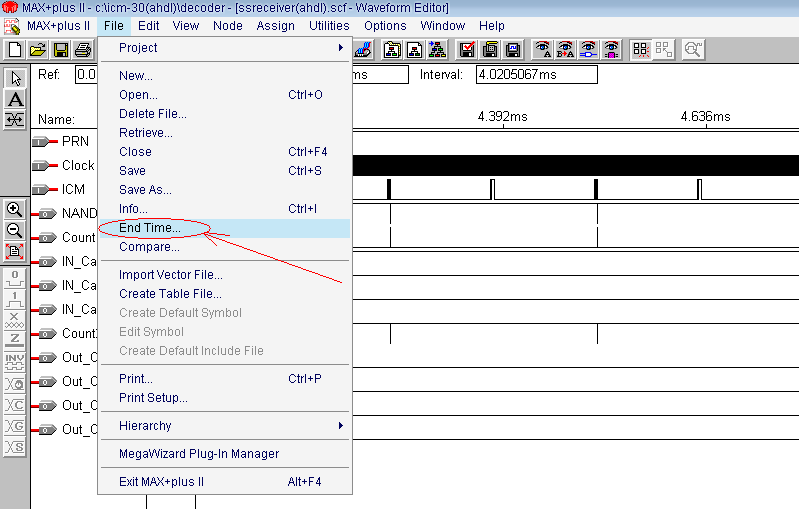

Задаём конечное время симуляции 5мс:

Задаём тестовые сигналы на входах:

PRN – устанавливаем в 1 и добавляем единичный сброс в 0 длительностью в 1 синхроимпульс в самом начале диаграммы.

Clock – сигнал тактовой частоты с периодом 488нс(частотой 2048кГц)

ICM – создаём сигнал ИКМ в соответствии с временными интервалами реальной системы. Можно создать чётный и нечетный цикл а потом размножить по всей длине диаграммы. Сигнал ИКМ необходимо сдвинуть относительно начала диаграммы на время, достаточное для достижения устойчивого состояния схемы при включении(в противном случае возникают неопределенности).

Запускаем симуляцию и анализируем результат.

Сначала мы подаём идеальные сигналы, что должно соответствовать состоянию циклового синхронизма. Схема при начале симуляции находится в состоянии рассинхронизации потому, что ИКМ сигнал смещен: дополнительный счётчик находится в режиме поиска синхронизма, а счётчик-делитель на 512 работает в режиме деления частоты, но при этом считает с момента появления сигнала тактовой частоты, а не с момента прихода первой синхрокомбинации(см. приложение №5). Накопитель по выходу фиксирует отсутствие синхронизма и записывает последовательно в течение пяти циклов единицы. Накопитель по входу работает в режиме поиска нового положения синхропоследовательности. При первом же правильно принятом синхросигнале записывает 1 на выход младшего разряда, дополнительный счётчик переходит в режим деления на 512 и теперь только через 256 тактов под действием тактового импульса с выхода S счётчика проверяется наличие 1 в Р2 КИ0 нечетного цикла, единица присутствует, накопитель по входу не меняет своего состояния. В следующем цикле происходит запись 1 в следующий разряд накопителя по входу, сбрасывается счётчик-делитель на 512 и начинает работать в фазе с приходящим ИКМ сигналом. В следующем цикле опять проверяется наличие единицы на месте Р2 и накопители не меняют своего состояния. При приходе синхрокомбинации в пятом по счёту цикле происходит обнуление всех триггеров накопителя по выходу и окончательное заполнение единицами накопителя по входу. Схема вошла в синхронизм с ИКМ сигналом через 4 полных цикла. Далее изменений нет, т.к. сигналы поступают синхронно без воздействия помех и схема находится в синхронизме.

Теперь внесем в сигнал ИКМ искажения после того момента как схема найдёт первоначальный синхронизм. Занулим третий бит синхропоследовательности в 6 цикле (см. приложение №6). При таком искажении сигнала схема из состояния синхронизма перешла в состояние поиска синхронизма, дополнительный счётчик остановился и выдаёт на выход сигнал тактовой частоты, что продолжается до прихода правильной синхропоследовательности в цикле 8. Через 3 такта накопитель по входу заполнился нулями. Счётчик-делитель на 512 остаётся в фазе с ИКМ сигналом и продолжает считать, но в накопитель по выходу записалась единица. Эта единица остаётся в накопителе до момента прихода правильной синхропоследовательности в восьмом цикле. В цикле 7 происходит проверка Р2, но там нет искажений, сигнал верный и накопители остаются в прежнем состоянии. При приходе правильной синхропоследовательности в цикле 8 дополнительный счётчик переходит в режим деления на 512, в накопитель по входу записывается 1, накопитель по выходу сбрасывается. Синхронизм восстановлен.

Исправим сигнал ИКМ и внесем искажение в цикле 7. Занулим Р2 (см. приложение №7). При проверке Р2 КИ0 седьмого цикла схема не обнаруживает единицы. Накопитель по входу сбрасывается в 0(все разряды), дополнительный счётчик переходит в режим поиска синхронизма. Накопитель по выходу в прежнем состоянии. При приходе правильной синхрокомбинации в восьмом цикле в младший разряд накопителя по входу записывается единица, дополнительный счётчик переходит в режим счёта, в накопитель по выходу записывается единица в младший разряд. Накопитель по выходу сбрасывается только в цикле 10. И синхронизм снова восстановлен.

Теперь снова исправим сигнал ИКМ и внесем изменения в сигнал тактовой частоты после момента нахождения первоначального синхронизма. Удалим один импульс (см. приложение №8). Искажение внесено в четвертом цикле. На пятом цикле ничего не происходит, т.к. Р2 КИ0 смещается из-за искажения на одну позицию вправо на Р3, а там тоже единица и схема принимает её за верное значение. А вот на цикле 6 происходит срыв синхронизма из-за того, что счётчики срабатывают не в момент прихода синхропоследовательности, а с запаздыванием на 1 такт. Накопитель по входу работает также как при искажении в синхропоследовательности (в режиме поиска) до прихода правильной синхропоследовательности в восьмом цикле. Там происходит перевод дополнительного счётчика в режим счёта и в накопитель по входу записывается единица. Но счётчик-делитель на 512 по прежнему не в фазе и в накопитель по выходу на восьмом цикле записывается еще одна единица (вторая). Накопитель по выходу сбросится только на десятом цикле, когда счётчик-делитель будет установлен в фазу. После этого момента синхронизм можно считать восстановленным.

Итак, проведен анализ работы схемы приёмника циклового синхросигнала при единичных искажениях во входных сигналах. Теперь проанализируем работу схемы в режиме аварии циклового синхронизма. Исказим сразу три цикла сигнала ИКМ. Занулим: Р3 КИ0 шестого цикла, Р2 КИ0 седьмого цикла, Р3 КИ0 восьмого цикла (см. Приложение №9). В шестом цикле происходит срыв синхронизма. Дополнительный счётчик переходит в режим поиска, накопитель по входу обнуляется за три такта, в накопитель по выходу записывается единица. При приходе неправильной синхрокомбинации в цикле 8 накопитель записывает еще одну единицу, накопитель по входу и дополнительный счётчик в прежнем состоянии. Т.к. в девятом цикле сигнал соответствует верному, JK-триггер сброса накопителя по выходу устанавливается в соответствующий режим и на десятом цикле происходит сброс накопителя по выходу. Синхронизм будет восстановлен только в двенадцатом цикле. Это сделано для того, чтобы исключить возможность ложного синхронизма из-за формирования ложных синхрогрупп. Схема проверяет три цикла подряд и тогда, если все в порядке, можно считать, что синхронизм восстановлен.

Итак, промоделированы возможные причины потери синхронизма, схема проекта работает исправно. Теперь можно файл проекта прошить в реальную микросхему, которая будет выполнять функции приемника циклового синхросигнала.

Выводы

В ходе данной работы я изучил на практике работу приёмника циклового синхросигнала аппаратуры ЦСП ИКМ-30С-4, а также структуру цикла передачи. Также я познакомился с современными способами разработки цифровой аппаратуры, а в частности с системой автоматизированного проектирования MAX+plusII фирмы Altera, как в плане проектирования, так и в плане проверки схемы на работоспособность.

Литература

Л.С. Левин, М.А. Плоткин «Цифровые системы передачи информации»Радио и Связь 1982г. Москва

Руководство по эксплуатации цифровой системы передачи информации ИКМ-30-С-4:

Комплект оборудования №1 Аппаратура первичной цифровой системы передачи для СТС ИКМ-30С-4 Альбом №1

Комплект оборудования №1 Блок АЦО-11 Альбом №13

Комплект оборудования №1 Блок АЦО-11 Альбом №14