Методика расчета и оптимизации ячеек памяти низковольтовых последовательных ЭСППЗУ

ОГЛАВЛЕНИЕ

1 ВВЕДЕНИЕ

2 ОБЩИЕ СВЕДЕНИЯ

2.1 Элементы СППЗУ

2.1.1 Элементы ЭСППЗУ, программируемые с помощью туннельного эффекта

3 МОДЕЛИРОВАНИЕ ЯЧЕЙКИ ЭСППЗУ

3.1 Упрощенная модель ячейки памяти

3.1.1 Расчет V>tun>

3.1.2 Расчет пороговых напряжений

3.1.3 Зависимость порогов от времени записи/стирания

3.2 Полная модель ячейки

3.2.1 Расчет плавающего затвора и потенциалов канала

4 ЭКСПЕРИМЕНТАЛЬНАЯ ЧАСТЬ

4.1 Запоминающая ячейка

4.1.1 Методика исследования элементной базы ЭСППЗУ

4.2 Результаты исследования элементной базы

4.2.1 Исследование характеристик туннельного окисла

4.2.2 Эквивалентная схема замещения туннельного окисла

4.2.3 Построение и расчет ячейки ЭСППЗУ

5 ТЕХНИКО-ЭКОНОМИЧЕСКОЕ ОБОСНОВАНИЕ ПРОЕКТА

5.1 Краткая характеристика проведенной работы

5.2 Методика определения сметной калькуляции и цены на ОКР

5.3 Расчет сметной калькуляции, плановой себестоимости и цены на ОКР

6 ОХРАНА ТРУДА И ЭКОЛОГИЧЕСКАЯ БЕЗОПАСНОСТЬ

СПИСОК ИСПОЛЬЗУЕМОЙ ЛИТЕРАТУРЫ

1. ВВЕДЕНИЕ

Запоминающие устройства имеют очень широкое применение в самых различных областях электроники, вычислительной техники, контрольно-измерительного оборудования. Они присутствуют везде где необходимо запоминание и хранение любого вида информации. ЭСППЗУ являются одной из разновидностей запоминающих устройств и по своим специфическим особенностям они составляют основу блоков электронной аппаратуры, кредитных и телефонных карточек, устройств где необходимо хранить информацию с отключением источника питания.

В современных условиях основное внимание во всем мире уделяется энергосберегающим технологиям. Развитие электроники связано с уменьшением норм топологического проектирования интегральных схем, и это требует разработки и применения элементной базы интегральных схем с пониженным напряжением питания. Анализ состояния научно-технических разработок зарубежных производителей интегральных микросхем показывает, что все новые разработки выполняются только с 3-х вольтовым напряжением питания. Ряд иностранных фирм, таких как Siemens, Philips, Microchip и др., производят изделия с нижней границей напряжения питания 2,5 В, а их научные подразделения уже разрабатывают приборы с напряжением питания 1,0 В.

В настоящее время на НПО “Интеграл” усилия разработчиков интегральных микросхем направлены на переход на стандарт с пониженным напряжением питания (3 В) и, соответственно, с пониженной потребляемой мощностью электронных приборов. Однако, переход на новый стандарт для некоторого типа приборов связан с определенными трудностями. В частности, это относится для целого направления последовательных ЭСППЗУ, которые сейчас широко используются в серии микросхем для телевизионных приемников и телефонных карточек.

Изделия этого класса имеют некоторые специфические технические характеристики. Так, например, напряжение питания их составляет 5 В, что не позволяет создавать электронные приборы с автономным питанием, использование их в автомобильной электронике, и исключает их прямое согласование с элементной базой основанной на 3-х вольтовом стандарте. Нижняя граница напряжения питания этого класса схем определяется элементной базой, схемотехническими и топологическими решениями узлов ЭСППЗУ, определяющими режимы записи информации в запоминающую ячейку. Существующие решения не позволяют достигать требуемой длительности цикла записи при низком значении напряжения питания (3 В). Это требует оптимизации запоминающих элементов (ячеек).

Целью работы является разработка методики расчета и оптимизации ячеек памяти низковольтовых последовательных ЭСППЗУ. Разрабатываемая модель запоминающей ячейки должна позволить в полном объеме проводить моделирование и расчет ЭСППЗУ.

2. ОБЩИЕ СВЕДЕНИЯ

Цифровые полупроводниковые микросхемы памяти предназначены для применения в оперативных (ОЗУ) и постоянных (ПЗУ) запоминающих устройствах. Наиболее распространены БИС памяти с произвольной выборкой, основной частью которых является накопитель — матрица запоминающих элементов (элементов памяти), каждый из которых предназначен для хранения одного бита информации. Совокупность элементов представляет собой информационную емкость БИС. С помощью систем шин строк Х и столбцов Y возможна выборка произвольного элемента памяти.

Микросхемы ПЗУ хранят информацию при отключении источника питания, тогда как в микросхемах ОЗУ она теряется.

Важнейшими параметрами элемента памяти являются площадь, занимаемая им на кристалле, и потребляемая мощность. Для достижения максимальной информационной емкости площадь элемента, а значит, и размеры транзисторов (длина, ширина канала и др.) должны быть минимальными. Они зависят от разрешающей способности фотолитографии, задающей минимальный топологический размер. При сравнении элементов памяти разных типов удобно оценивать их площадь не в абсолютных, а в относительных единицах — числом литографических квадратов со стороной. Относительная площадь характеризует «качество» схемотехники и топологического проектирования элементов памяти.

Репрограммируемые ПЗУ хранят информацию при отключенном источнике питания. Ввод информации называют программированием. Установку элементов памяти в исходное одинаковое состояние, соответствующее хранению лог. О (или лог. 1), называют стиранием информации. В зависимости от типа элементов памяти оно может осуществляться электрическим или неэлектрическим способом. Соответствующие устройства обозначают ЭСППЗУ (электрически стираемые программируемые ПЗУ) или СППЗУ. В СППЗУ стирание осуществляется сразу для всех элементов накопителя, в ЭСППЗУ его можно произвести в отдельной строке и даже в произвольно выбранном одном элементе. Стирание и последующее программирование образуют цикл перепрограммирования.

Элементы памяти основываются на бистабильных МДП-транзисторах, которые могут находиться в одном из двух состояний, соответствующих хранению лог. 1 или лог. О. Наиболее распространенными являются транзисторы с «плавающим» затвором, у которых между управляющим затвором и подложкой расположен второй затвор, со всех сторон окруженный диэлектриком. Потенциал второго затвора изменяется в зависимости от заряда на нем, отсюда и название «плавающий». Хранимая информация определяется зарядом на плавающем затворе.

2.1 Элементы СППЗУ

В отличие от постоянных запоминающих устройств (ПЗУ) и однократно программируемых постоянных запоминающих устройств (ППЗУ), которые не допускают изменения однажды записанной информации, в стираемых ПЗУ информацию можно перезаписывать многократно. Стирание информации производится с помощью ультрафиолетового облучения. Длительность хранения записанной информации может доходить до нескольких лет и более. Поэтому стираемые ПЗУ часто называют энергонезависимой памятью (памятью с сохранением информации при выключении электропитания). Существует много различных типов стираемых ПЗУ незначительно отличающихся принципами действия и структурой, причем каждый тип имеет свои разновидности.

Электрически программируемые ПЗУ (ЭППЗУ) не требуют для стирания информации ультрафиолетового облучения. Запись и удаление информации из запоминающего элемента производится с помощью приложения высокого напряжения. Примером ЭППЗУ является структура с плавающим затвором и туннельным переходом (ПЛТМОП). В таких ПЗУ информация стирается электрически последовательно бит за битом.

В настоящее время моделирование и оптимизация конструкции ЭСППЗУ осложнено отсутствием модели запоминающего элемента, основой которого является участок с туннельным окислом. Для модели требуется создание схемы замещения этого участка на основе анализа элементной базы низковольтовых ЭСППЗУ, а также методики расчета и оптимизации конструкции ячейки.

В случае хранения лог. 1 на плавающем затворе существует отрицательный заряд электронов и пороговое напряжение по управляющему затвору, получается высоким (несколько вольт). Если хранится лог. О, то заряд на плавающем затворе равен нулю или положителен, тогда пороговое напряжение, низкое (или даже отрицательное). Так как токи утечки диэлектрика ничтожно малы, то время хранения, являющееся важным параметром элемента памяти, большое. По оценкам оно превышает 10 лет при повышенной температуре (70...100'С), когда токи утечки максимальны.

В режиме считывания на шину выбранной строки подают напряжение, лежащее в пределах порогового, а на шины остальных строк — напряжение, меньшее порогового, так что в элементах памяти этих строк транзисторы закрыты. В выбранной строке транзисторы будут открытыми или закрытыми в зависимости от хранимой информации. Следовательно, в шине выбранного столбца в случае хранения лог. 0 будет протекать ток, а в случае хранения лог. 1 ток равен О. Ток в шине столбца воспринимается усилителем считывания. Время считывания определяется значением тока, чувствительностью и быстродействием усилителя и других схем обслуживания. Оно того же порядка, что и в СБИС ОЗУ.

В режиме программирования напряжение на шине выбранного столбца устанавливается высоким (около 15..20 В), если необходимо создать отрицательный заряд на плавающем затворе (запрограммировать лог. 1). В противном случае это напряжение равно 0. Напряжение на шине выбранной строки также устанавливается высоким, причем большим напряжения программирования столбца. Программирование основано на инжекции горячих электронов в окисел у стокового конца канала. Они генерируются в сильном электрическом поле, высокая напряженность которого обусловлена малой длиной канала и большим напряжением программирования. Число инжектированных электронов пропорционально току канала, составляющему несколько миллиампер. Так как напряжение на управляющем затворе выше, чем на стоке, в диэлектрике существует вертикальная составляющая вектора напряженности электрического поля, благодаря которой инжектированные в окисел электроны дрейфуют к плавающему затвору и накапливаются на нем. Ток через диэлектрик очень мал (единицы пикоампер), поэтому время программирования одного элемента памяти весьма велико (около 1 мс) и на 4 порядка превышает время считывания.

Стирание (удаление электронов с плавающего затвора) производится облучением кристалла ультрафиолетовым светом, для чего в корпусе микросхемы предусматривается окно с кварцевым стеклом. Под действием света электроны приобретают энергию, достаточную для перехода с плавающего затвора в диоксид. Далее они дрейфуют в подложку, потенциал которой должен быть выше, чем на управляющем затворе. Время стирания порядка 1 мин. Для проведения этой операции микросхема должна быть извлечена из устройства и поставлена в специальную установку стирания, что практически не всегда удобно, причем стирается содержимое всего накопителя.

В каждом цикле перепрограммирования происходят небольшие изменения в физической структуре элемента. Протекание токов через диоксид приводит к захвату в нем электронов ловушками и образованию дополнительного поверхностного заряда. Установлено, что после большого числа циклов разность порогового напряжения 0 и 1 уменьшается. Поэтому существует максимально допустимое число циклов перепрограммирования (около 103).

Достоинством рассмотренного элемента является его простота и малая площадь (6...10 литографических квадратов). Это позволяет создавать СБИС большой информационной емкости (1 Мбит и выше).

2.1.1 Элементы ЭСППЗУ, программируемые с помощью туннельного эффекта

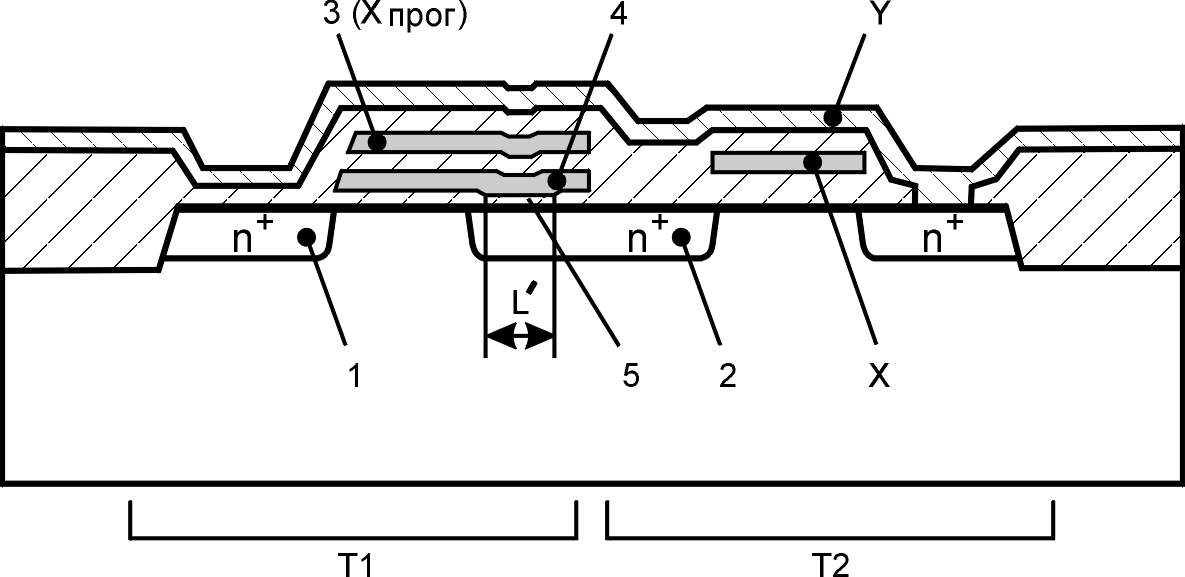

Ha рисунке 1 показана структура, а на рисунке 2 эквивалентная схема элемента памяти. Левая часть структуры образует бистабильный транзистор (1 — исток, 2 — сток, 3 — управляющий затвор, совмещенный с шиной программирования строки Х>прог>, 4 — плавающий затвор). Слой диоксида 5, отделяющий сток 2 от затвора 4, имеет очень малую толщину — порядка 10 нм (туннельно-тонкий диоксид). При программировании на шину Х>прог >выбранной строки подают высокое напряжение (20 В). Если на плавающий затвор надо ввести заряд (запрограммировать лог. 1), то на стоке следует установить нулевое напряжение. Тогда происходит туннелирование электронов из стока в слой 5 и их дрейф на плавающий затвор. Если же не надо вводить заряд, то на стоке устанавливают такое же напряжение, как и на управляющем затворе. Для стирания (удаления заряда) на управляющий затвор необходимо подать нулевое напряжение, а на сток — высокое. Тогда электроны совершают обратный переход с плавающего затвора в сток. Таким образом, программирование и стирание идут с одинаковой скоростью. Эти процессы отличаются только знаком напряженности электрического поля в слое 5 и направлением движения электронов.

Достоинством рассмотренного элемента является возможность стирания информации в произвольно выбранном элементе памяти за малое время (менее 1 мс). Максимальное число циклов перепрограммирования достигает 106 — больше, чем для элементов, использующих инжекцию горячих электронов. 0днако площадь элемента памяти в 3...4 раза больше, чем у элементов ПЗУ и составляет 30...40 литографических квадратов. Недостатком также является необходимость получения тонкого высококачественного диоксида, что сложно технологически и ухудшает надежность.

Рисунок 1

Рисунок 2

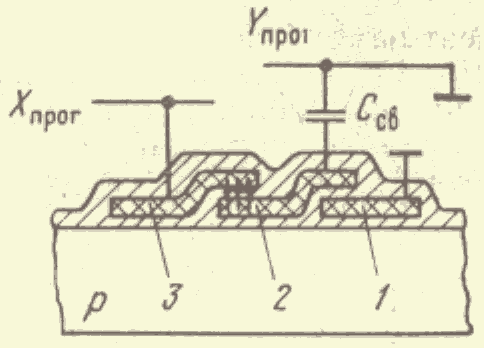

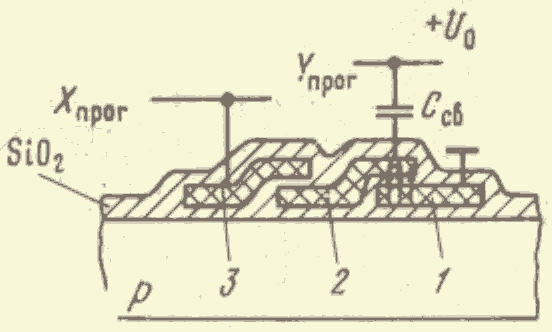

Толщина диоксида может быть увеличена в несколько раз, если использовать туннелирование с шероховатой поверхности поликремния. Структура элемента памяти содержит три слоя поликремния, взаимное расположение которых показано на рисунок 3 (области истока, стока и шины Х, Y для простоты не показаны). Источником электронов при программировании служит электрод 1 первого слоя поликремния, являющийся общей шиной (он соединяется с областью истока транзистора). Плавающий затвор 2 создают нанесением второго, а затвор управления 8 — третьего слоя поликремния. Толщина диоксида между слоями 1 и 2, 2 и 3 около 0,04 мкм. В такой структуре возможно только одностороннее туннелирование с электрода 1 вверх. Обратное туннелирование вниз невозможно, так как нижняя поверхность плавающего затвора гладкая, а напряженность электрического поля из-за большой толщины диэлектрика мала.

Для удаления электронов с плавающего затвора при стирании используют туннелирование вверх и дрейф электронов на управляющий затвор. В обоих режимах программирования и стирания на управляющий затвор (шину Х>прог> )подают высокое напряжение 15...20 В. Чтобы при программировании не было перехода электронов с плавающего затвора на управляющий, а при стирании- с электрода 1 на плавающий затвор, между плавающим затвором и специальной управляющей шиной У>прог >создают конденсатор связи C>св>. При программировании (рисунок 3) на У>прог> подают положительное напряжение U>0>, дополнительно повышающее потенциал плавающего затвора. Разность потенциалов между ним и управляющим затвором получается малой, и туннелирование с плавающего затвора вверх отсутствует. При стирании (рисунок 4) на управляющей шине У>прог> устанавливают нулевое напряжение, понижающее потенциал плавающего затвора. В результате разность потенциалов между затворами 3 и 2 получается высокой и идет интенсивное туннелирование электронов с затвора 2 вверх. В то же время разность потенциалов между электродами 2 и 1 мала и туннелирование с электрода 1 отсутствует.

Элемент памяти по сравнению с предыдущим характеризуется меньшей площадью (15…20 литографических квадратов), что позволяет создать СБИС с большей информационной емкостью (256 Кбит…1Мбит). Из-за гораздо больших токов туннелирования время программирования получается меньше (0,003 мс/байт).

Рисунок 3

Рисунок 4

3. МОДЕЛИРОВАНИЕ ЯЧЕЙКИ ЭСППЗУ

В данной работе будет рассмотрен теоретический анализ и экспериментальные данные по программированию и стиранию ячейки памяти программируемой туннельным током.

Структура такой ячейки изображена на рисунке 5. Это n-канальный транзистор с плавающим затвором. Тонкий окисел (~100 ангстрем) между плавающим затвором и стоком способен пропускать электроны (туннелирование) инжектируемые и поглощаемые плавающим затвором во время операций записи/стирания согласно эффекту Фаулера-Нордхайма.

Во время записи плавающий затвор заряжается отрицательно электронами, туннелирующими из стоковой области через тонкий оксид. Это достигается за счет приложения положительного потенциала к верхнему (управляющему) затвору, в то время как сток и подложка заземлены. Накопившийся отрицательный заряд на плавающем затворе сдвигает пороговое напряжение транзистора на большую положительную величину. При последующем считывании транзистор будет закрыт.

Операция стирания заключается в снятии отрицательного заряда с плавающего затвора с помощью приложенного к стоку высоковольтного импульса, в то время как исток свободен (не подключен), а оба затвора и подложка заземлены. Величина порогового напряжения смещается в отрицательном направлении, и транзистор открывается при последующем чтении.

Во время считывания прикладывается достаточно низкое напряжение, поэтому туннельный ток незначительный и плавающий затвор практически изолирован. При таких условиях считывания заряд нужной величины (информация) может храниться до 10 лет.

В схемах памяти используется двухтранзисторная ячейка. Дополнительный транзистор вводится для изоляции ячейки от воздействия сигналов соседних ячеек во время циклов записи/стирания.

В данной работе рассматривается анализ и моделирование режимов записи/стирания, учитывая эффекты, которые возникают во время стирания.

Рисунок 5

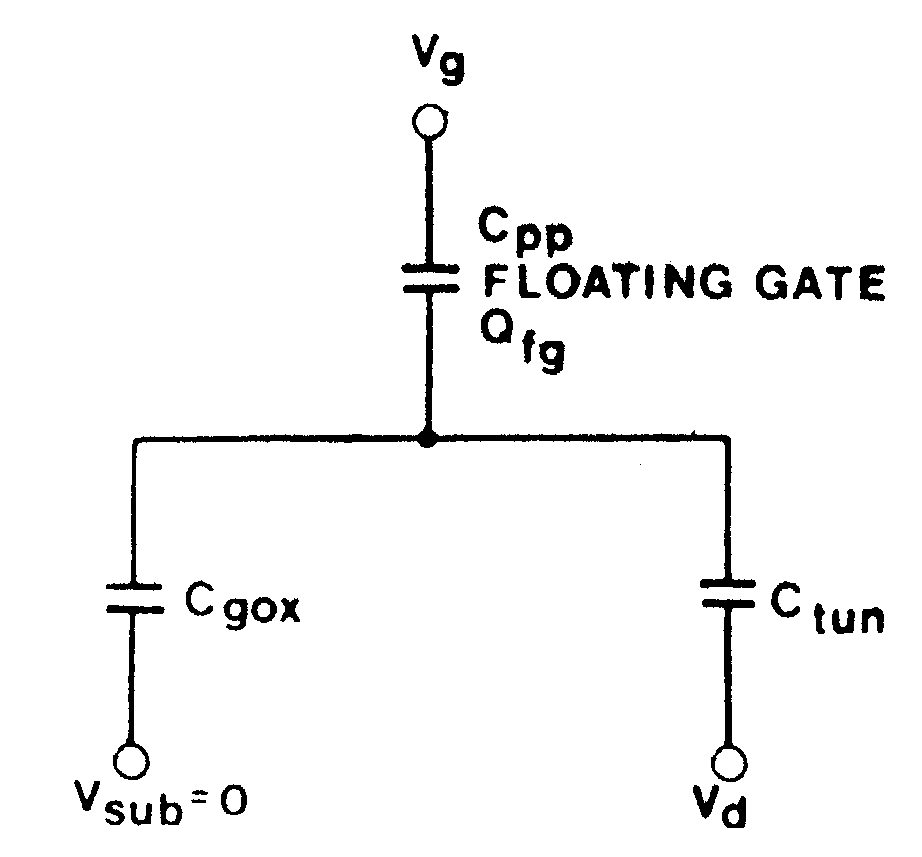

3.1 Упрощенная модель ячейки памяти

Для того чтобы получить представления о работе ячейки используется упрощенная модель эквивалентной схемы прибора, представленная на рисунке 6. Более детальный анализ будет рассмотрен в главе 3.2.

Плотность тока текущего через тонкий окисел приближенно вычисляется при помощи уравнения Фаулера-Нордхайма:

J>tun>> >= E>tun>> > (exp ( -/E>tun>)); (1)

где E>tyn> это электрическое поле в окисле, а и - константы. Электрическое поле в тонком окисле рассчитывается так:

E>tyn>> >= V>tun>> >/X>tun>; (2)

где V>tun> это напряжение туннелирования через окисел, а X>tun> это толщина тонкого окисла. Напряжение туннелирования может быть рассчитано через емкостную эквивалентную схему ячейки

Рисунок 6

3.1.1 Расчет V>tun>

C>pp> это емкость между плавающим и управляющим затвором, C>t>>u>>n >это емкость тонкого окисла, C>gox> это емкость подзатворного окисла между плавающим затвором и подложкой, Q>fg>> >это заряд, накопившийся на плавающем затворе. V>tun> может быть рассчитан для электрически нейтрального затвора по простому соотношению коэффициентов:

V>tun> >запись >= V>g> K>w>; (3)

Где K>w>> >= C>pp>/(C>pp>> >+ C>gox>> >+ C>tun>); (4)

и V>tun> >стирание >= V>d> K>e>;> >(5)

где K>e >= 1 - (C>tun>/(C>pp >+ C>gox >+ C>tyn>); (6)

где V>g>> >и V>d> напряжения на затворе и истоке соответственно, а коэффициенты K>e> и K>w> обозначают напряжение, которое проходить сквозь тонкий окисел при стирании и записи соответственно. Формулы (3) и (5) справедливы, только если Q>fg>=0. Во время записи сохраненный на плавающем затворе потенциал понижает пороговое напряжение тонкого окисла согласно следующей формуле:

V>tun> >запись>= V>g> K>w>> >+ (Q>fg>/(C>pp>> >+ C>gox>> >+ C>tyn>) (3’)

Во время стирания отрицательный начальный потенциал плавающего затвора повышает пороговое напряжение тонкого окисла согласно соотношению:

V>tun> >стирание >= V>d> K>e> – (Q>fg>/(C>pp>> >+ C>gox>> >+ C>tyn>); (5’)

После завершения операции стирания, когда затвор заряжен положительно последний коэффициент уравнения (5) понижает напряжение потенциал тонкого окисла.

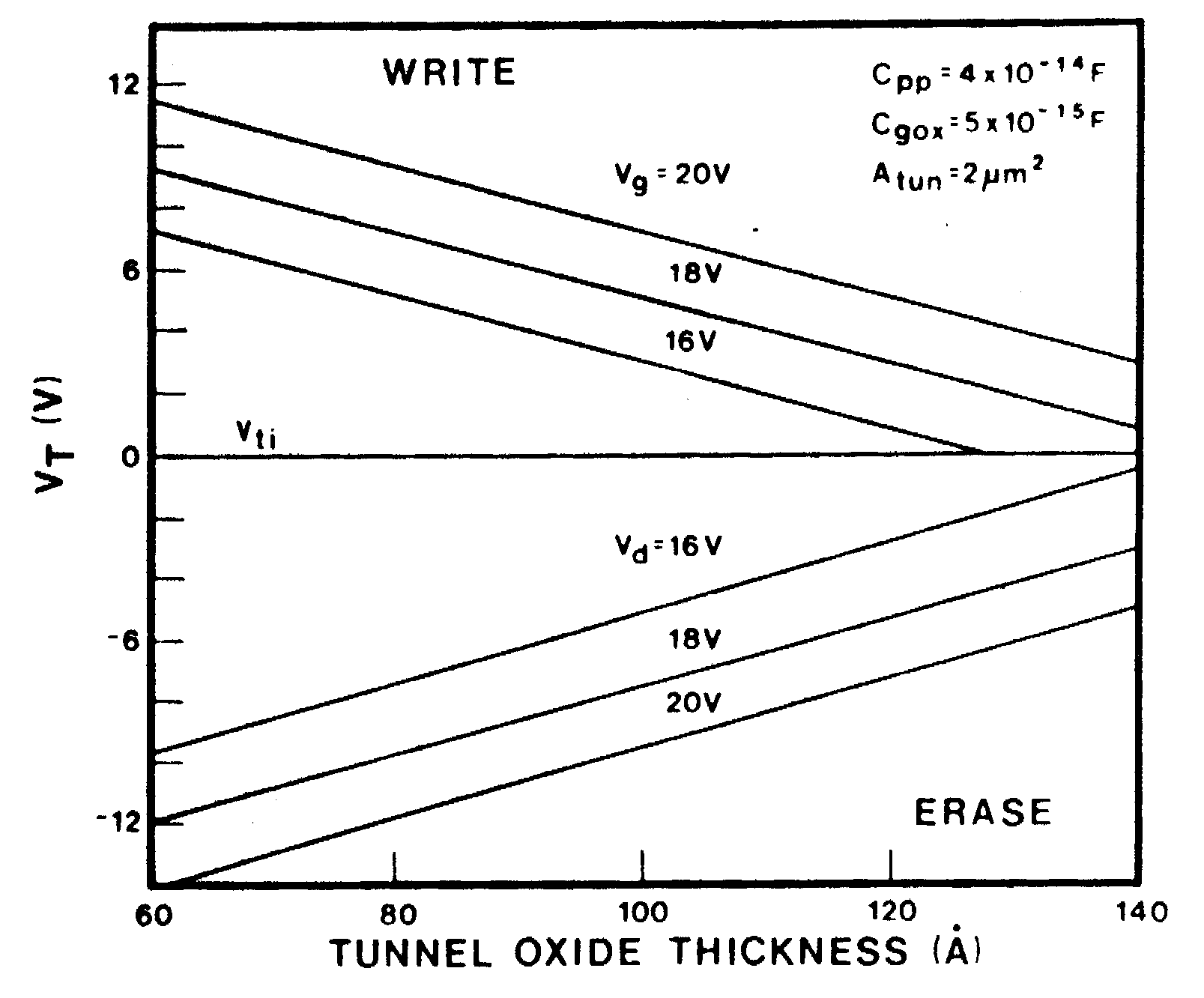

3.1.2 Расчет пороговых напряжений

Начальное пороговое напряжение ячейки, которое соответствует Q>fg>=0, обозначается как V>ti>. Начальный заряд смешает порог согласно соотношению:

V>ti>> >= -Q>fg>/C>pp>> >(7)

Используя соотношения (3') и (5') для определения Q>fg> при снятии импульса записи/стирания пороговые напряжения определяются так:

V>tw>> >= V>ti>> >- Q>fg>/C>pp>> >= V>ti>> >+ V>g>(1 - (V’>tun>/K>w>> > V>g>)) (8)

V>te>> >= V>ti>> >- Q>fg>/C>pp>> >= V>ti>> >- V>d>(K>e>/K>w>> >- (V’>tun>/K>w>> > V>d>)) (9)

Здесь V>tw>> >это порог записи ячейки, а V>te> это порог стирания ячейки.V>g>> >и V>d> это амплитуды импульсов записи и стирания соответственно, а V’>tun> это напряжение в тонком окисле после снятия импульса. Предположим, что импульс записи/стирания по времени достаточно длинный, тогда электрическое поле в тонком окисле уменьшится до значений близких 1107В/см. При такой напряженности поля туннелирование практически прекращается. Приближенное значение V>tun> может быть получено из выражения (2) и подставлено в (8) и (9) для получения приближенных значений окна программирования ячейки, зависимости параметров ячейки и напряжения программирования. Типичные результаты представлены графиками на рисунке 7.

Для того чтобы увеличить окно ячейки нужно увеличить толщину тонкого окисла и напряжение записи/стирания, причем значения связывающих коэффициентов должны быть максимально приближены друг к другу. Оба связывающих коэффициента должны увеличиваться при уменьшении C>tun> и увеличении C>pp>. При увеличении толщины тонкого окисла это обычно достигается за счет уменьшения площади тонкого окисла и внедрения дополнительной поликремниевой области перекрытия в транзисторе ячейки. Типичное значение связующих коэффициентов равно 0,7, причем K>e>> >всегда больше K>w>. Увеличение емкости подзатворного окисла C>gox> увеличивает K>e>, но уменьшает K>w>.

Рисунок 7

3.1.3 Зависимость порогов во время записи/стирания

Аналитическое выражение зависимости пороговых напряжений ячейки от времени программирования получается при решении следующего дифференциального уравнения:

DQ>fg>/dt = A>tun> J>tun>; (10)

Подставляя это уравнение в (1),(2),(3’),(5’) и (7) получим:

V>tw>(t) = V>ti> + V>g> – (1/K>w>) (B/ln(A B t + E>1>); (11)

V>te> (t) = V>ti >– (V>d> K>e>)/K>w> + 1/K>w > [ B /(ln (A B t + E>2>)) ]; (12)

Где A = (A>tun > )/(X>tun > (C>pp> + C>gox> + C>tun>)); (13)

B = X>tun>; (14)

E>1 >= exp[ B/(K>w > (V>g> + V>ti >- V>t>(0))) ]; (15)

E>2 >= exp[ B/(V>d> K>e >+ K>w> V>t>(0) + K>w> V>ti>) ]; (16)

V>t>(0) это пороговое напряжение ячейки при t = 0, которое не может быть спутано с V>ti> – пороговое напряжение нейтральной ячейки. A>tun> это область тонкого окисла. Надо отметить, что в уравнении (11) пороговое напряжение остается практически неизменным при t = 0, если V>g>> >прикладывается на время меньшее, чем “характеристическая временная константа” , которая определяется следующим выражением:

= (1/AB) exp[ B/(K>w> (V>g >+ V>ti> – V>t>(0)) ]; (17)

При больших значениях времени t пороговое напряжение асимптотически приближается к кривой описанной следующим уравнением:

V>tw>(t) = V>ti> + V>g> – [ B/(K>w > ln(A B t)) ]; (18)

Аналогичное выражение для операции стирания выводится из уравнения (12). Это приближение полезно использовать при проектировании ячеек памяти, а также оно может быть применено для оценки времени программирования, порога окна, операционного времени для любого набора параметров ячейки(A, B, V>ti>, K>w>,> >K>e>).

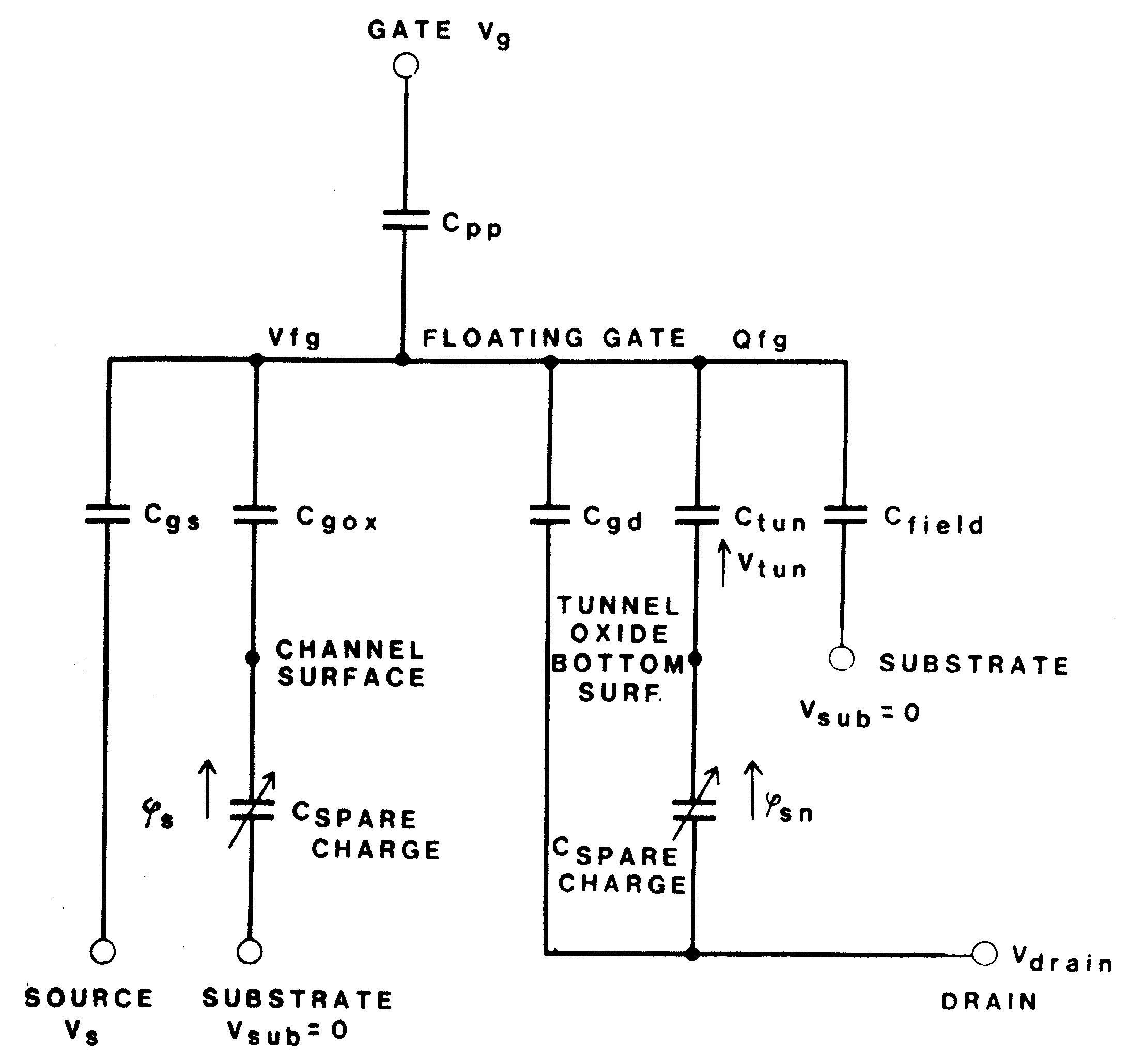

3.2 Полная модель ячейки

3.2.1 Расчет плавающего затвора и потенциалов канала

Эквивалентная схема ячейки памяти ЭСППЗУ с учетом паразитных емкостей и емкостей обедненного слоя представлена на рис.8. Эффект утечки дырок в подложку исключен и предположим, что ячейка у нас спроектирована. C>gs> и C>gd> это емкости перекрытия подзатворного диэлектрика, C>fld>> >это емкость области окисла между плавающим затвором и подложкой. Падение напряжения на емкости обедненного слоя равно >s> и >sn>> >для канала и n+ области соответственно. Накопившийся на плавающем затворе заряд Q>fg> это сумма зарядов всех емкостей:

Q>fg> = C>pp>(V>fg> – V>g>) + C>gd>(V>fg> – V>d>) + C>fld>(V>fg> – V>sub>>)

+ C>tun>(V>fg> – (V>D> - >sn>))+ C>gs>(V>fg>-V>s>)

+ C>gox>(V>sub>> +>s>)); (19)

Во время записи в области n+ накапливается заряд и >sn> принимается равным нулю. Канал формируется так, что поверхность канала и свободный исток составляют напряжение на стоке V>d> = 0. Таким образом, V>fg> может быть вычислено из соотношения (19).

Во время стирания >sn> принимается постоянной. Состояние поверхности канала определяет следующий способ нахождения Q>fg>: во-первых, истощение принято и последний часть в уравнении (17) может быть заменена следующим выражением:

Q>dep> = A>ch> (2q >si> >0 > N>b> >s>)-2 (20)

Для предполагаемого условия V>fg> связано с >s> следующим соотношением:

V>fg >= V>fb> + >s> + A>ch>/C>gox > (2q >si > >0 > >s>)-2 (21)

Это выражение включенное в выражение (17) и равнодействующее квадратичное уравнение решено для (>s>)-2. Если уравнение не имеет положительных решений, то поверхность канала накоплена и >s> берется равным 0. Напряжение на истоке эквивалентно >s>. Уравнение (17) решено для V>fg> с учетом >s>.

Рисунок 8

4. ЭКСПЕРИМЕНТАЛЬНАЯ ЧАСТЬ

4.1 Запоминающая ячейка

В настоящее время на НПО “Интеграл” используются две разновидности конструкции запоминающей ячейки для ЭСППЗУ: обычная и её масштабированная (уменьшенная) топологическая модификация. Конструктивно ячейки состоят из адресного транзистора (транзистора выборки) и транзистора с «плавающим» затвором, на котором хранится информация.

Для сравнения нами был проведен анализ аналогов ЭСППЗУ, производимых некоторыми зарубежными фирмами: Siemens и Philips.

На всех проанализированных образцах ЭСППЗУ, произведенных фирмой Philips (PCF 8582, PCF 8594, PCF 85116), используются различные топологические рисунки запоминающего элемента. Аналогична ситуация и у фирмы Siemens (SDA 2586, SDE 2526).

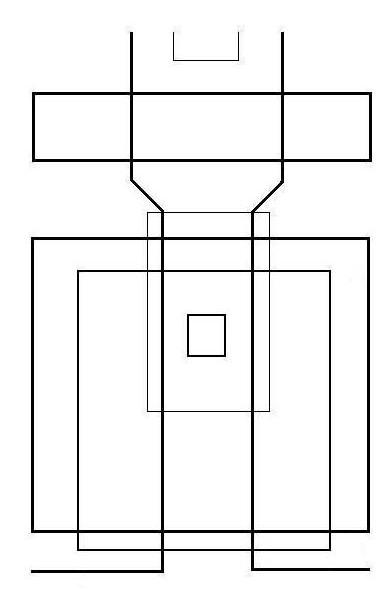

На рисунке 9 приведена электрическая схема запоминающей ячейки ЭСППЗУ одного из иностранных аналогов, а на рисунке 10 – ее топологический чертеж.

Основные отличия в электрических схемах запоминающих ячеек ЭСППЗУ отечественной разработки и ее иностранного аналога состоит в том, что они имеют различную организацию.

Топологическая площадь запоминающего элемента аналога 5,0 мкм 11,25 мкм 56,25 мкм2, а площадь ячейки, разработанной на НПО “Интеграл” равна 11,0 мкм х 18,5 мкм = 203,5 мкм2. Это связано с разными нормами топологического проектирования элементной базы (0,6 мкм у аналога и 1,0 мкм на НПО “Интеграл”).

Необходимо отметить, что корректное сравнение различных запоминающих ячеек затруднительно. Выбор конкретного варианта реализации топологии зависит от множества факторов: норм проектирования элементной базы и технологического процесса их изготовления, схем электрических блоков обрамления матрицы запоминающего устройства (дешифраторы, разрядная схема, усилители считывания, схемы управления напряжением программирования), статических, динамических, надежностных характеристик всего устройства, режимов программирования и многого другого.

Более детальный анализ и формирование требований к параметрам ячейки могут быть осуществлены после моделирования микросхемы.

Разрядная шина

Т1

Адресная

шина

Управляющий

затвор

Т2

Т3

Подключение к шине «земля» при чтении информации

Рисунок 9. Схема электрическая запоминающей ячейки

Т1

Т2

11.25 мкм

Р

5.0 мкм

исунок 10. Топология запоминающей ячейки4.1.1 Методика исследования элементной базы ЭСППЗУ

Физика работы запоминающего элемента ЭСППЗУ требует подачи на нее довольно высоких уровней напряжения при записи информации. Что накладывает ряд специфических требований на элементную базу как самой запоминающей ячейки, так и кристалла микросхемы целиком.

Напряжение поступающее на запоминающую ячейку в режиме программирования составляет ~ 15 20 В и формируется встроенным на кристалле источником и подается к ячейке посредством цепочки коммутирующих п-канальных транзисторов. Типовая схема передачи напряжения от источника к запоминающей ячейке приведена на рисунке 11.

Необходимость использования для передачи напряжения программирования п-канальных транзисторов определяет потери в его величине на выводах ячейки относительно напряжения источника.

Напряжение Uпрог. поступающее на запоминающую ячейку определяется следующим образом:

Uпрог = Uист – 2 (U>TN >+ Uпрог) (22),

где: U>TN> - порог п-канального транзистора (без смещения подложки);

- коэффициент влияния подложки;

Uист- напряжение источника вырабатывающего высокое напряжение на кристалле.

Максимально достижимое значение напряжения источника ограничивается пробивными и пороговыми напряжениями его элементов. Достижение режима работы запоминающей ячейки при записи информации с учетом соотношения емкостей управляющего и туннельного окисла иллюстрируется на рисунке 12

Схема передачи

Рисунок 11

Рабочий режим запоминающей ячейки

Рисунок 12

Основными характеристиками, которые определяют работоспособность и надежность ячейки, являются соотношение емкостей между обкладками транзистора с “плавающим” затвором (параметр отвечает за величину напряжения на “плавающем” затворе при программировании) и разность токов при чтении информации различных состояний ячейки.

Для эффективного программирования соотношение ёмкостей должно быть 1,0. При соотношении 1,0 к туннельному окислу в режиме программирования прилагается напряжение, равное половине “высокого”, что достаточно для протекания туннельного тока при d>ox >= 80 – 85 A. У анализируемого образца данное соотношение равно 1,1.

Ток ячейки, при прочих равных условиях, определяется эффективной шириной адресного и “плавающего” транзисторов и, безусловно, уровнем заряда, записанного на “плавающем” затворе.

Для элементной базы ЭСППЗУ в отличие от стандартных КМОП ИС очень важными параметрами элементной базы являются:

1. Значения и разброс пороговых напряжений рабочих транзисторов.

2. Пробивные напряжения элементов, с помощью которых формируется и подается к запоминающей ячейке программирующее напряжение.

3. Пороговые напряжения паразитных структур, прилегающих к элементам обеспечивающим формирование Uпрог.

4. Тип подложки и собственная структура транзисторов, определяющие коэффициент влияния напряжения смещения истока относительно напряжения подложки на пороговое напряжение ключевых транзисторов, осуществляющих передачу программирующего напряжения к выбранному запоминающему элементу.

5. Емкости туннельного и межслойного (между управляющим и плавающим затвором) окислов.

4.2 Результаты исследования элементной базы

Учитывая приведенные выше требования, были отобраны тестовые структуры, на которых проводились комплексные измерения параметров элементной базы ЭСППЗУ.

4.2.1 Исследование характеристик туннельного окисла запоминающего элемента

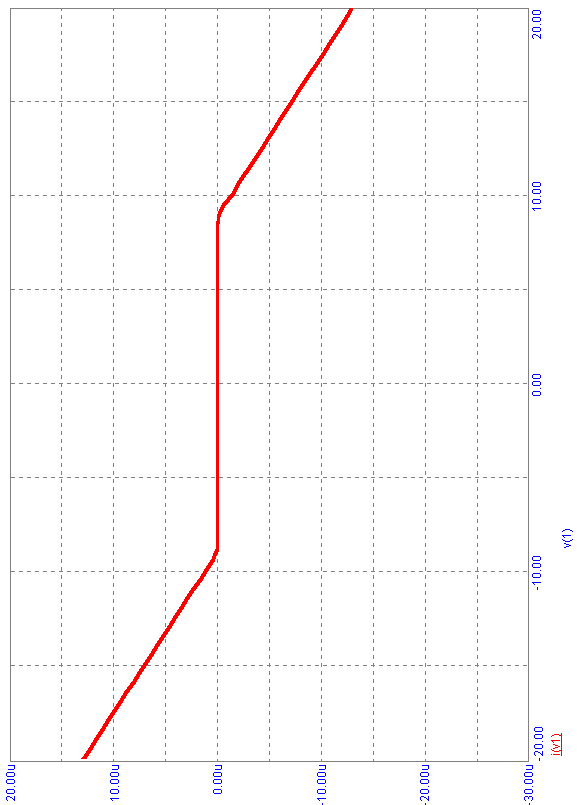

Вольтамперные характеристики туннельного окисла снимались непосредственно на структуре, входящей в состав запоминающей ячейки. Измерения проводились для напряжения обоих полярностей при температуре +20, +85 и +125С.

Результаты измерений (представлены в форме графиков в приложении 2) были подвергнуты компьютерной математической обработке и приведены на рисунке 13.

Полученные результаты показывают симметричность вольт-амперной характеристики туннельного окисла при разной полярности приложенного напряжения и слабую зависимость от температуры, что подтверждается научными литературными источниками. Для упрощения рисунке 14, на нем не приведены кривые, полученные при температуре +85оС.

4.2.2 Эквивалентная схема замещения туннельного окисла

Важным этапом разработки микросхем ЭСППЗУ является моделирование электрической схемы. В настоящее время полное моделирование затруднено в связи с отсутствием модели запоминающей ячейки. Основным препятствием к ее созданию является отсутствие схемы замещения туннельного окисла в составе библиотек программных пакетов систем проектирования.

Однако на элементах библиотек этих систем возможно создание схем, которые позволят обеспечить электрические характеристики имитирующие поведение туннельного окисла в составе запоминающей ячейки и запоминающая ячейка в целом в режимах записи и чтения информации.

Вольтамперные характеристики туннельного окисла

Рисунок 13

Нами предложено три варианта эквивалентной схемы замещения туннельного окисла. Туннельный окисел может быть замещен двумя встречно включенными МОП транзисторами (рисунок 14), системой диодов и стабилитронов (рисунок 15) или двумя встречно включенными источниками тока управляемыми напряжением (рисунок 16)

В данном дипломном проекте будет рассмотрена схема замещения на источниках тока управляемых напряжением.

Рисунок 14

Рисунок 15

Р

исунок

16

4.2.3 Построение и расчет ячейки ЭСППЗУ

Модель ячейки представлена на рисунке 16. Ее моделирование проводилось со всеми предложенными выше схемами замещения. Однако в силу сложности обеспечения параметров туннельного окисла с помощью систем параметров элементов входящих в состав этих схем замещения была найдена еще одна. В основе этой схемы замещения лежит источник тока управляемый напряжением. Причем схема состоит из двух таких источников, включенных параллельно, но с разными направлениями токов. Такое включение позволяет заменить туннельный окисел при обеих полярностях напряжения в режимах стирания и записи информации. Замещение туннельного окисла, таким образом, позволяет точно описать токовую характеристику и исключить влияние каких-либо других параметров из системы параметров других схем замещения, таких как емкость, сложность обеспечения требуемого порогового напряжения и т.д.

Результаты построения токовой характеристики источников замещающих туннельный окисел в модели, в сравнении с измеренными на образцах, приведены на рисунке 17. Как видно из рисунка обе характеристики совпадают с высокой точностью.

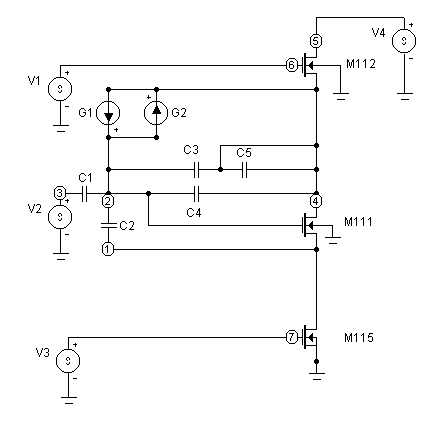

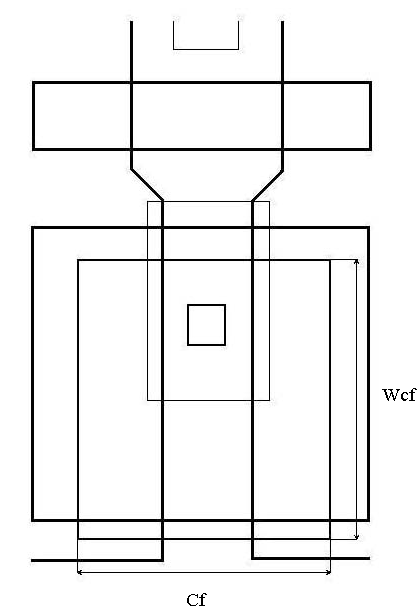

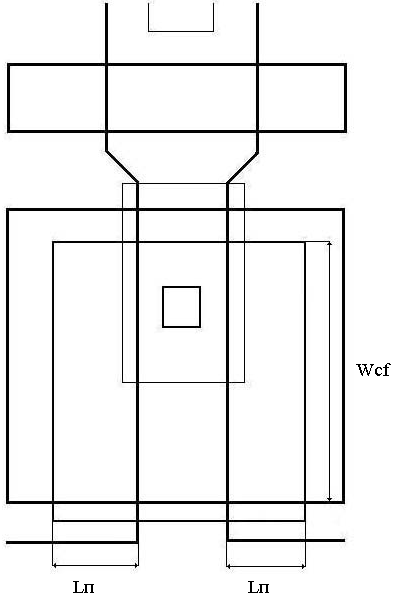

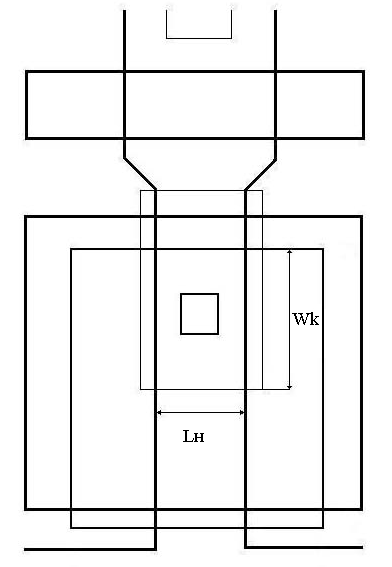

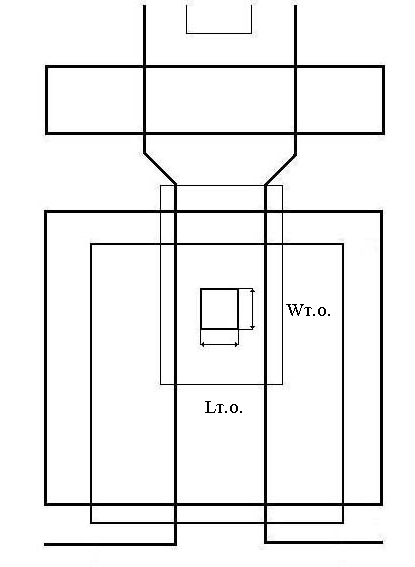

Разработанная модель представлена на рисунке 18, а на рисунке 19 представлены SPICE-параметры этой модели. В этой схеме два источника тока управляемых напряжением G>1> и G>2> моделируют параметры туннельного окисла, транзистор М>112> является транзистором выборки, а транзистор М>111> активным транзистором-транзистором с плавающим затвором. Емкость С>1> между плавающим и управляющим затворами представленная на рисунке 20 и рассчитывается по формуле(22), емкость C>14> рассчитывается по формуле (23) и представлена на рисунке 21

C>15>=( >0 > W>cf>> > L>f>)/d>1> (23)

C>14>=( >0 > W>cf>> > 2L>перекр>)/d>1> (24)

Где W>cf>> >–это ширина области перекрытия. L>f> и L>перекр> - длина области перекрытия, а d>1 >–это толщина диэлектрика между затворами.

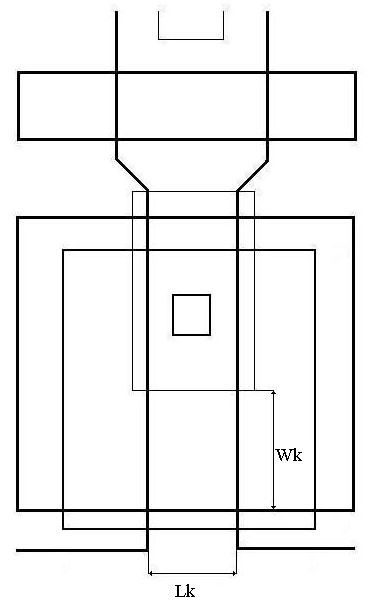

Емкость C>17>, показанная на рисунке 22 рассчитывается по формуле (24) и учитывается в расчете внутренних емкостей транзистора М>111>. Активная емкость нырка без учета емкости туннельного окисла рассчитывается по формуле (25) и показана на рисунке 23.

C>17>=( >0 > W>к > L>к>)/d>1> (25)

C>16>=( >0 > W>к > L>н>)/d>1> (26)

Где W>к >ширина канала, а L>к> и L>н> длина канала и нырка соответственно.

Фактическая же емкость туннельного окисла показана на рисунке 24 и рассчитывается по формуле (26).

C>18>=( >0 > W>т.о. > L>т.о.>)/d>1> (27)

Где W>т.о. >и L>т.о> ширина и длина туннельного окисла соответственно

Рисунок 17

Рисунок 18

C14 1 2 0.005P

C15 2 3 0.3P

C16 4 2 0.04P

C17 4 4 .1P

C18 4 2 0.005P

G5 4 2 TABLE {V(4,2)} =

+(0,0)(1,0)(2,0)(3,0)(4,0)(5,0)(6,0)(7,0)(8,10N)(8.5,50N)(9,200N)(9.5,600N)(9.8

+ ,1000N)(20,13U)(25,19U)

G6 2 4 TABLE {V(2,4)} =

+(0,0)(1,0)(2,0)(3,0)(4,0)(5,0)(6,0)(7,0)(8,10N)(8.5,50N)(9,200N)(9.5,600N)(9.8

+ ,1000N)(20,13U)(25,19U)

M111 4 2 1 0 12MSC L=2U W=3U

M112 5 6 4 0 12MSC L=4U W=5U

M115 1 7 0 0 12MSC L=1.4U W=6U

RG5 4 2 1G;added by G5

RG6 2 4 1G;added by G6

V1 6 0 PWL 0M 0 1M 5 9M 5 11M 5 19M 5 21M 15 29M 15 31M 5 40M 5

V2 3 0 PWL 0M 0 1M 14 9M 14 11M 0 19M 10 21M 0 29M 0 31M 0 {40M -10}

V3 7 0 PWL 0M 0 9M 0 11M 5 19M 5 21M 0 29M 0 31M 5 40M 5

V4 5 0 PWL 0M 0 9M 0 11M 5 19M 5 21M 15 29M 15 31M 5 40M 5

**** sram32k*8

.MODEL 12MSC NMOS (LEVEL=3 VTO=650M L=1.4U W=50U GAMMA=350M LAMBDA=20M RD=30

+ RS=30 IS=0 PB=750M CGSO=200P CGDO=200P CJ=360U CJSW=350P MJSW=250M TOX=25N

+ Nsub>=4.000000E+016 TPG=1 XJ=350N LD=220N WD=200N UO=550 VMAX=150K DELTA=3.7

+ THETA=35M ETA=15M KAPPA=700M T_MEASURED=27)

*.OPTIONS ACCT LIST OPTS ABSTOL=1UA CHGTOL=.01pC CPTIME=1G DEFL=100u DEFW=100u

+ DIGDRVF=2 DIGDRVZ=20K DIGERRDEFAULT=20 DIGERRLIMIT=10000 DIGFREQ=10GHz

+ DIGINITSTATE=0 DIGIOLVL=2 DIGMNTYMX=2 DIGMNTYSCALE=0.4 DIGOVRDRV=3

+ DIGTYMXSCALE=1.6 GMIN=1p ITL1=100 ITL2=50 ITL4=10 ITL5=0 LIMPTS=0 PIVREL=1m

+ PIVTOL=.1p RELTOL=1m TNOM=27 TRTOL=7 VNTOL=1u WIDTH=80

.END

Рисунок 19

Рисунок 20

Рисунок 21

Рисунок 22

Рисунок 23

Рисунок 24

Для оценки возможностей модели ячейки разработана схема для расчета ее характеристик. Сигналы, обеспечивающие работу ячейки в составе ЭСППЗУ, имитируются источниками V>1>…V>3>.

Временная диаграмма построена таким образом, что сначала осуществляется стирание информации, а потом чтение – определение порогового напряжения после стирания информации, запись информации и опять чтение. При этом, изменяя амплитуды и длительность сигналов источников V>1>…V>3> можно оценить все необходимые параметры ячейки ЭСППЗУ в реальных режимах работы устройства и определить пороговые напряжения, токи считывания информации для определения необходимого порогового напряжения на управляющем затворе для обеспечения устойчивого напряжения во всем диапазоне питающих напряжений. Модель позволяет оптимизировать соотношения геометрических размеров элементов ячейки и минимизировать ее площадь по заданным параметрам технологической структуры элементов.

Пример расчета приведен на рисунке 25, результаты же расчета в сравнении с измеренными параметрами приведены на таблице 1. Данные приведены для длительности времени программирования 1ms.

Как видно из таблицы 1 результаты лежат достаточно близко к измеренным. За тестовую ячейку преднамеренно выбирается запоминающая ячейка экспериментальных образцов микросхем, оптимизация конструкции которых проводится на основе экспериментальных данных и занимает значительный отрезок времени и требует больших финансовых затрат.

Сравнительный анализ полученных и экспериментальных результатов показывает, что ячейка требует оптимизации, т.к. при задании уровня напряжения на управляющем затворе равного 1,5 В пороговое напряжение активного транзистора с плавающим затвором превышает его только при U>прогр>14 В.

Для принятой технологической структуры это значение напряжения программирования является граничным, т.е. область работоспособности микросхемы будет ограниченной особенно в области низких значений питающих напряжений, что подтверждается результатами измерения образцов кристаллов микросхем ЭСППЗУ.

Для улучшения ситуации необходимо либо увеличить U>прогр> , либо изменить соотношение емкостей управляющего и плавающего затворов в сторону увеличения емкости управляющего затвора, либо изменить конструкцию и схемотехнику узлов интегральной схемы с целью снижения напряжения на управляющем затворе в режиме чтения.

Таблица 4.1

|

ПРОГРАММИРОВАНИЕ |

||||||||||

|

Uпрогр=12 В tпрогр=1 mS |

Uпрогр=13 В tпрогр=1 mS |

Uпрогр=14В tпрогр=1 mS |

Uпрогр=15 tпрогр=1 mS |

Uпрогр=16В tпрогр=1 mS |

||||||

|

Uпор,В Iст=0.1 мкА, Uс=Uз, Uи=0,Uп=0В |

Uпор,В Iст=0.1 мкА, Uс=Uз, Uи=0,Uп=0В |

Uпор,В Iст=0.1 мкА, Uс=Uз, Uи=0,Uп=0В |

Uпор,В Iст=0.1 мкА, Uс=Uз, Uи=0,Uп=0В |

Uпор,В Iст=0.1 мкА, Uс=Uз, Uи=0,Uп=0В |

||||||

|

Экпери-мент |

Моделиро-вание |

Экпери-мент |

Моделиро-вание |

Экпери-мент |

Моделиро-вание |

Экпери-мент |

Моделиро-вание |

Экпери-мент |

Моделиро-вание |

|

|

0,10 |

0,21 |

0,60 |

0,49 |

1,30 |

1,41 |

1,90 |

2,08 |

2,60 |

2,73 |

|

|

0,02 |

0,032 |

0,60 |

0,51 |

1,25 |

1,34 |

1,90 |

2,03 |

2,60 |

2,71 |

|

|

0,12 |

0,23 |

0,60 |

0,71 |

1,25 |

1,35 |

1,90 |

2,05 |

2,60 |

2,70 |

|

|

0,00 |

0,05 |

0,25 |

0,35 |

0,75 |

0,80 |

1,50 |

1,63 |

2,00 |

2,11 |

|

|

0,00 |

0,031 |

0,24 |

0,33 |

1,15 |

1,28 |

1,60 |

1,71 |

2,15 |

2,23 |

|

|

0,00 |

0,04 |

0,30 |

0,41 |

1,10 |

1,22 |

1,30 |

1,41 |

2,20 |

2,30 |

|

|

0,25 |

0,31 |

0,95 |

1,00 |

1,60 |

1,72 |

2,20 |

2,29 |

2,90 |

3,00 |

|

|

0,25 |

0,33 |

0,95 |

1,07 |

1,60 |

1,71 |

2,20 |

2,31 |

2,80 |

2,93 |

|

|

0,25 |

0,35 |

1,05 |

1,16 |

1,50 |

1,63 |

2,40 |

2,52 |

2,90 |

3,01 |

|

|

СТИРАНИЕ |

||||||||||

|

Uстир=12 В tстир=1 mS |

Uстир=13 В tстир=1 mS |

Uстир=14В tстир=1 mS |

Uстир=15 tстир=1 mS |

Uстир=16В tстир=1 mS |

||||||

|

Uпор,В Iст=0.1 мкА, Uс=2В, Uи=0,Uп=0В |

Uпор,В Iст=0.1 мкА, Uс=2В, Uи=0,Uп=0В |

Uпор,В Iст=0.1 мкА, Uс=2В, Uи=0,Uп=0В |

Uпор,В Iст=0.1 мкА, Uс=2В, Uи=0,Uп=0В |

Uпор,В Iст=0.1 мкА, Uс=2В, Uи=0,Uп=0В |

||||||

|

Экпери-мент |

Модели-рование |

Экпери-мент |

Модели-рование |

Экпери-мент |

Модели-рование |

Экпери-мент |

Модели-рование |

Экпери-мент |

Модели-рование |

|

|

+0,85 |

+0,9 |

+1,24 |

+1,3 |

-1,50 |

-1,4 |

-2,14 |

-2,03 |

-3,50 |

-3,41 |

|

|

+0,95 |

+1,0 |

+0,32 |

+40,41 |

-1,54 |

-1,49 |

-2,40 |

-2,34 |

-3,42 |

-3,31 |

|

|

+1 |

+1,1 |

+0,4 |

+0,49 |

-1,40 |

-1,3 |

-2,70 |

-2,61 |

-4,00 |

-3,91 |

|

|

+1,1 |

+1,22 |

+0,4 |

+0,51 |

-1,37 |

-1,25 |

-2,32 |

-2,25 |

-3,30 |

-3,19 |

|

|

+1,1 |

+1,25 |

+0,4 |

+0,53 |

-1,28 |

-1,19 |

-2,30 |

-2,21 |

-3,34 |

-3,25 |

СПИСОК ИСПОЛЬЗУЕМОЙ ЛИТЕРАТУРЫ

Статьи из IEEE JOURNAL OF SOLID-STATE CIRCUITS:

“A 16kbit EEPROM Using n-Channel Si-Gate MOS Technology” June1980, number 3, vol. sc-15; TAYAAKI HAGIWARA, YUJI YANSUDA, RYUJI KONDO, SHIN-ICHI MINAMI, TOSHIRO AOTO, and YOKICHI ITOH.

“ A 16kbit EEPROM Employing New Array Architecture and Designed-In Reliability Features” October1982, number 5, vol. sc-17; GIORA YARON, S. JAYASIMHA PRASAD, MARK S. EBEL, and BRUCE M. K. LEONG.

“ A 128kbit Flash EEPROM Using Double-Polysilicon Technology” October1987, number 5, vol. sc-22; GHEORGHE SAMASHISA, CHIEN-SHENG SU, YU SHENG KAO, GEORGE SMARANDOIU, CHENG-YUAN MICHAEL WANG, TINGWONG, CHENMING HU.

“A 50-ns CMOS 256K EEPROM ” October 1988 number 5 vol.23; TAH-KANG J.TING, THOMAS CHANG,TIEN LIN,CHING S. JENQ,KENNETH L. C. NAIFF.

“An 80ns 32K EEPROM Using the FETMOS Cell”October1982 number 5, vol. sc-17 ;CLINTON KUO,JOHN R. YEARGAIN,WILLIAM J. DOWNEY,KERRY A.ILGENSTEIN,JEFFREY R.JORVIG,STEPHEN L.SMITH,ALAN R. BORMANN.

“An Enhanced 16K EEPROM” October 1982 number 5 vol.sc-17; LUBIN GEE, PEARL CHENG, YOGENDRA BOBRA,RUSTAM MENTA.

“A 5-V-ONLY one-Transistor 256K EEPRON with Rage-Mode Erase” August 1989 number 4 vol.24; TAKESHI NAKAYAMA, YOSHIKAZU MIYAWAKI, KAZUO KOBAYASHI, YASUSHI TERADA, HIDEAKI ARIMA,TAKAYUKI, MATSUKAWA,TSUTOMU YOSHIHARA.

“An Experimental 4-Mbit CMOS EEPROM with a NAND-structured Cell” October 1989 number 5 vol.24;MASAKI MOMODOMI,YASUO ITOH,RIICHIRO SHIROTA,YOSHIHISA IWATA,RYOZO MAKAYAMA,RYOUHEI KIRISAWA,TOMOHARU TANAKA,SEIICHI ARITOME,TETSUO ENDOH,KAZUNORI OHUCHI,FUJIO MASUOKA.

“120-ns 128K /8bit/64K/16bit CMOS EEPROM’S” October 1989 number 5 vol.24;YASUSHI TERADA, KAZUO KOBAYASHI,TAKESHI NAKAYAMA,MASANORI HAYASAIKOSHI,YOSHIKAZU MIYAWAKI,NATSUO AJIKA, HIDEAKI ARIMA,TAKAYUKI MATSUKAWA,TSUTOMU YOSHIHARA.

“Yield and Reliability of MNOS EEPROM Products” December 1989 number 6 vol.24 ; YOSHIAKI KAMIGAKI,CHIN-ICHI MINAMI,TAKAAKI HAGIWARA,KAZUNORI FURUSAWA,TAKESHI FUURUNO,KEN UCHIDA,MASAAKI TERASAWA,KOUBU YAMAZAKI.

“A High-Density NAND EEPROM with Block-Page Programming for Microcomputer Applications” April 1990number 2 vol.25 ;YOSHIHISA IWATA,MASAKI MOMODOMI,TOMOHARU TANAKA,HIDEKO OODAIRA,YASUO ITOH,RYOZO NAKAYAMA,RYOUHEI KIRISAWA,SEIICHI ARITOME,TETSUO ENDOH, RIICHIRO SHIROTA,KAZUNORI OHUCHI,FUJO MASUOKA.

“A 60-ns 16Mb Flash EEPROM with Program and Erase Sequence Controller” November 1991 number 11 vol.26;TAKESHI NAKAYAMA,SHIN-ICHI KOBAYASHI,YOSHIKAZU MIYAWAKI,YASUSHI TERADA,NATSUO AJIKA,MAKOTO OHI,HIDEAKI ARIMA,TAKAYUKI MATSUKAWA,TSUTOMU YOSHIHARA,KIMIO SUZUKI.

“A Dual-Mode Sensing Scheme of Capacitor-coupled EEPROM Cell” April 1992 number 4 vol.27; MASANORI HAYASUIKOSHI ,HIDETO HIDAKA,KAZUTAMI ARIMOTO, KAZUYASU FUJISHIMA.

“A 512-kb Flash EEPROM Embedded in a 32-b Microcontroller” April 1992 number 4 vol.24; CLINTON KUO,MARK WEIDNER,THOMAS TOMS,HENRY CHOE,KO-MIN CHANG,ANN HARWOOD,JOSEPH JELEMENSKY,PHILIP SMITH.

“A 5-v-Only Operation0.6 mm Flash EEPROM with Row Decoder Scheme in Triple-Well Structure” November 1998 number 11 vol.27; AKIRA UMEZAWA ,SHIGERU ATSUMI,MASAO KURIYAMA,HIRONORI BANDA,KEN-ICHI IMAMIYA,KIYOMI NARUKE,SEIJI YAMADA,ETSUSHI OBI,MASAMITSU OSHIKIRI,TOMOKO SUZUKI,SUMIO TANAKA.

“High-Voltage Regulation and Process Consideration for High-Density 5V-Only EEPROM’S ”October 1983 number 5 vol. sc-18; DUANE H . OTO,VINOD K. DHAM, KEITH H. GUDGER,MICHAEL J. REITSMA, GEOFFREY S. GONGWER,YAW WEN HU,JAY F. OLUND,H.STANLEY JONES,SIDNEY T. K. NIEH.

“A 16 kbit Smart 5V-Only EEPROM with Redundancy”. October 1983 number 5 vol.sc-18;ELROY M. LUCERO,NAGESH CHALLA ,JULIAN FIELDS,JR.

“A 35-ns 64K EEPROM” October 1985 number 5 vol.sc-20;CAMPBELL,DAVID L. TENNANT ,JAY F.OLUND,ROBERT B. LEFFERTS,BRENDAN T. CREMEN,PHILIP A. ANDREWS.

“A Temperature-and Process Tolerant 64K EEPROM .”October 1985 number 5 vol.sc-20;COLIN S.BILL,PAUL I. SUCIU, MICHAEL S. BRINER, DARRELL D. RINERSON.

“An Experimental 5-V-Only 256-kbit CMOS EEPROM with a High-Performance Single-Polysilicon Cell”. October 1986 number 5 vol.sc-21; JUN-ICHI MIYAMOTO, JUN-ICHI TSUJI-MOTO,NAOHIRO MATSUKAWA,SHIGERU MORITA,KAZUYOSI SHINADA,HIROSHI NOZAWA,TETSUA IIZUKA.

“A Four-state EEPROM using Floating-Gate Memory Cells ”June 1987 number 3 vol.sc-22; CHRISTOPH BLEIKER, HANS MELCHIOR.77