Двухканальная осциллографическая приставка к ПК

МИНИСТЕРСТВО ОБРАЗОВАНИЯ И НАУКИ РОССИЙСКОЙ ФЕДЕРАЦИИ

Федеральное агентство по образованию.

Двухканальная осциллографическая приставка к ПК.

Пояснительная записка

Руководитель

Подпись

Дата

Студент

Подпись

2008

Содержание

1.Разновидности аналогово-цифровых устройств

1.1Последовательный аналого-цифровой преобразователь со ступенчатым пилообразным напряжением…………………………………………………….3

1.2Аналого-цифровой преобразователь следящего типа……………………...4

1.3 Аналого-цифровой преобразователь параллельного типа ……………….5

2.Принцип работы двухканального осциллографа ………….………………..7

3.Работа LPT ……………………………………………………………………...7

3.1 Параллельный интерфейс: LPT-порт………………………………………..7

3.2 Традиционный LPT-порт…………………………………………………….9

3.3 Функции BIOS для LPT-порта……………………………………………..10

3.4 Режимы передачи данных ………………………………………….………11

3.5 Конфигурирование LPT-портов ……………………………………………11

3.6 Использование параллельных портов …………………………….……….12

3.7 Неисправности и тестирование параллельных портов ………………….12

3.8 Параллельный порт и РпР …………………………………………………13

4.Описание функциональной схемы

5.Выбор и обоснование элементной базы

6.Описание работы электрической схемы

7.Расчет параметров:

7.1мощность

7.2надежность

7.3быстродействие

1 Разновидности аналогово-цифровых устройств

1.1 Последовательный аналого-цифровой преобразователь со ступенчатым пилообразным напряжением

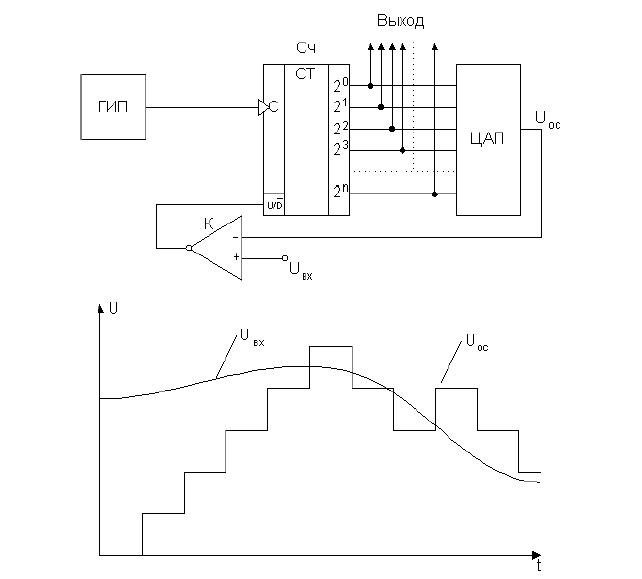

Структурная схема преобразователя данного типа приведена на рисунке 1.1, а.

Тактовым импульсом (ТИ) счетчик Сч сбрасывается в нулевое состояние. Нулевое напряжение Uoc = 0 возникает на выходе ЦАП, преобразующего число счетчика в пропорциональное напряжение. Устанавливается неравенство Uвх > Uос, при котором компаратор К подает на вход элемента И уровень логической "1". При этом импульсы генератора импульсной последовательности ГИП проходят через элемент И на вход счетчика. Каждый поступивший на вход счетчика импульс вызывает увеличение хранившегося в нем числа на единицу, на одну элементарную ступеньку напряжение возрастает на выходе ЦАП. Таким образом, напряжение Uос растет по ступенчатому закону, как показано на рисунке 1.1, б. В момент времени, когда напряжение Uос достигает уровня, превышающего Uвх, компаратор выдает уровень логического "0", и в дальнейшем прекращается доступ импульсов генератора в счетчик. Полученное к этому моменту времени в счетчике число пропорционально напряжению Uвx.

1.2 Аналого-цифровой преобразователь следящего типа

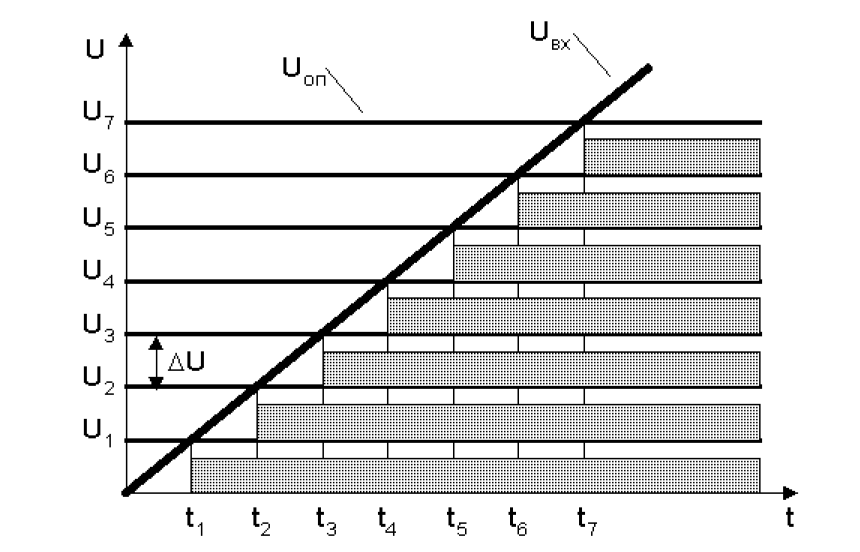

Рассмотренный выше тип АЦП работает в циклическом режиме. В немкаждый очередной тактовый импульс устанавливает преобразователь висходное состояние, после чего начинается процесс преобразования.Быстродействие такого преобразователя ограничивается, главным образом, быстродействием счетчика (а именно, быстродействием триггеров егомладших разрядов, в которых переключение происходит с высокой частотой).На практике часто используется нециклический преобразователь,структурная схема которого представлена на рисунке 1.2, а.

Рисунок 1.2 – Схема АЦП следящего типа (а) и диаграмма его работы (б)

Эта схема отличается от схемы преобразователя предыдущего типа тем, что в ней используется реверсивный счетчик Сч, управляемый сигналами свыхода компаратора К. При Uвх > Uос счетчик устанавливается в режим прямого счета, поступающие на вход импульсы генератора ГИП последовательно увеличивают в нем число, растет напряжение Uос, до уровня напряжения Uвх. При Uвх < Uос счетчик переводится в режим обратного счета, при котором убывает число в счетчике и, следовательно, убывает напряжение Uос, пока не будет достигнуто значение Uвх.

Таким образом, все происходящие во времени изменения напряжения Uвхотслеживаются напряжением Uос на выходе ЦАП. В необходимые моменты времени с выхода счетчика могут сниматься числа, пропорциональные значениям Uвх.

1.3 Аналого-цифровой преобразователь параллельного типа

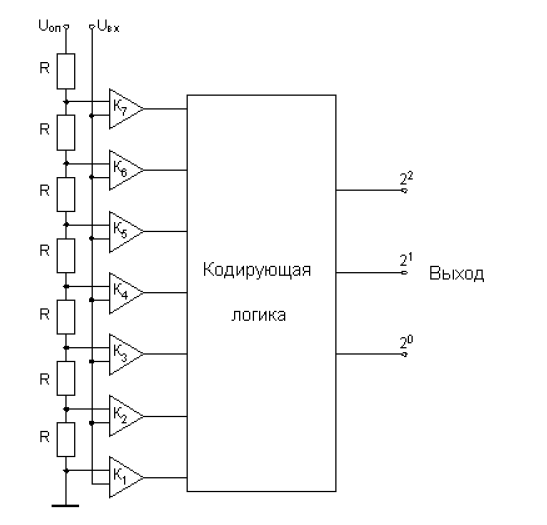

Диаграмма работы АЦП параллельного типа представлена на рисунке 1.3, схема АЦП представлена на рисунке 1.4.

Рисунок 1.3 – Диаграмма работы АЦП параллельного типа

Рисунок 1.4 – Схема АЦП параллельного типа.

АЦП параллельного типа содержит делитель, состоящий из наборапоследовательно включенных резисторов с одинаковым сопротивлением R, компараторов К и кодирующей логики. На один из входов каждогокомпаратора подается опорное напряжение Uоп, снимаемое с делителя, причем эти напряжения отличаются друг от друга на величину ∆ U (см.рисунок 1.3). Вторые входы компараторов объединены и на них подано входное напряжение Uвх. Работу АЦП данного типа можно рассмотреть по диаграмме, изображенной на рисунке 1.3. При достижении входным напряжением значения опорного напряжения первого компаратора U1 (момент времени t1) последний срабатывает и подает сигнал активного уровня со своего выхода на первый вход устройства кодирующей логики, на выходе которого при этом появляется число "1" в двоичном коде. При дальнейшем возрастании входного напряжения в момент времени t2 сработает второй компаратор и на выходе АЦП появится "2" и т.д. В данном случае значение ∆ U представляет собой шаг квантования.

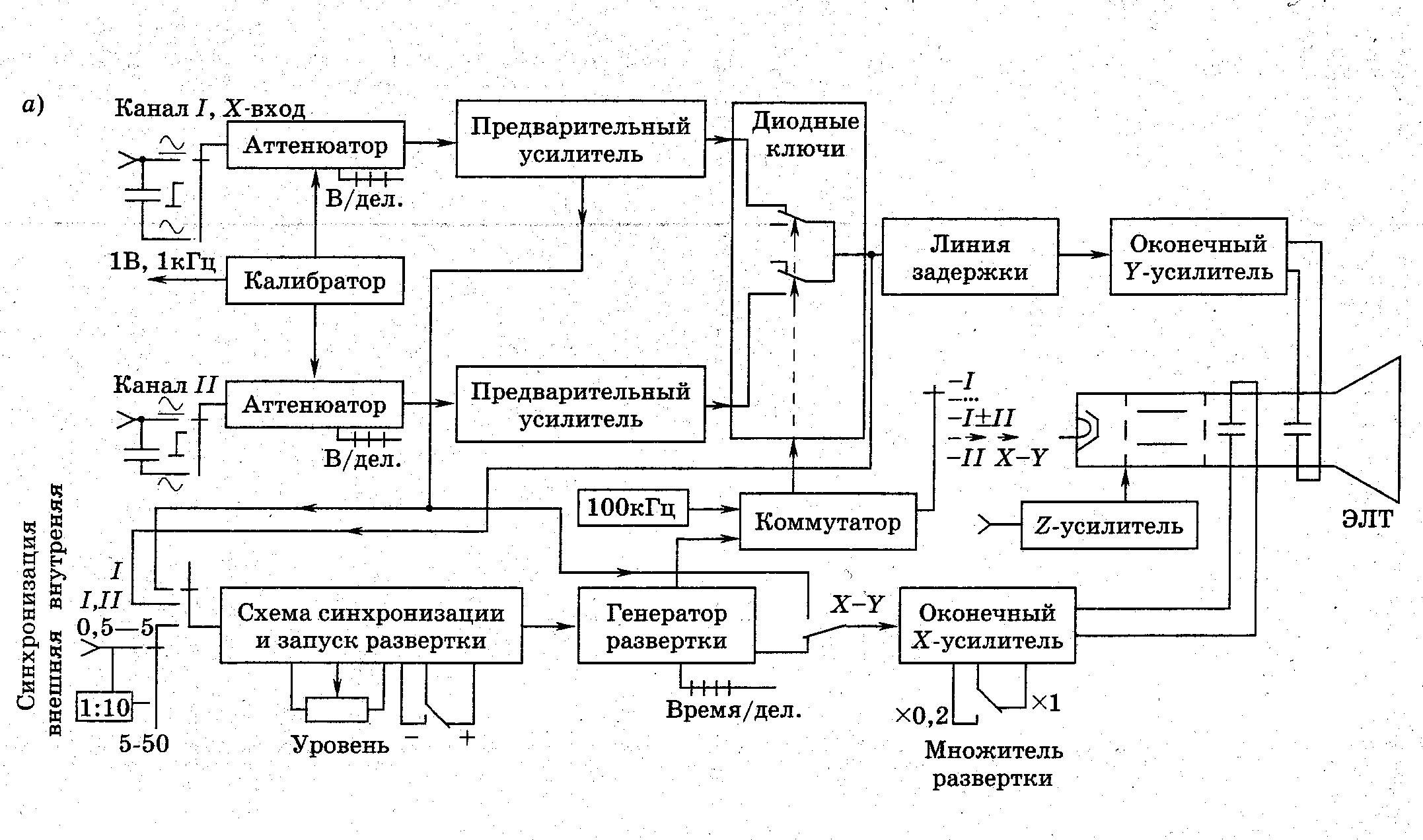

2 Принцип работы двухканального осциллографа

Двухканальный осциллограф (рис. 2.1, а) дает возможность одновременно наблюдать и сравнивать на экране изображения двух сигналов одной и той же частоты либо кратных частот, измерять их амплитудные и временные параметры.

Осциллограф содержит два идентичных канала вертикального отклонения (рис. 2.1, а), в которые входят аттенюатор и предварительный усилитель. Линия задержки и оконечный У-усилитель к каналам I и II подключаются с помощью электронного коммутатора. Канал горизонтального отклонения содержит схему синхронизации и запуска развертки, генератор развертки и оконечный X-усилитель. Сигналы с выходов каналов поступают на вертикально и горизонтально отклоняющие пластины ЭЛТ. Для проверки коэффициентов отклонения «В/дел.» каналов I и II и коэффициента развертки «Время/дел.» канала горизонтального отклонения служит калибратор, который имеет внутренний и внешний выходы.

Аттенюатор — это частотно-компенсированный делитель напряжения, состоящий из RС-элементов, откалиброванный в коэффициентах отклонения «В/дел.».

Коммутатор представляет собой мультивибратор, управляет диодными ключами каналов I и II и имеет пять режимов переключения: «I», «II Y—X»,

«I ± II», «...», «→→».

На экране регистрируется один сигнал в следующих режимах:

«I» — подключен только канал I;

«II Y—X» — подключен только канал II (выполняющий роль У-канала, а развертывающее напряжение подается на канал I, выполняя роль Х-канала);

«I ± II».— подключены оба канала I и II (на экране регистрируется суммарный сигнал либо разностный, если предварительно инвертировать сигнал канала II);

«...» и «→ →» — на экране наблюдаются два сигнала.

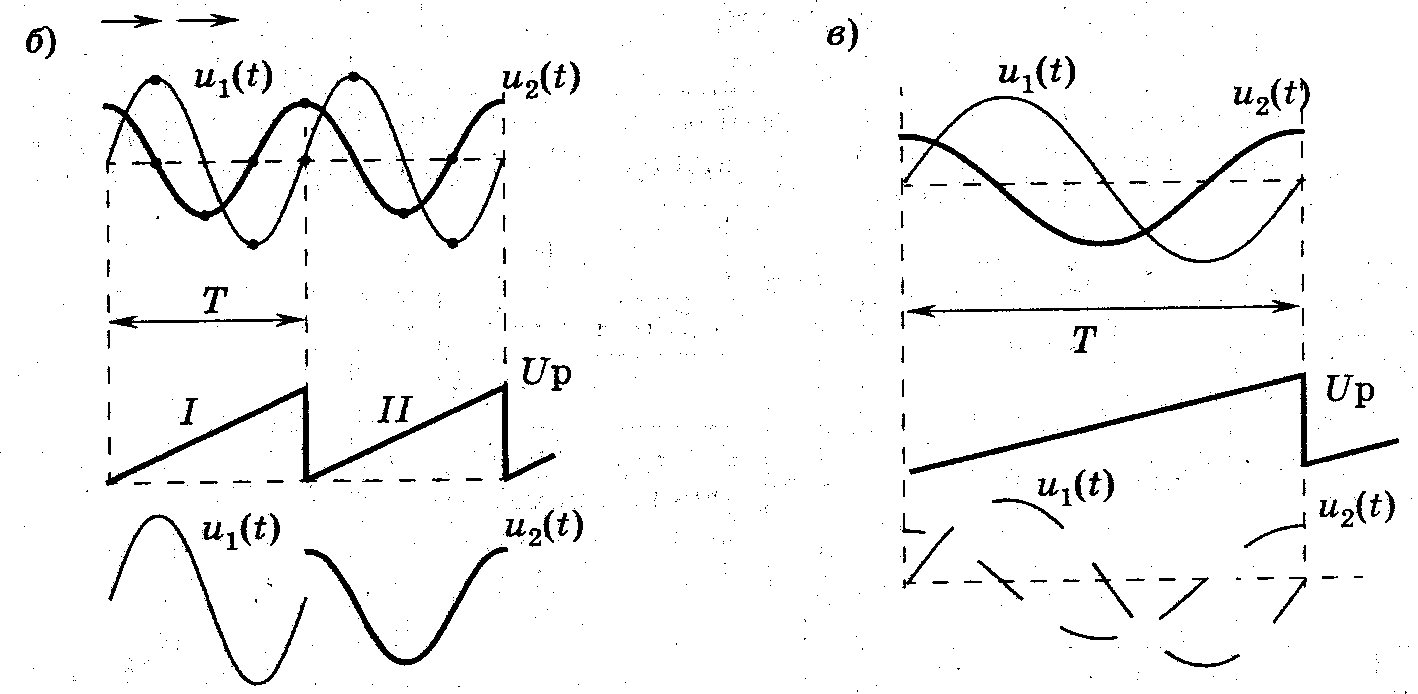

В поочередном (синхронном) режиме «→→» коммутатор работает от генератора развертки. Подключение каналов к оконечному усилителю происходит попеременно с частотой генератора развертки после каждого прямого хода развертки. Изображения сигналов каналов I и II поочередно сменяют друг друга, но так часто, что на экране они наблюдаются одновременно (рис. 2.1, б). Этот режим является основным при измерениях (на частотах выше 1 кГц). Недостаток поочередного режима проявляется при исследовании синусоидальных и импульсных сигналов с низкой частотой повторения 150 Гц, так как глазу заметны редкие поочередные мелькания изображений сигналов. Для низкого диапазона частот в осциллографе предусмотрен прерывистый (асинхронный) режим «...» работы коммутатора. В этом случае коммутатор работает с частотой 100 кГц от встроенного генератора, подключая каналы I и II к оконечному усилителю поочередно через каждые 5 мкс (за 10 мкс — оба канала). Прерывистое изображение сигналов состоит из штрихов (рис. 2.1, в). На экране осциллографа за фрагментом изображения первого сигнала следует фрагмент изображения

второго сигнала (фрагменты следуют через каждые 5 мкс). Часть информации о форме сигнала при этом теряется.

Например, при периоде 50 мкс (f = 20 кГц) будет зарегистрировано пять штрихов на каждом сигнале, а при периоде 5 мс (f = 200 Гц) сигнал будет практически непрерывным. Работу коммутатора в поочередном и прерывистом режимах иллюстрирует движение луча при медленной развертке 50 мс/дел. и отсутствии сигнала.

Генератор развертки работает в автоколебательном или ждущем режимах, переключатель режимов совмещен с регулятором «Уровень». Для исследования сигналов разных частот изменяют масштаб «Время/дел.» горизонтальной оси, что достигается изменением частоты (периода) генератора развертки. Для уменьшения минимального коэффициента развертки и растягивания отдельных фрагментов сигнала используют множитель развертки Мр. Новый коэффициент развертки равен произведению установленного коэффициента развертки и множителя развертки Мр (1 или 0,2); К'р = KРMp. Любой измеряемый временной интервал равен tx = lxKpMv.

Рисунок 2.1 Структурная схема двухканального осциллографа (а), временные диаграммы, поясняющие режимы «→→» (б) и «.....» (в)

3.Работа LPT порта

3.1 Параллельный интерфейс: LPT-порт

Порт параллельного интерфейса был введен в PC для подключения принтера —LP'T-порт (Line PrinTer — построчный принтер). Адаптер параллельного интерфейса представляет собой набор регистров, расположенных в пространстве ввода/вывода. Регистры порта адресуются относительно базового адреса порта, стандартными значениями которого являются 386h, 378h и 278h. Порт имеет внешнюю 8-битную шину данных, 5-битную шину сигналов состояния и 4-битную шину управляющих сигналов.

BIOS поддерживает до четырех LPT-портов (LPT1-LPT4) своим сервисом — прерыванием INT 17h, обеспечивающим через них связь с принтерами по интерфейсу Centronics. Этим сервисом BIOS осуществляет вывод символа, инициализацию интерфейса и принтера, а также опрос состояния принтера.

Интерфейс Centronics. Понятие Centronics относится как к набору сигналов и протоколу взаимодействия, так и к 36-контактному разъему, устанавливаемому на принтерах. Интерфейс Centronics поддерживается большинством принтеров с параллельным интерфейсом, его отечественным аналогом является интерфейс ИРПР-М.

3.2 Традиционный LPT-порт

Традиционный порт SPP (Standard Parallel Port) является однонаправленным портом, на базе которого программно реализуется протокол обмена Centronics. Порт обеспечивает возможность вырабатывания запроса аппаратного прерывания по импульсу на входе АСК#. Сигналы порта выводятся на разъем DB-25S (розетка), установленный непосредственно на плате адаптера (или системной плате) или соединяемый с ней плоским шлейфом. Название и назначение сигналов разъема порта (табл. 1) соответствуют интерфейсу Centronics. Стандартный порт имеет три 8-битных регистра, расположенных по соседним адресам в пространстве ввода/вывода, начиная с базового адреса порта (BASE).

Таблица 1

Разъем стандартного LPT-порта.

|

Контакт DB-25S |

Провод шлейфа |

Назначение |

||

|

I\O* |

Reg.Bit** |

Сигнал |

||

|

1 |

1 |

0\1 |

CR: 0\ |

Strobe# |

|

2 |

3 |

0(1) |

DR:0 |

Data 0 |

|

3 |

5 |

0(1) |

DR:1 |

Data 1 |

|

4 |

7 |

0(1) |

DR:2 |

Data 2 |

|

5 |

9 |

0(1) |

DR:3 |

Data 3 |

|

6 |

11 |

0(1) |

DR:4 |

Data 4 |

|

7 |

13 |

0(1) |

DR:5 |

Data 5 |

|

8 |

15 |

0(1) |

DR:6 |

Data 6 |

|

9 |

17 |

0(1) |

DR:7 |

Data 7 |

|

10 |

19 |

I |

SR:6 |

Ack#*** |

|

11 |

21 |

I |

SR:7\ |

Busy |

|

12 |

23 |

I |

SR:5 |

PaperEnd |

|

13 |

25 |

I |

SR:4 |

Select |

|

14 |

2 |

0\1 |

CR:1\ |

Auto LF# |

|

15 |

4 |

I |

SR:3 |

Error# |

|

16 |

6 |

0\1 |

CR:2 |

Init# |

|

17 |

8 |

0\1 |

CR:3\ |

SelectIn# |

|

18-25 |

10,12,14,16 |

18, 20, 22, 24, 26 |

- |

- |

* I/O задает направление передачи (вход/выход) сигнала порта; 0/I обозначает выходные линии, состояние которых считывается при чтении из соответствующих портов вывода.

** Символом «\» отмечены инвертированные сигналы (1 в регистре соответствует низкому уровню линии).

*** Вход Ack# соединен резистором (10 кОм) с питанием +5 В.

3.3 Функции BIOS для LPT-порта

BIOS обеспечивает поддержку LPT-порта, необходимую для организации вывода по интерфейсу Centronics. В процессе начального тестирования POST BIOS проверяет наличие параллельных портов по адресам ЗВСЬ, 378h и 278h и помещает базовые адреса обнаруженных портов в ячейки BIOS DATA AREA 0:0408h, 040Ah, 040СП, 040ЕП. Эти ячейки хранят адреса портов с логическими именами LPT1-LPT4. В ячейки 0:0478, 0479, 047А, 047В заносятся константы, задающие выдержку тайм-аута для этих портов. Поиск портов обычно ведется по базовому адресу. Если считанный байт совпал с записанным, считается, что найден LPT-порт, и его адрес помещают в ячейку BIOS DATA AREA. Адрес порта LPT4 BIOS самостоятельно установить не может, поскольку в списке стандартных адресов поиска имеются только три вышеуказанных. Обнаруженные порты инициализируются — записью в регистр управления формируется и снимается сигнал Initff, после чего записывается значение 00h, соответствующее исходному состоянию сигналов интерфейса.

Программное прерывание BIOS I NT 17h обеспечивает следующие функции поддержки LPT-порта:

00h — вывод символа из регистра AL по протоколу Centronics. Данные помещаются в выходной регистр и после готовности принтера формируется строб.

01h — инициализация интерфейса и принтера.

02h — опрос состояния принтера.

При вызове INT 17h номер функции задается в регистре АН, номер порта — в регистре DX (0 — LPT1, 1 — LPT2...). При возврате после любой функции регистр АН содержит код состояния — биты регистра состояния SR[7:3] (биты 6 и 3 инвертированы) и флаг тайм-аута в бите 0.Флаг тайм-аута устанавливается при неудачной попытке вывода символа.

3.4 Режимы передачи данных

Стандарт IEEE 1284 определяет пять режимов обмена(EPP,ECP, Nibble Mode, Fast Centronics, Parallel Port FIFO Mode) один из которых полностью соответствует традиционному стандартному программно-управляемому выводу по протоколу Centronics. Остальные режимы используются для расширения функциональных возможностей и повышения производительности интерфейса. Стандарт определяет способ согласования режима, по которому программное обеспечение может определить режим, доступный и хосту (в нашем случае это PC), и периферийному устройству.

3.5 Конфигурирование LPT-портов

Управление параллельным портом разделяется на два этапа — предварительное конфигурирование (Setup) аппаратных средств порта и текущее (оперативное) переключение режимов работы прикладным или системным ПО. Оперативное переключение возможно только в пределах режимов, разрешенных при конфигурировании. Таким образом обеспечивается возможность согласования аппаратуры и программного обеспечения и блокирования ложных переключении, вызванных некорректными действиями программы. Способ и возможности конфигурирования LPT-портов зависят от его исполнения и местоположения. Порт, расположенный на плате расширения (обычно на мультикарте), устанавливаемой в слот ISA или ISA+VLB, обычно конфигурируется джамперами на самой плате. Порт, расположенный на системной плате, обычно конфигурируется через BIOS Setup.

3.6 Использование параллельных портов

Наиболее распространенным применением LPT-порта является, естественно, подключение принтера. Практически все принтеры могут работать с портом в режиме SPP, но применение расширенных режимов дает дополнительные преимущества:

- Двунаправленный режим (Bi-Di) дает дополнительные возможности для сообщения

состояния и параметров принтера.

-Скоростные режимы (Fast Centronics) существенно повышают производительность практически любого принтера (особенно лазерного), но могут потребовать более качественного кабеля.

-Режим ЕСР потенциально самый эффективный, и он имеет системную поддержку во всех вариантах Windows. Из распространенных семейств ЕСР поддерживают принтеры HP DeskJet моделей BXX, LaserJet начиная с 4-го, современные модели фирмы Lexmark требуют применения кабеля по частотным свойствам соответствующего IEEE 1284.

3.7 Неисправности и тестирование параллельных портов

Тестирование параллельных портов целесообразно начинать с проверки их наличия в системе. Список адресов установленных портов обычно появляется в таблице заставки, выводимой BIOS на экран перед загрузкой ОС. Кроме этой таблицы, список можно посмотреть и с помощью тестовых программ или прямо в

BIOS DATA AREA с помощью любого отладчика. Если BIOS обнаруживает меньше портов, чем установлено физически, скорее всего, каким-либо двум портам присвоен один адрес. Программное тестирование порта без диагностической заглушки (Loop Back) не покажет ошибок, поскольку при этом читаются данные выходных регистров, а они у всех конфликтующих (по отдельности исправных портов) совпадут. Именно такое тестирование и производит BIOS при проверке на наличие портов.

Разбираться с такой ситуацией имеет смысл последовательно устанавливая порты и наблюдая за адресами, появляющимися в списке. Если физически установлен только один порт и его не обнаруживает BIOS, то либо он отключен при конфигурировании, либо вышел из строя скорее всего из-за нарушений правил подключения.

3.8 Параллельный порт и РпР

Большинство современных периферийных устройств, подключаемых к LPT-порту, поддерживает стандарт 1284 и функции РпР. Для поддержки этих функций компьютером с аппаратной точки зрения достаточно иметь контролер интерфейса, поддерживающий стандарт 1284. Для работы РпР подключенное устройство должно сообщить операционной системе все необходимые сведения о себе (идентификаторы производителя, модели и набор поддерживаемых команд). Более развернутая информация об устройстве может содержать идентификатор класса, подробное описание и идентификатор устройства, с которым обеспечивается совместимость.

6 Описание электрической схемы

Исследуемые сигналы через входные гнезда XW1 и XW2 поступают на резистивно-емкостные делители, состоящие из переключателей 1SA2, 2SA2, резисторов 1R1—1R8, 2R1— 2R8 и конденсаторов 1С2—1С9,2С2—2С9, которые определяют максимальный размах по вертикали (префиксы 1 и 2 здесь и далее обозначают принадлежность элементов соответственно к каналам 1 и 2). К выходам делителей через повторители на транзисторах 1VT1, 1VT2 и 2VT1, 2VT2 подключены МОП-ключи микросхемы 1DA1 (два из ее направлений использованы в канале 1, остальные — в канале 2). Ключи открываются импульсами длительностью около 10 нc, поступающими от формирователя на триггере DD1.2, и через них заряжаются конденсаторы 1С10 и 2С10, к которым подключены неинвертирующие входы ОУ 1DA2 и 2DA2. Напряжения на конденсаторах, соответствующие напряжениям сигналов в момент открывания ключей, усиливаются ОУ в 10 раз. Длительность открывающего импульса соответствует минимальной длительности фронта входного сигнала, который отобразится без искажений, т. е. определяет полосу пропускаемых частот.

К выходам ОУ подключен сдвоенный АЦП последовательного приближения. Он содержит компараторы 1DA3, 2DA3 и ЦАП, собранный на элементах микросхем DD2, DD3 и матрице R-2R, состоящей из резисторов R12—R19, R21 — R28. Выходы компараторов соединены с контактами 13 и 15 принтерного разъема ХР1. Значения сигналов на этих контактах соответствуют битам 3 и 4 порта 37.9Н. Входы ЦАП подключены к контактам 2—9 ХР1, поэтому значение выходного сигнала ЦАП может устанавливаться путем записи в порт 378Н числа от 0 до 255 (в пределах 0,5...4,5 В). Реализованное в программе измерение напряжений на выходах ОУ 1DA2 и 2DA2 путем последовательного приближения осуществляется следующим образом. Сначала в порт 378Н выставляется число 27 (на выходе ЦАП — 2,5 В) и проверяется состояние выходов компараторов (бит 3 и 4 порта 379Н). Если компаратор сработал, к указанному числу прибавляется 26, если нет — из первого вычитается второе. Затем еще раз проверяется состояние компараторов, прибавляется или вычитается 25. Процедура повторяется до прибавления или вычитания 2 . Полученные в результате числа соответствуют значениям напряжения на выходах 1DA2 и 2DA2. Делитель R20R29 устанавливает пределы изменения напряжения на выходе ЦАП от0,5 до 4,5 В. Чтобы формирователь импульсов не срабатывал при определении напряжений на выходах ОУ, на вход D триггера DD1.2 в это время подается лог. 0.

Время преобразования АЦП при времени записи в порт, равном 2 мкс, составляет 2x40 мкс. Синхронизация осуществляется в канале 1 с помощью компаратора DA1, инвертирующий вход которого через конденсаторы С1 и С2 подключен к выходу повторителя на транзисторах 1VT1 и 1VT2. Для повышения помехоустойчивости введены резисторы R2 и R3, задающие компаратору гистерезис 20 мВ. Уровень синхронизации регулируют переменным резистором R4.

Задержка времени от момента срабатывания компаратора DA1 до момента открывания ключей микросхемы 1DA1 устанавливается программно-аппаратно на высокочастотных диапазонах и программно — на низкочастотных.

В первом случае программа, когда она. готова к приему очередного значения входных сигналов, устанавливает, а затем убирает сигнал "Reset" с триггера DD1.1 (бит 7 порта 37А= "1/0", контакт 1 принтерного разъема = "0/1"). "Взведенный" таким образом триггер срабатывает при переключении компаратора DA1, и транзистор VT3 закрывается. В результате от источника тока, выполненного на элементах VT2, R8, R9, начинает заряжаться один из времязадающих конденсаторов С7—С21. Когда напряжение на нем достигает значения напряжения на выходе ЦАП, срабатывает компаратор DA2 и запускает формирователь импульса (DD1.2, R11, С22), управляющий ключами микросхемы 1DA1. Срабатывание компаратора DA2 программа определяет по значению 0 на контакте 11 принтерного разъема (бит 0 порта 37ЭН). После этого запускается подпрограмма определения напряжения на выходах 1DA2 и 2DA2. Величины напряжений записываются в память, в ЦАП устанавливается следующее значение, триггер DD1.1 снова "взводится", и цикл повторяется до момента, когда будет нажата какая-либо клавиша.

На элементах VT1, R5, R6, VD1, СЗ, С6 реализован узел определения наличия синхронизации. Когда компаратор DA1 периодически срабатывает, на контакте 10 разъема ХР1 (бит 1 порта 379Н) присутствует лог. 1, и после "взведения" триггера DD1.1 программа дожидается срабатывания компаратора DA2. В противном случае этот триггер запускается из программы путем последовательной установки сигналов "Reset" и "Set"(6nTbi 4, 7 порта 37А = "10/01", контакты 1, 17 принтерного разъема = "01/10"). На выходе ЦАП программно устанавливаются значения от 0 до 255, соответственно задержка от момента синхронизации до момента открывания ключей изменяется от минимального значения до максимального, и формируется изображение сигнала. Период развертки Т (в секундах на деление) определяется по формуле Т = CU/2I, где С — емкость подключенного конденсатора в фарадах; U = 4,5 В — максимальное напряжение ЦАП; I = 0,001 А — ток коллектора транзистора VT2. При большой емкости времязадающего конденсатора изображение сигнала формируется слишком медленно. Поэтому в программе реализована процедура определения его емкости, проверяющая, сколько раз программа может считать значения сигналов за время его зарядки. Если это время велико (задана большая длительность развертки), после переключения компаратора DA1 ключи коммутатора 1DA2 могут открываться несколько раз. При этом на выходе ЦАП устанавливаются промежуточные значения, а триггер DD1.1 запускается из программы путем последовательной установки сигналов "Reset" и "Set". Если выбрана длительность развертки больше 5 мс/дел. (переключатель SA2 в нижнем — по схеме — положении), задержка после переключения компаратора DA1 формируется программно. Программа "узнает" об этом по нулевому значению бита 2 порта 379Н.

Триггер DD1.1 запускается из программы путем последовательной установки сигналов "Reset" и "Set" через заданные промежутки времени. Время развертки задают с клавиатуры клавишами "0"— "9". Смещение луча по вертикали изменяют переменными резисторами 1R13 и 2R13, длительность развертки (плавно) — резистором R28.

Расчет параметров

При выполнении курсового проекта производится расчет статических и динамических параметров разрабатываемого изделия

7.1 Расчет потребляемой мощности

Мощность и ток, потребляемый логическим элементом (ЛЭ) от источника питания зависит от его логического состояния.

Статическая мощность потребляется ЛЭ, который не переключается. Такой элемент может находиться в состоянии логического ноля или логической единице, поэтому существует два значения статической мощности P0 и P1. Для схемы с множеством ЛЭ нулевое и единичное состояния принимают равновероятное и пользуются средним значением статической мощности:

(1)

(1)

Средняя мощность, потребляемая ЛЭ в статической режиме может быть определена по формуле:

где Iср – среднее значение тока, потребляемого ЛЭ;

Uпит – напряжение питания ЛЭ.

Схема потребляет Iп0 при Uпит =U0 и Iп1 при Uпит =U1. Тогда средний потребляемый ток одного ЛЭ определяется по формуле:

По справочным данным составляется таблица значений потребляемого тока всеми логическими элементами в состоянии лог.0 и лог.1.

Таблица 2 потребляемый ток

|

Тип ИМС |

Iп1,мА |

Iп0,мА |

Iп.ср,мА |

|

К155 ЛП5 |

45,5 |

55,5 |

50 |

|

К589АП16 |

- |

- |

45 |

|

К155 ЛН1 |

25 |

41 |

33 |

|

К155ИР13 |

18,5 |

19,5 |

19 |

Таблица 3 общий ток

Тип ИМС |

Кол-во |

Общий ток группы ИМС, мА |

Общий ток схемы, мА |

|

К155 ЛП5 |

2 |

100 |

603 |

|

К589АП16 |

1 |

45 |

|

|

К155 ЛН1 |

1 |

33 |

|

|

К155ИР13 |

1 |

19 |

Потребляемая мощность изделия рассчитывается по формуле:

Таблица 4 потребляемая мощность

|

Тип ИМС |

Мощность одного элемента, мВт |

Кол-во |

Мощность группы элементов, мВт |

Общая мощность, Вт |

|

К155 ЛП5 |

250 |

2 |

500 |

3,105 |

|

К589АП16 |

225 |

1 |

225 |

|

|

К155 ЛН1 |

165 |

1 |

165 |

|

|

К155 ИЕ7 |

510 |

2 |

1100 |

|

|

К155ИР13 |

95 |

1 |

95 |

PОБЩ =3,105 Вт

2.3.2 Расчет быстродействия

Быстродействие ЛЭ определяется временем их перехода из состояния лог.0 в состояние лог.1 и обратно (tзд01 и tзд10). Одним из важнейших

параметров является средняя задержка:

которая определяет среднее время выполнения логической операции.

При расчетах быстродействия пользуются этим параметром.

Быстродействие схемы в целом определяется средним временем задержки передачи сигнала по формуле:

где N - количество ЛЭ в максимальном пути прохождения сигнала.

По справочным данным значений времени задержек составляется таблица 4:

Таблица 5 задержка

|

Тип ИМС |

tзд10,нс |

tзд01,нс |

tзд..ср,,нс |

Быстродействие схемы, нс |

|

К155 ЛП5 |

22 |

15 |

18,5 |

20 |

|

К589АП16 |

11 |

7,5 |

9,25 |

|

|

К155 ЛЛ1 |

25 |

20 |

22,5 |

|

|

К155 ЛН1 |

10 |

5 |

7,5 |

|

|

К155ИР13 |

18 |

6 |

12 |

Tобщ=20+74=94 нС

Максимальная рабочая частота сигнала определяется по формуле:

F=10 МГц

2.3.3 Расчет надежности

Надежность – свойство объекта сохранять во времени в установленных пределах значение всех параметров, характеризующих способность выполнять требуемые функции в заданных режимах и условиях эксплуатации, применения, хранения, ремонта, транспортировки.

Расчет параметров надежности ведется в два этапа:

предварительный расчет надежности;

2)окончательный расчет надежности.

Предварительный расчет надежности производят на этапе эскизного проектирования. В результате предварительного расчета определяются

следующие показатели надежности:

интенсивность отказов изделия:

где N – число групп “компонентов надежности”, имеющих разные интенсивности отказов;

-

интенсивность отказа элемента i-ой

группы;

-

интенсивность отказа элемента i-ой

группы;

ni - число элементов этой группы

время наработки на отказ:

вероятность безотказной работы:

P(t) рассчитывается для t=100, 1000, 10000 часов.

Результаты предварительного расчета показателей надежности вносится в таблицу:

Таблица 6 предварительный расчёт надёжности

|

Группы элементов |

Количество элементов |

Интенсивность

отказов

|

1/ч*10-6 |

|

|

ИМС |

11 |

0,02 |

0,22 |

7,732865 |

|

Конденсаторы керамические |

31 |

0,15 |

0,6 |

|

|

Конденсаторы электролитические |

1 |

0,035 |

0,105 |

|

|

Основание платы |

2 |

0,1 |

0,1 |

|

|

Пайка |

259 |

0,005 |

1 |

|

|

Разъем (штырек) |

25 |

0,062 |

2,294 |

Т=2,30*105 ч;

P (100) =0,99956;

P (1000) =0, 99567;

P (10000 ) =0,95753.

Окончательный расчет надежности ведется на этапе технического проектирования. При расчете интенсивности отказов учитывается электрический режим работы электрорадиоэлементов (ЭРЭ) и условия эксплуатации (температура, влажность, вибрация и т.д.).

В рамках курсового проекта для учета влияния режима работы рассчитывается коэффициент нагрузки Kn, а температурный коэффициент берется равным единицы:

где Нраб – нагрузка на элемент в рабочем режиме;

Нном – нагрузка в номинальном (допустимом) режиме.

Коэффициент Кн для ИМС определяется нагрузочной способностью (через коэффициент разветвления):

для конденсаторов через напряжение:

для резисторов через мощность:

Номинальный коэффициент разветвления для микросхем серии 155 равен десяти.

Результаты расчетов заносится в таблицу:

Таблица 7 Окончательный расчет надежности

|

Элементы |

Интенсивность

отказов

|

Коэффициент нагрузки Kн |

|

|

|

DD1 |

0,02 |

0,2 |

0,004 |

3,57888 |

|

DD2 |

0,02 |

0,175 |

0,0035 |

|

|

DD3 |

0,02 |

0,106 |

0,00212 |

|

|

DD4 |

0,02 |

0,187 |

0,00374 |

|

|

DD5 |

0,02 |

0,106 |

0,00212 |

|

|

DD6 |

0,02 |

0,23 |

0,0046 |

|

|

DD7 |

0,02 |

0,04 |

0,0008 |

|

|

DD8 |

0,02 |

0,075 |

0,0015 |

|

|

DD9 |

0,02 |

0,06 |

0,0012 |

|

|

DD10 |

0,02 |

0,08 |

0,0016 |

|

|

DD11 |

0,02 |

0,1 |

0,002 |

|

|

DD12 |

0,02 |

0,01 |

0,0002 |

|

|

C1 |

0,15 |

0,1 |

0,015 |

|

|

C2 |

0,035 |

0,5 |

0,0175 |

|

|

C3 |

0,035 |

0,5 |

0,0175 |

|

|

C4 |

0,035 |

0,5 |

0,0175 |

|

|

C5 |

0,15 |

0,2 |

0,03 |

|

|

C6 |

0,15 |

0,2 |

0,03 |

|

|

C7 |

0,15 |

0,2 |

0,03 |

|

|

Пайка(200шт) |

1 |

1 |

1 |

|

|

Разъем(37шт) |

2,294 |

1 |

2,294 |

|

|

Основание платы |

0,1 |

1 |

0,1 |

Т=2,79*105 ч;

P(100)=0,99964;

P(1000)=0,99642;

P(10000)=0,96484.

,

, ,

1/ч*10-6

,

1/ч*10-6 1/x*10-6

1/x*10-6 Kн,

1/ч*10-6

Kн,

1/ч*10-6 1/ч*10-6

1/ч*10-6