Проектирование устройств фильтрации (работа 1)

Министерство образования Республики Беларусь

Учреждение образования «Белорусский государственный университет

информатики и радиоэлектроники

Факультет телекоммуникаций

Кафедра систем телекоммуникаций

Дисциплина: Прикладное программирование

Пояснительная записка

к курсовой работе

на тему

Проектирование устройств фильтрации

БГУИР КР 1-45 01 01 ххх ПЗ

Студент: гр. 860801 Хочченкко О.В.

Руководитель: старший

преподаватель Беленкевич Н.И.

Минск 2010

СОДЕРЖАНИЕ

ВВЕДЕНИЕ

1 ОБЗОР ПРОГРАММНОГО ОБЕСПЕЧЕНИЯ ДЛЯ РАЗРАБОТКИ ПЛИС

1.1 САПР ORCAD

1.2 САПР FOUNDATION

1.3 САПР SyNPLICITy

2 МЕТОДЫ ПРОЕКТИРОВАНИЯ УСТРОЙСТВ ФИЛЬТРАЦИИ ПО РАБОЧИМ ПАРАМЕТРАМ

3 ВИДЫ АППРОКСИМАЦИИ ЧАСТОТНЫХ ХАРАКТЕРИСТИК: АППРОКСИМАЦИЯ ЧЕБЫШЕВА (ПРЯМАЯ И ИНВЕРСНАЯ)

3.1 АППРОКСИМАЦИЯ ПО ЧЕБЫШЕВУ ПРЯМАЯ (ПЕРВОГО РОДА)

3.2 АППРОКСИМАЦИЯ ЧЕБЫШЕВА ИНВЕРСНАЯ (ВТОРОГО РОДА)...19

4 ВЫВОД ПЕРЕДАТОЧНОЙ ФУНКЦИИ ФИЛЬТРА ПО СТРУКТУРЕ РАУХА

5 МОДЕЛИРОВАНИЕ ФИЛЬТРА НА ФУНКЦИОНАЛЬНОМ УРОВНЕ В СИСТЕМЕ MATHCAD В ЧАСТОТНОЙ И ВРЕМЕННОЙ ОБЛАСТЯХ (РАСЧЕТ АЧХ, ФЧХ, ХРЗ, ХГВЗ, ИХ, ПХ В НОРМИРОВАННОМ И ДЕНОРМИРОВАННОМ ВИДАХ

6 РАЗРАБОТКА ПРИНЦИПИАЛЬНОЙ СХЕМЫ ФИЛЬТРА, РАСЧЕТ ЭЛЕМЕНТОВ

7 МОДЕЛИРОВАНИЕ ФИЛЬТРА НА СХЕМАТЕХНИЧЕСКОМ УРОВНЕ В СИСТЕМЕ ELECTRONIC WORKBENCH В ЧАСТОТНОЙ И ВРЕМЕННОЙ ОБЛАСТЯХ (ИЗМЕРЕНИЕ АЧХ, ФЧХ, ЧРЗ, ИХ, ПХ)

8 ИЗМЕРЕНИЕ АЧХ ФИЛЬТРА В СИСТЕМЕ ELECTRONIC WORKBENCH С ПОМОЩЬЮ ЛЧМ СИГНАЛА

ЗАКЛЮЧЕНИЕ

СПИСОК ИСПОЛЬЗОВАННЫХ ИСТОЧНИКОВ

ВВЕДЕНИЕ

Цепи фильтрации сигналов – важная и неотъемлемая часть многих систем связи и электрических контрольно-измерительных устройств. Они служат для формирования частотных каналов в системах коммутации, разделения и преобразования электрических сигналов. С помощью машинных программ можно рассчитывать схему любых фильтров, отвечающих заданным техническим требованиям, используя хорошо разработанные методы синтеза.

Электрический фильтр – устройство, пропускающее электрические колебания одних частот и задерживающее колебания других часто. В более узком смысле фильтры – это основные электронные компоненты многих систем связи, таких, как телефония, телевидение, радиовещание, радио- и звуколокация. Фактически электрические фильтры так распространены в современной технике, что невозможно представить любой электронный прибор средней сложности, в котором бы не использовался фильтр в том или ином виде.

Данная курсовая работа будет направлена на проектирование устройства фильтрации, освоение методики расчета его элементов, построение характеристик. Анализ характеристик во временной и частотной областях позволит сделать некоторые выводы о правильности расчёта фильтра на определённых этапах.

В данной курсовой работе будут использованы два вспомогательных программных продукта – это MathCAD как программа построения различных характеристик и численного расчёта выражений, а также Electronic Workbench как оболочка построения принципиальной схемы фильтра и получения тех же характеристик.

ОБЗОР ПРОГРАММНОГО ОБЕСПЕЧЕНИЯ ДЛЯ РАЗРАБОТКИ ПЛИС

Программируемые логические интегральные схемы (ПЛИС) являются ИС высокого уровня интеграции для разработки на их базе специализированных устройств. ПЛИС соединяют достоинства массового заводского производства ИС с возможностью гибкого подбора структуры ИС для малосерийных специализированных устройств. На базе ПЛИС могут быть изготовлены логические блоки и системы, преобразователи кодов, периферийные контроллеры, микропрограммные устройства управления, конечные автоматы, умножители, небольшие процессоры, в том числе для быстрого преобразования Фурье. Проектирование устройства на ПЛИС заключается в составлении схемы соединений входящих в ее состав логических элементов и последующем программировании матрицы специальным программатором, которое может быть выполнено самим пользователем. Основное преимущество ПЛИС перед другими специализированными схемами — малое время изготовления требуемых заказных вариантов схем. Исчезает необходимость обращаться к изготовителям ИМС для нанесения металлической маски и установки кристалла в корпус. Время получения нужной ИС из стандартной ПЛИС измеряется секундами и минутами. Широкое распространение ПЛИС стало возможным благодаря наличию множества автоматизированных систем проектирования (САПР). Разными производителями для решения собственных задач было разработано множество САПР. На сегодня наибольшее распространение получили несколько мощных САПР для ПЛИС, к которым следует отнести OrCAD, Protel, MAX+PLUS II, Foundation, Active-CAD, Synplicity.[1]

1.1САПР ORCAD

Система OrCAD является системой моделирования и сквозного проектирования аналого-цифровых электронных устройств. Продукты серии OrCAD принадлежат компании Cadence Design Systems. Название OrCAD произведено от слов Oregon и CAD. Последняя версия OrCAD 16.2 обладает возможностями по созданию и поддержке баз данных доступных интегральных схем и работает в ОС Windows 9x, Windows NT 4.0, Windows 2000, Windows XP, Windows 2003, Windows Vista. Базы данных могут быть обновлены путем скачивания пакетов производителей компонентов, таких как Texas Instruments. В России пока наиболее хождение имеет версия 9.2, вышедшая в октябре 2000 года . В составе пакета следующие модули:

Capture — редактор принципиальных схем;

Capture CIS Option — менеджер библиотек Active Parts;

PSpice Analog Didital — пакет аналого-цифрового моделирования;

PSpice Аdvanced Аnalysis — пакет параметрической оптимизации;

PSpice SLPS option — интерфейс связи с пакетом Matlab;

PCB Designer — редактор топологий печатных плат;

SPECCTRA for OrCAD — программа автоматической и интерактивной трассировки;

Signal Explorer — модуль анализа целостности сигналов и перекрестных искажений.

Линейка программ OrCAD реализует все этапы проектирования ПП:

схемный ввод;

размещение компонентов;

трассировка;

вывод изделия в производство.

Следует отметить, что в состав OrCAD 9.2 не входит модуль моделирования цифровых устройств и синтеза ПЛИС OrCAD Express. Для этих целей фирма Cadence предлагает специализированный пакет программ FPGA Studia.

Опция для моделирования поведения печатной платы позволяет выполнять тестирование изделия без выпуска физического прототипа. Выпуск документации автоматизирован, при внесении изменений в любую часть проекта, они автоматизировано отражаются в документации. Технология проектирования Cadence обеспечивает целостность и синхронизацию этапов проекта от схемного ввода до запуска в производство, а также средства ведения корпоративной базы данных компонентов CIS.[1]

1.2 САПР FOUNDATION

Для работы с устройствами FPGA, в том числе и с семейством Virtex, фирмой Xilinx в кооперации с Aldec и Synopsys разработан мощный и современный пакет Foundation, последняя версия которого (ISE 4.1) обеспечивает ряд новых функций, позволяющих использовать ПЛИС в качестве основной элементной базы для построения “систем на кристалле” (system-on-chip, SOC). Компоненты SOC разрабатываются отдельно и хранятся в виде файлов параметризируемых модулей. Окончательная структура SOC-микросхемы выполняется на базе этих “виртуальных компонентов”, называемых также “блоками интеллектуальной собственности”, с помощью САПР. Благодаря стандартизации, в одно целое можно объединять “виртуальные компоненты” от разных разработчиков. Для поддержки работы над кристаллами, емкость которых составляет 2 000 000 эквивалентных вентилей, необходимо обеспечить возможность коллективной работы над проектом. Foundation обеспечивает поддержку коллектива разработчиков как в локальной сети, так и с использованием ресурсов Internet. Данная технология разработки получила наименование Internet Team Design (Itd).

Основу системы составляет оболочка Foundation Project Manager, разработанная фирмой Aldec. Использование Project Manager позволяет обеспечить удобное задание всех параметров проекта, а также быстрое управление вводом описания проекта, его компиляции, временного и функционального моделирования, верификации и программирование ПЛИС (рис. 6). Пакет Foundation выпускается в различных по конфигурации модификациях, в максимальном варианте доступны следующие модули:

FPGA Express Synthesis — осуществляет синтез проекта с использованием языков описания аппарат уры высокого уровня (VHDL и Verilog synthesis). Данный модуль разработан компанией Synopsys. Данный компилятор поддерживает синтез устройств с заданными временными пара-

метрами.

Schematic Editor — схематический редактор, имеющий развитые библиотеки. В версии 2.1 применяется редактор схем Vista, входящий составной частью в FPGA Express. Модуль ввода проекта на языке описания аппаратуры.

ABEL — обеспечивается поддержка ввода описания алгоритма и синтез с использованием данного языка, который предназначен для описания проектов, выполняемых на ПЛИС Xilinx и некоторых других производителей.

State Editor — обеспечивается ввод описания цифрового автомата с помощью его графа переходов. Данный способ описания проекта позволяет весьма просто и наглядно задать поведение автомата и весьма удобен при разработке различных устройств управления. В дальнейшем возможно сделать для созданного автомата символ и использовать его в редакторе схем.

HDL Editor — специализированный редактор, имеющий удобные средства контроля синтаксиса, шаблоны типовых конструкций и удобную связь с компиляторами. В качестве средства работы с проектом на базе HDL используется Language Assistant, состоящий из трех основных модулей Language Templates, Synthesis Templates и User Templates.

LogiBLOX — средство для создания описания модулей в интерактивном графическом режиме. Оно позволяет создавать такие узлы, как счетчики, сдвиговые регистры, элементы памяти и мультиплексоры. LogiBLOX запускается непосредственно из редактора HDL Editor с использованием команды Synthesis / LogiBLOX. С использованием этого средства достаточно просто создать описание узла на языке описания аппаратуры, не владея им в совершенстве.

Express Constraints Editor — средство для задания параметров компиляции проекта. С помощью этого редактора удобно задавать временные ограничения для проекта.

Logic Simulator — симулятор, позволяющий удобно провести его функциональное (логическое, поведенческое) моделирование после ввода описания проекта. В симуляторе в интерактивном графическом режиме задаются сигналы, которые используются для проведения моделирования. Результаты моделирования можно наблюдать как в привычном виде временных диаграмм, в том числе в режиме Probe, так и с использованием семисегментных индикаторов.

Design Implementat ion — модуль, запускающийся из Project Manager, позволяющий выбрать устройство, на котором реализуется проект, подгрузить файл ограничений и параметров синтеза, созданный пользователем, а затем запустить компиляцию проекта.

Timing Simulation — модуль, позволяющий провести временное моделирование в случае успешной компиляции проекта.

Xchecker — загрузчик, позволяющий проводить аппаратную верификацию проекта после проведения моделирования на компьютере. Программное обеспечение фирмы Xilinx поддерживает генератор логических ядер (CORE Generator). Сгенерированные ядра (LogiCORE) представляют собой функциональные параметризированные блоки системного уровня, предназначенные для применения в цифровой обработке сигналов. Кроме того, фирма Xilinx поддерживает программу разработки готовых решений для САПР ПЛИС AllianceCORE.[1]

1.3 САПР SyNPLICITy

Разработчики ПЛИС по всему миру используют программные средства компании Synplicity. Образованная в 1994 году, Synplicity сразу выпустила ряд успешных продуктов, ориентированных на решение задачи логического синтеза для ПЛИС. Учитывая, что электронные устройства на базе современных ПЛИС — один из наиболее активно развивающихся секторов микроэлектроники, можно утверждать, что Synplicity сегодня входит в число самых заметных игроков на рынке средств автоматизированного проектирования микроэлектронных компонентов. Компания Synplicity интенсивно развивается, осваивает новые направления системного и физического синтеза. Особенно трудная задача при разработке систем синтеза — обеспечить возможность эффективной реализации исходного RTL-описания во всех доступных элементных базисах. В полной мере решить эту задачу, как впрочем и для компиляторов, тяжело, но Synplicity, пожалуй, продвинулась в ее решении дальше всех. Одно из интереснейших направлений развития компании — разработка аппаратного отладчика RTL-кода на базе ПЛИС. Сегодня отладка и функциональная верификация RTL-кода, кстати в отличие от разработки программ, производится в искусственной среде средств логического моделирования. Понятно, что при реализации в виде ASIC отладку на аппаратном уровне не сделаешь, а вот решения для перепрограммируемых FPGA весьма интересны.

Сегодня компания Synplicity предоставляет средства для решения практически всех задач синтеза как для ПЛИС, так и для ASIC и структурных ASIC. Линейка продуктов компании включает следующие пакеты:

Synplify DSP — автоматический синтез RTL-кода для систем цифровой обработки сигналов (Digital Signal Processing, DSP).

Synplify Pro, Synplify ASIC — логический синтез для FPGA и заказных СБИС соответственно.

Amplify FPGA, Amplify ASIC — физический синтез для FPGA и заказных СБИС соответственно. (Существуют также специальные версии Ampl ify ASIC для таких структурных ASIC, как RapidChip фирмы LSI Logic, ISSP фирмы NEC, AccelArray фирмы Fujitsu.)

Certify — прототипирование ASIC-проектов на FPGA.

dentify — отладчик RTL-кода.

Fortify — проектирование системы питания для ASIC с учетом влияния таких факторов, как электромиграция, падение напряжения в шинах питания и др.

Поскольку компания Synpl icity стартовала как разработчик средств логического синтеза, в этой области накоплен наибольший опыт. Именно Synplicity сделала логический синтез простым и доступным инструментом, который стандартно используется всеми разработчиками, а основатель и идеолог компании Кен Макэлван (Ken McElvan) входит в небольшой список людей, оказавших наиболее значительное влияние на развитие всей полупроводниковой промышленности. Продукты компании базируются на собственной B.E.S.T. (Behavior Extracting Synthesis Technology) — технологии логического синтеза. Реализованная в системе Synplify, эта технология получила дальнейшее развитие в системе Synplify Pro.

Synplify Pro ориентирована на работу с современными ПЛИС емкостью в несколько миллионов вен-тилей, работающих с частотами свыше 100 МГц. Благодаря алгоритмам, заложенным в систему, можно выделять крупные функциональные блоки (конечные автоматы, память, арифметические блоки) и проводить высокоуровневую оптимизацию. Использование метода ретайминга (retiming), при котором оптимизируется расположение регистров внутри комбинационной логики, позволяет добиваться 25-процентного увеличения производительности. Инкрементный синтез, базирующийся на собственной технологии компании Multipoint и использующий установленные пользователем в компиляторе RTL-кода точки, обеспечивает возможность за счет оптимизации интерфейсов скомпилированных блоков добиться высокого уровня стабильности проекта и избежать ухудшения производительности, что свойственно другим инкрементным методам. Для самых сложных проектов полезны будут такие возможности Synplify Pro, как управление вариантами реализации, интеграция IP и повторное использование ранее разработанных блоков (design re-use). Система логического синтеза для ASIC (Synplify ASIC), появившаяся несколько позже, была разработана на основе идеологии и алгоритмов, заложенных в Synplify Pro., таких как технология синтеза B.E.S.T., которая позволяет при компиляции извлекать поведенческую информацию из RTL-кода и проводить высокоуровневую оптимизацию всего проекта. А уникальная технология прямого отображения проекта в элементный базис производителя (Direct Mapping Technology, D.M.T.) дает возможность миновать свойственные другим системам синтеза этапы преобразования проекта в базис внутренней библиотеки и последующей оптимизации в базисе произ-водителя. Система сразу “видит” и использует все доступные элемен-ты, а не элементарные логические функции. Благодаря этому в Synplify ASIC высокая производительность синтеза сочетается с глубокой оптимизацией проекта (в среднем, при пятикратном уменьшении времени синтеза, результирующая схема получается на 15% компактнее, чем в традиционных системах логического синтеза заказных СБИС). Получение более компактной схемы облегчает задачу размещения/трассировки на последующих этапах и повышает качество всего проекта в целом. В системе Synplify ASIC обеспечена возможность поддержки единой иерархии проекта и системы проектных ограничений на этапах синтеза и размещения/трассировки. Методология проектирования сверху вниз позволяет проводить синтез с учетом временных ограничений при размерах отдельных блоков до двух миллионов вентилей. [1]

Как Synplify ASIC, так и Synplify Pro включают в себя систему отлад-ки HDL Analyst, которая обеспечивает удобные средства анализа и отладки проекта. Здесь поддержи-вается возможность кросс-ссылок между исходным RTL-текстом, его схемным графическим представлением, синтезированной схемой в библиотечном базисе и диагностическими листингами. В среде HDL Analyst также выполняется анализ критических путей и различные виды фильтрации схемных диаграмм, так что разработчик может полностью контролировать проект во всех его представлениях. [1]

Надо заметить, что сложность проектов на FPGA возрастает вслед за ASIC, и те проблемы, с которыми уже столкнулись разработчики ASIC, становятся актуальными и для разработчиков FPGA. Имея полную линейку продуктов синтеза для различных технологий, компания Synplicity видит весь спектр проблем проектирования в этой области. Поэтому многие технологии проектирования, изначально разработанные и апробированные в Synplify ASIC, сейчас реализуются в SynplifyPro.

С ростом степени интеграции и переходом на технологические нор-мы проектирования ниже 0,18 мкм усиливается влияние топологии на временные параметры логических схем. Задержки в линиях связей начинают преобладать над задержками логических элементов. В этих условиях приобретает актуальность создание систем физического синтеза, где одновременно с логическим синтезом производится размещение элементов и оптимизация синтезированной схемы по его результатам. Возникновение систем физического синтеза было инициировано прежде всего требованиями разработчиков ASIC. Но сегодня потребность в таких системах возрастает и для разработчиков FPGA.

Система Amplify ASIC в единой оболочке поддерживает весь процесс логического и физического синтеза, включая планировку кристалла, размещение, предварительную рассировку, оценку загруженности и временной анализ. Средства планировки дают возможность автоматически сгенерировать весь план кристалла непосредственно из RTL-кода либо завершить предварительно сделанную частичную планировку. Быстрые средства автоматического размещения позволяют проводить синтез и одновременное размещение компоненов, а предварительная глобальная трассировка и временной анализ обеспечивают достоверное прогнозирование результатов проектирования. Предусмотрены также средства учета при размещении требований к трассировке тактовых сигналов. [1]

Следует заметить, что Ampl ify ASIC — один из первых продуктов на зарождающемся перспективном рынке средств физического синтеза для структурных ASIC. Сегодня уже поддерживается синтез для кристаллов ISSP фирмы NEC, RapidChip фирмы LSI Logic и Luminance компании Lightspeed Semiconductor. В ближайшее время будет обеспечена поддержка серии AccelArray фирмы Fujitsu и ряда других производителей структурных ASIC. Базовый продукт Amplify ASIC — универсальный, он обеспечивает проектирование любых ASIC, включая и структурные. В то же время аналогично версиям Synplify и Synplify Pro для различных производителей FPGA, разработаны специальные версии Amplify для каждого производителя структурных ASIC, в полной мере учитывающие возможности конкретных типов кристаллов. [1]

Компания Synplicity — пионер в области физического синтеза для ПЛИС. Ее система Amplify FPGA на протяжении нескольких лет используется крупными электронными компаниями по всему миру, являясь фактически стандартом в этой области. Для современных ПЛИС недостаточно средств логического синтеза, в котором анализируются только статистические модели меж-соединений и задержки переключения вентилей, поскольку реальные задержки во многом определяются топологией и могут сильно отличаться от предварительных оценок. В отсутствие средств, учитывающих топологическую реализацию, процесс проектирования современных ПЛИС имеет шанс стать непредсказуемым, поскольку исправление ситуации в одном месте может повлечь за собой возникновение проблем в других частях схемы. Использование системы Ampl ify FPGA позволяет достичь в автоматическом режиме работы результатов, сопоставимых с полностью ручными режимами размещения и трассировки, и в среднем увеличить производительность разрабатываемых устройств на 20%, а в некоторых случаях — до 45% по сравнению с результатами, полученными при использовании обычного логического синтеза. Улучшение достигается за счет одновременной оптимизации размещения и синтезируемой логики. Используются методы оптимизации, учитывающие меж-соединения логических элементов, проводится автоматическая репликация (repl ication) логики и оптимизация критических путей. Сегодня появилось уже третье поколение системы Amplify FPGA, в котором реализованы новейшие методы физического синтеза для самых современных архитектур ПЛИС, таких как Virtex-4 компании Xilinx и Stratix II компании Altera. Для FPGA фирмы Xilinx в Amplify FPGA реализованы все этапы автоматического синтеза вплоть до размещения. Причем с гарантией соблюдения временных параметров. Остается только выполнить трассировку. Надо отметить, что сами разработчики ПЛИС — компании Xi l inx и Altera — при разработке своих библиотек IP-блоков применяют системы Amplify и Synplify Pro.

Система Identify позволяет на практике реализовать концепцию верификации проекта на основе отладки. Суть этой концепции в том, что с помощью систем моделирования проверяются только основные режимы работы модулей проекта, затем, после интеграции модулей в единый проект, макет на базе FPGA с воз-можностью диагностики ключевых внутренних сигналов в контрольных точках помещается в реальную рабочую среду, после чего фактически сама среда автоматически тестирует проект. Аппаратный отладчик, которому доступны данные контрольных точек, помогает выявлять имеющиеся проблемы и разбираться с причинами их возникновения. Как уже было замечено, процесс разработки цифровых электронных систем все больше напоминает разработку программного обеспечения. Но в программировании редко кто смотрит на скомпилированный код. При разработке аппаратуры разработчик работает со спецификациями VHDL или Verilog на уровне RTL, поэтому отладка, соответственно, должна проводиться на RTL-уровне, а не на уровне синтезированного списка цепей. Процесс аппаратной отладки выглядит аналогично отладке в системах моделирования, но с реальными сигналами и на скорости работы реальной аппаратуры. Объединение моделирования и аппаратной отладки обеспечивает более надежную проверку проекта при значительно меньших затратах на создание тестов и верификацию проекта средствами моделирования. Причем, при использовании современных средств прототипирования, таких как система Certify, предложенный подход доступен как разработчикам FPGA, так и разработчикам ASIC.

Отладчик Identify на сегодняшний день единственная система, дающая возможность разработчикам FPGA и прототипов ASIC выполнять функциональную отладку проектов напрямую в исходном коде RTL с использованием сигналов реального мира для аппаратно-программных, мультимедийных и сетевых приложений. По сравнению с системами моделирования скорость функциональной верификации повышается на пять порядков. Identify позволяет разработчикам напрямую выбирать в исходном RTL-коде сигналы и задавать условия для контроля и просмотра временных диаграмм с сохранением результатов в стандартном формате VCD (Value Change Dump), воспринимаемом всеми системами работы с временными диаграммами. [1]

2.МЕТОД ПРОЕКТИРОВАНИЯ УСТРОЙСТВ ФИЛЬТРАЦИИ ПО РАБОЧИМ ПАРАМЕТРАМ

Методика проектирования фильтров по рабочим параметрам основана на нахождении значений элементов, нармированных по частоте и сопротивлению нагрузки, путём аппроксимации или с помощью справочной литературы.

Если взять нормирующую частоту fn (Гц) и нормирующее сопротивление Rn (Ом), то получим следующие нормирующие величины(коэффициенты нормировки):

Ln=Rn/(2Пfn) – нормирующая индуктивность(Гн); (2.1)

Сn=1/(2ПfnRn) – нормирующая ёмкость(Ф); (2.2)

Физические величины(размерые) можно нормировать относительно выбранных нормирующих величин, среди которых нормированные(безразмерные) значения частоты, индуктивности, ёмкости определяются соответственно формулами:

W=f/fn; (2.3)

L=L/Ln; (2.4)

C=C/Cn; (2.5)

Обратный переход от нормированных к денормированным(размерным) значениям физических параметров схемы фильтра осуществляется путём соответствующего выбора конкретных значений fn и Rn. [2]

При решении задач по расчёту ФНЧ обычно заданы такие параметры:

fc – граничная частота полосы пропускания

fs – граничная частота полосы задерживания, на которой затухание должно быт не менее минимального затухания в полосе задерживания Аs;

R – сопротивление нагрузки.

В качестве нормирующей частоты fn выбирается частота среза fc, нормирующего сопротивления Rn – сопротивление нагрузки R. Для оценки требуемого порядка n ФНЧ используются соответствующие диаграммы и таблицы при нормированной частоте Ws, найденной из выражения(2.3):

Ws=fs/fc . (2.6)

В основе метода расчёта ФВЧ по рабочим параметрам лежит переход от ФВЧ к ФНЧ. Характеристики ФВЧ получают из характеристик фильтра прототипа нижних частот при использовании частотного преобразования:

Wфвч=1/Wфнч (2.7)

Как и в случае расчёта ФВЧ, параметры ПФ находятся с помощью частотных преобразований элементов на основе табличных данных для ФНЧ(как фильтров-прототипов).[2]

Согласно частотному преобразованию:

Wфнч=k(W~пф-1/W~пф) (2.8)

Положительным вещественным частотам W фильтра-прототипа НЧ соответствуют положительные значения W~ симметричного ПФ, тогда

W~=√((W/2k)² +1) ±W/2k (2.9)

В качестве нормирующей частоты для полосового фильтра используют среднюю геометрическую двух частот среза фильтра:

fn=f0=√fc1fc2, (2.10)

Коэффициент преобразования ширины полосы k вычисляется по формуле:

k= f0/(fc1-fc2)=f0/∆f (2.11)

Порядок n и тип фильтра-прототипа НЧ определяют, исходя из заданного затухания Аs на нормированной частоте Ws, которую вычисляют по формуле,полученной в результате подстановки выражений (2.10) и (2.11) при f=fs в уравнение (2.8):

Ws=│f²s-f²0│/fs∆f [2]

3. ВИДЫ АППРОКСИМАЦИИ ЧАСТОТНЫХ ХАРАКТЕРИСТИК: АППРОКСИМАЦИЯ ЧЕБЫШЕВА (ПРЯМАЯ И ИНВЕРСНАЯ)

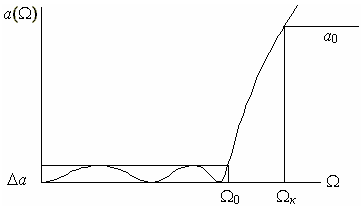

Задача аппроксимации состоит в том, чтобы синтезировать некоторую функцию частоты, удовлетворяющую требованиям к АЧХ или ХРЗ разрабатываемого фильтра. Наиболее удобно функцию частоты представить в виде ХРЗ

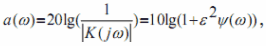

(3.1)

(3.1)

где ε^2 – коэффициент, характеризующий степень постоянства (неравномерность) затухания (усиления) в полосе пропускания; ψ(ω) – функция фильтрации, для которой желательны значения, близкие к нулю в полосе пропускания и как можно большие в полосе задерживания. Функция фильтрации в общем случае может быть дробной.[3]

В качестве функции фильтрации часто используют полиномы Чебышева. Полиномы Чебышева обеспечивают равноволновое приближение в полосе пропускания.Полиномы Чебышева первого рода в общем виде задаются соотношением

Tn(x)= cos (n arccos(x)) [3] (3.2)

Функция Tn(x) на отрезке [- 1 ; 1] изменяется в пределах от -1 до +1, переходя n раз через нуль и принимая 1 + n раз крайние значения (поочередно 1 или -1 ). При x>1 все полиномы T 1 + n(x) положительны, при x<-1 полиномы четных степеней положительны, нечетных — отрицательны. За пределами отрезка [ -1 ; 1] функция Tn(x) монотонно возрастает. Доказано, что из всех полиномов одинаковой степени, значение модуля которых на отрезке [-1 ; 1] не превышае тединицы, полином Чебышева за пределами этого отрезка принимает наибольшие по абсолютной величине значения. Данное свойство полиномов Чебышева обусловило их широкое применение при аппроксимации ХРЗ фильтров.[4]

3.1 АППРОКСИМАЦИЯ ПО ЧЕБЫШЕВУ ПРЯМАЯ (ПЕРВОГО РОДА)

Фильтр Чебышева — один из типов линейных аналоговых или цифровых фильтров, отличительной особенностью которого является более крутой спад амплитудно-частотной характеристики (АЧХ) и существенные пульсации амплитудно-частотной характеристики на частотах полос пропускания (фильтр Чебышева I рода)

Фильтры Чебышева обычно используются там, где требуется с помощью фильтра небольшого порядка обеспечить требуемые характеристики АЧХ, в частности, хорошее подавление частот из полосы подавления, и при этом гладкость АЧХ на частотах полос пропускания и подавления не столь важна.

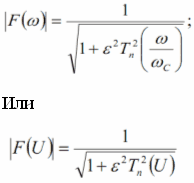

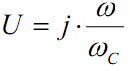

Амплитудно-частотная характеристика фильтра чебышева 1-го порядка задаётся следующим образом:

Здесь

ωС — частота среза (для фильтра-прототипа

она равна 1 рад/с), Тn(U) — полином Чебышева

n-го порядка, n — порядок фильтра, ε —

параметр, определяющий величину пульсаций

АЧХ в полосе пропускания, ωС — частота

среза,

нормированная

комплексная частота.

нормированная

комплексная частота.

Полином Чебышева Тn(х) при х<1 колеблется в диапазоне -1... +1,

а при

х >1 неограниченно возрастает по

абсолютной величине. Поэтому АЧХ фильтра

Чебышева первого рода в полосе пропускания

(при |ω|<ωС) колеблется между значениями

и 1, а вне полосы пропускания (при |ω|>ωС)

монотонно затухает до нуля (см.рисунок

3.1.1)

и 1, а вне полосы пропускания (при |ω|>ωС)

монотонно затухает до нуля (см.рисунок

3.1.1)

Коэффициент

передачи на нулевой частоте равен 1 при

нечетном порядке фильтра,

—

при четном. На частоте среза коэффициент

передачи фильтра равен

—

при четном. На частоте среза коэффициент

передачи фильтра равен

,

то есть уровню пульсаций АЧХ в полосе

пропускания. При ω→∞ АЧХ стремится к

нулю.[5]

,

то есть уровню пульсаций АЧХ в полосе

пропускания. При ω→∞ АЧХ стремится к

нулю.[5]

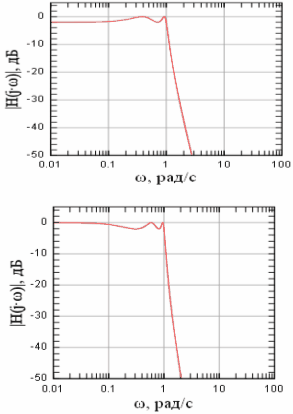

Рисунок 3.1 АЧХ фильтра Чебышева первого рода 4-го и 5-го порядков соответственно.

ФЧХ фильтра Чебышева изображены на рисунке 3.1.2.Из рисунка видно,что полоса пропускания становится более нелинейной при увеличении порядка фильтра. Обусловлено это колебательным видом АЧХ.[5]

Рисунок 3.2 ФЧХ фильтра Чебышева первого рода 4-го и 5-го порядков соответственно

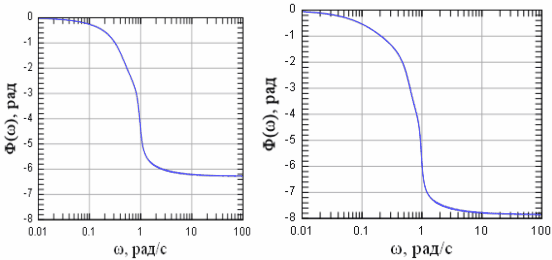

ХГВЗ фильтра Чебышева изображены на рисунке 3.1.3.В полосе пропускания при увеличении порядка фильтра отклоняется от идеальной функции . Это приводит к увеличению вклада фазовых искажений в общее искажение формы выходного сигнала.

Рисунок 3.3 ХГВЗ фильтра Чебышева первого рода 4-го и 5-го порядков соответственно

ХРЗ фильтра Чебышева на рисунке 3.1.4 имеет равноволновый характер в полосе пропускания и монотонный характер в переходной области и полосе задерживания. Количество колебаний в полосе пропускания возрастает с увеличением порядка фильтра.[5]

Рисунок 3.4 ХРЗ фильтра Чебышева

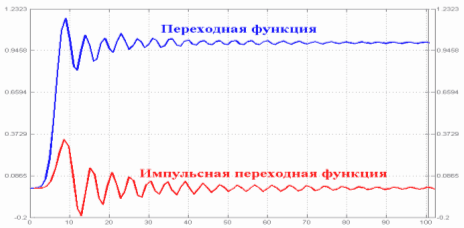

Временные характеристики фильтра Чебышева I рода (рисунок 3.1.5 )— импульсная переходная функция и переходная функция Импульсная переходная функция представляет собой реакцию фильтра на входной сигнал в виде дельта-функции Дирака, а переходная функция — реакцию на входное воздействие в виде единичной функции Хевисайда.

С увеличением порядка фильтра увеличиваются длительность переходного процесса, амплитуда колебаний (включая и амплитуду первого выброса), уменьшается размах основного лепестка импульсной характеристики при одновременном увеличении его длительности по уровню 0,5. Подобное поведение временных характеристик нежелательно при обработке импульсных сигналов, например телевизионных, поскольку при этом на изображении возникают окан-товки на яркостных переходах, уменьшается контрастность мелких деталей изображения.[5]

Рисунок 3.5 Импульсная переходная функция и переходная функция фильтра Чебышева

3.2 АППРОКСИМАЦИЯ ЧЕБЫШЕВА ИНВЕРСНАЯ (ВТОРОГО РОДА)

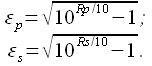

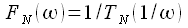

При

аппроксимации АЧХ многочленами Чебышева

задавалась допустимая неравномерность

АЧХ фильтров в полосе пропускания при

помощи параметра εp

. Однако можно также задать требуемый

уровень подавления в полосе заграждения

при помощи параметра

,

тогда получим фильтры Чебышева второго

рода или как их еще называют инверсные

фильтры Чебышева. Аппроксимирующая

функция в этом случае задается выражением

,

тогда получим фильтры Чебышева второго

рода или как их еще называют инверсные

фильтры Чебышева. Аппроксимирующая

функция в этом случае задается выражением

,

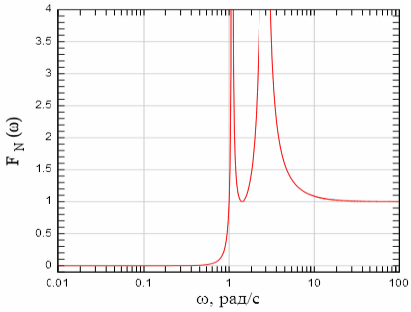

а квадрат модуля АЧХ представляется в

виде:

,

а квадрат модуля АЧХ представляется в

виде:

(3.5)

(3.5)

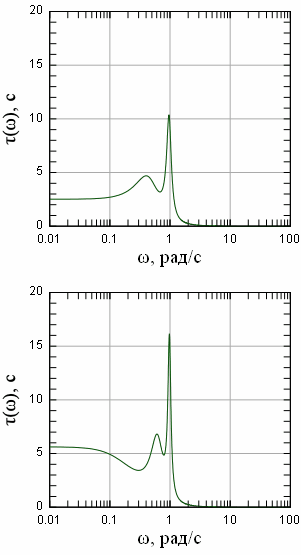

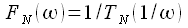

На

рисунках показаны аппроксимирующая

функция

и квадрат модуля АЧХ фильтра Чебышева

второго рода порядка N=4

при

и квадрат модуля АЧХ фильтра Чебышева

второго рода порядка N=4

при

(уровень подавления в полосе заграждения

равен

(уровень подавления в полосе заграждения

равен

)

)

Рисунок 3.3: Аппроксимирующая функция фильтра Чебышева второго рода 4-го порядка

Рисунок 3.4: Квадрат модуля АЧХ фильтра Чебышева второго рода 4-го порядка

Если

нормированный фильтр Чебышева первого

рода на частоте

«пропускает» сигнал, т.к.

«пропускает» сигнал, т.к.

Близко к единице (0 дБ), то нормированный

фильтр Чебышева второго рода на частоте

Близко к единице (0 дБ), то нормированный

фильтр Чебышева второго рода на частоте

«подавляет» сигнал, т.к.

«подавляет» сигнал, т.к.

.[4]

.[4]

Фильтры Чебышева второго рода целесообразно использовать для полосозаграждающих фильтров с заданным коэффициентом подавления.[4]

4. ВЫВОД ПЕРЕДАТОЧНОЙ ФУНКЦИИ ФИЛЬТРА ПО СТРУКТУРЕ РАУХА

В варианте данной курсовой работы предложено спроектировать полосовой фильтр восьмого порядка, используя структуру Рауха.

С целью вывода передаточной функции полосового фильтра по структуре Рауха рассмотрим фильтры второго порядка, которые будут соединены каскадно:

К1(р)

К2(р)

К3(р)

К4(р)

Рис.4.1 Структурная схема фильтра восьмого порядка

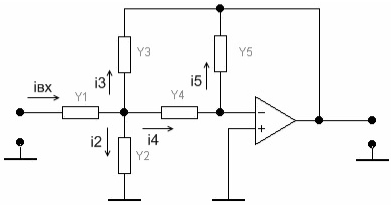

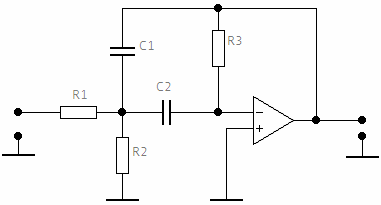

Построим принципиальную схему полосового фильтра восьмого порядка на операционном усилителе. Полосовой фильтр пропускает составляющие сигнала с частотами, лежащими между левой и правой частотой среза, а остальные задерживает, исходя из этого присутствие разделительных конденсаторов в ветвях схемы необходимо. Чтобы определить в какой именно ветви они должны стоять, сначала во все ветви поставим проводимости.

Рис.4.2 – Функциональная схема структуры Рауха второго порядка.

Найдём передаточную функцию каждого каскада.

(4.1)

(4.1)

Применим законы Кирхгофа:

(4.2)

(4.2)

(4.3)

(4.3)

(4.4)

(4.4)

(4.5)

(4.5)

(4.6)

(4.6)

(4.7)

(4.7)

(4.8)

(4.8)

(4.9)

(4.9)

Ток i4 протекает через проводимость Y4 и втекает в ветвь с проводимостью Y5 без потерь. Подставим (4.7), (4.8), (4.6) в (4.2), а затем получившееся выражение подставим в (4.5):

(4.10)

(4.10)

Подставим (4.4) в (4.10) и преобразуем, чтобы получить окончательное выражение для передаточной функции:

(4.11)

(4.11)

(4.12)

(4.12)

Общая же формула передаточной характеристики полосового фильтра имеет вид:

(4.13)

(4.13)

Анализируя выражения передаточной характеристики фильтра, определим типы проводимостей для обеспечения требуемой степени p. Так, сделаем вывод о том, что проводимости Y1, Y2 и Y5 должны заменить резисторы, а проводимости Y3 и Y4 – емкости:

(4.14)

(4.14)

Подставив (4.14) в (4.12) и преобразовав к виду (4.13), получим:

(4.15)

(4.15)

Таким образом, коэффициенты нормированного ФНЧ-прототипа для одного звена второго порядка можно представить следующим образом:

С учётом (4.14) построим принципиальную схему фильтра.

Рис.4.3 – Функциональная схема структуры Рауха второго порядка.

Данное функциональное звено представляет собой активный фильтр второго порядка, построенный на основе операционного усилителя.

5 МОДЕЛИРОВАНИЕ ФИЛЬТРА НА ФУНКЦИОНАЛЬНОМ УРОВНЕ В СИСТЕМЕ MATHCAD В ЧАСТОТНОЙ И ВРЕМЕННОЙ ОБЛАСТЯХ (РАСЧЕТ АЧХ, ФЧХ, ХРЗ, ХГВЗ, ИХ, ПХ В НОРМИРОВАННОМ И ДЕНОРМИРОВАННОМ ВИДАХ)

Для моделирования на функциональном уровне будем использовать Math CAD .

Операторную передаточную функцию можно записать в следующем виде:

(5.1)

(5.1)

где K(w)-амплитудно-частотная характеристика;

φ(w)-фазо-частотная характеристика.

Амплитудно-частотная характеристика определяется следующим образом:

(5.2)

(5.2)

Фазо-частотная характеристика определяется следующим образом:

(5.3)

(5.3)

Построим АЧХ и ФЧХ в Math CAD:

Исходные данные:

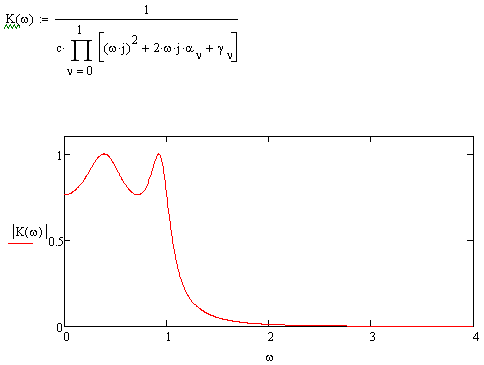

Построим АЧХ фильтра прототипа нижних частот:

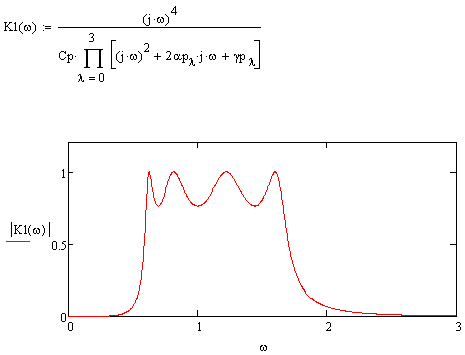

Рисунок 5.1 АЧХ фильтра прототипа нижних частот в нормированном виде

Для построения характеристик ПФ, осуществим пересчёт параметров.

Исходя из того, что

Kфнч(p)=А(p~+1/p~)=Kпф(p~) (5.4)

Получим выражения для пересчёта параметров:

В

выражениях 5.5-5.13

,

где

,

где

и

и

.

.

Построим АЧХ ПФ.

Рисунок 5.2 АЧХ ПФ в нормированном виде

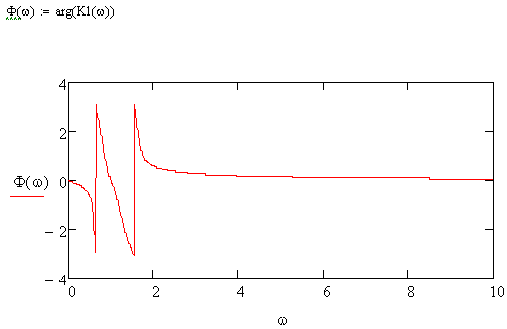

Построим ФЧХ ПФ.

Рисунок 5.3 ФЧХ ПФ в нормированном виде

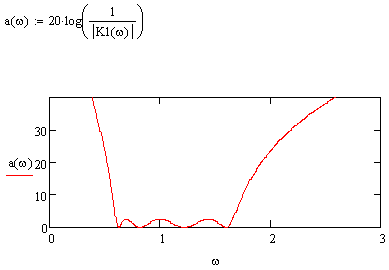

Построим характеристику рабочего затухания.

Рисунок 5.4 ХРЗ ПФ в нормированном виде

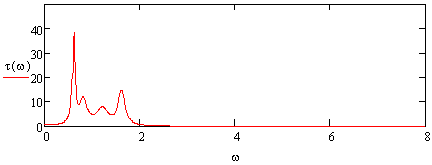

Построим характеристику группового времени запаздывания:

Рисунок 5.5 ХГВЗ ПФ в нормированном виде

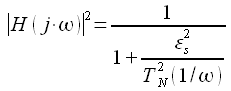

Построим импульсную и переходную характеристики:

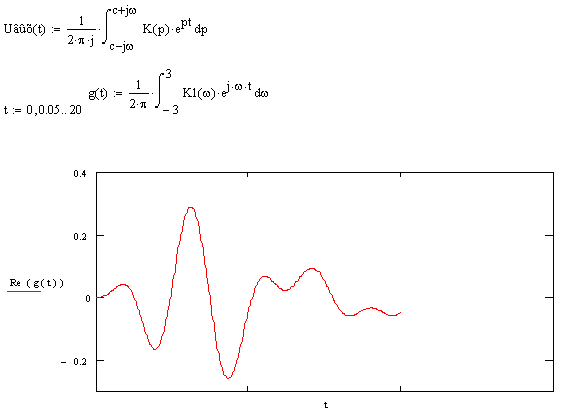

Так как импульсная характеристика – это реакция системы на δ-функцию, выражение для её построения получим следующим образом:

U

вх=δ(t)

1

вх=δ(t)

1

Uвых=K(p)* Uвх(p)

Рисунок 5.6 ИХ ПФ в нормированном виде

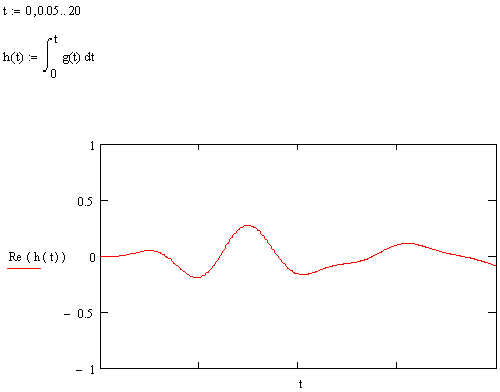

Переходная характеристика – реакция системы на единичный скачок(на функцию Хевисайда), поэтому выражение для её построения получим следующим образом:

1

(t)

1/p

(t)

1/p

h(t)= Uвых(t)=1/2*П*j

Рисунок 5.7 ПХ ПФ в нормированном виде

Чтобы построить данные характеристики фильтра в денормированном виде, необходимо получить параметры ПФ в денормированном виде. Для этого воспользуемся следующими выражениями:

(5.14)

(5.14)

(5.15)

(5.15)

(5.16)

(5.16)

(5.17)

(5.17)

В этих

выражениях

- денормированная частота, а

- денормированная частота, а

.

.

Таким образом деномированные коэффициенты равны:

Сpd=2.925739792537995685239e-17

Сpd=2.925739792537995685239e-17

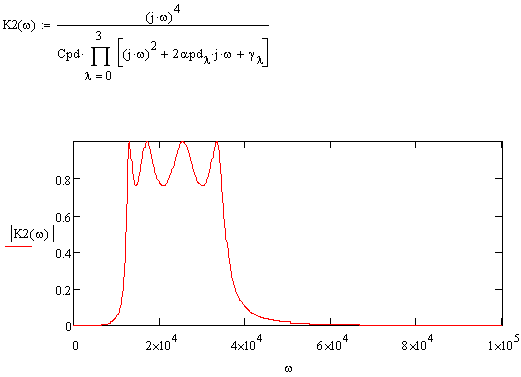

Построим АЧХ ПФ в денормированном виде:

Рисунок 5.8 АЧХ ПФ в денормированном виде

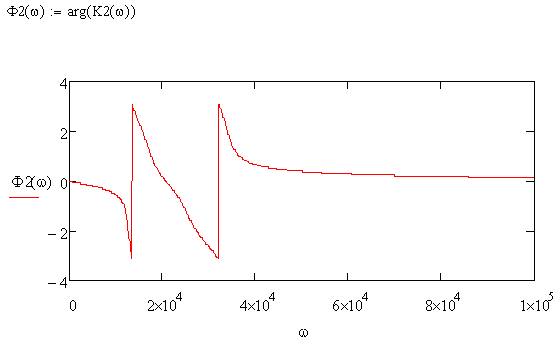

Построим фЧХ ПФ в денормированном виде:

Рисунок 5.9 ФЧХ ПФ в денормированном виде

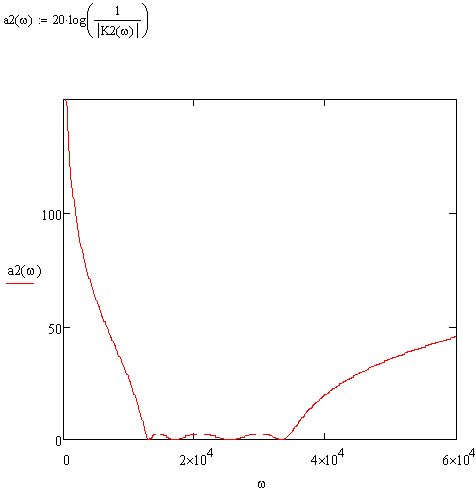

Построим ХРЗ ПФ в денормированном виде:

Рисунок 5.10 ХРЗ ПФ в денормированном виде

Построим ХГВЗ ПФ в денормированном виде:

Рисунок 5.11 ХГВЗ ПФ в денормированном виде

Построим ИХ и ПХ ПФ в денормированном виде:

Рисунок 5.12 ИХ ПФ в денормированном виде

Рисунок 5.13 ПХ ПФ в денормированном виде

Анализ результатов вычислений показывает, что операция денормирования произведена верно, так как характеристики фильтра в денормированном виде отличны от характеристик в нормированном виде представляемой областью частот.

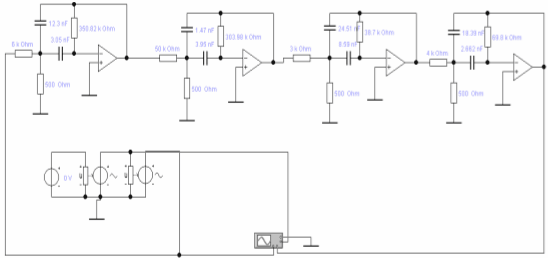

6 РАЗРАБОТКА ПРИНЦИПИАЛЬНОЙ СХЕМЫ ФИЛЬТРА, РАСЧЕТ ЭЛЕМЕНТОВ

Для построения принципиальной схемы восьмого порядка необходимо последовательно соединить четыре функциональных звена второго порядка структуры Рауха, изображение которого представлено на рисунке 4.3.

Операторную функцию представим произведением операторных функций каждого звена :

Операторная функция каждого звена запишется следующим образом:

Нормирующий множитель С распределим между каскадами следующим образом:

(6.3)

(6.3)

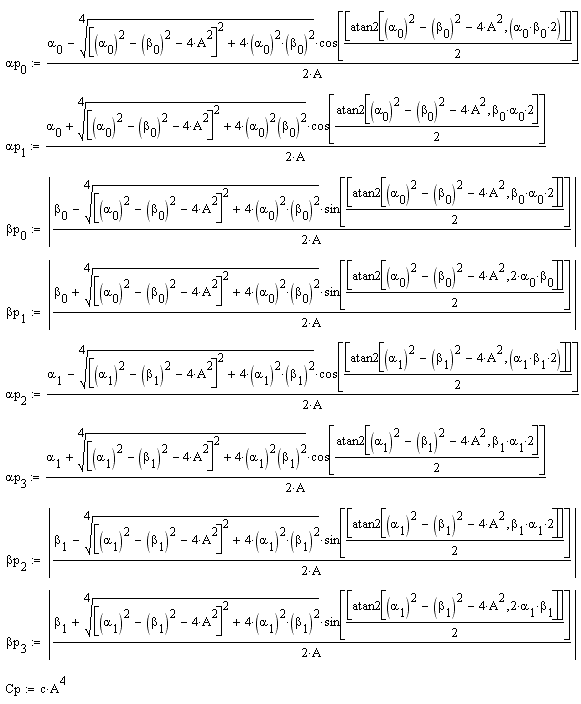

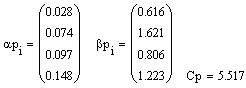

Чтобы рассчитать элементы принципиальной схемы фильтра, нужно решить четыре системы (4.16) (для четырёх каскадов второго порядка).

Система (4.16) для одного каскада второго порядка представляет собой три уравнения с пятью неизвестными, то есть с двумя степенями свободы. Следовательно, два элемента зададим произвольно. Рациональнее задавать сопротивления резисторов. Однако значения сопротивлений резисторов должны удовлетворять следующему условию:

(6.9)

(6.9)

Значения нормирующего коэффициента для всех каскадов согласно (6.3):

Расчёты будем производить в MatCad.

Решим систему (4.16) для первого каскада второго порядка. Для этого необходимо задать R1, R2 следующим образом:

Для удобства изменим нумерацию элементов согласно схеме.

Решим систему (4.16) для второго каскада второго порядка. Для этого необходимо задать R5, R4 следующим образом:

Решим систему (4.16) для третьего каскада второго порядка. Для этого необходимо задать R7, R8 следующим образом:

Решим систему (4.16) для четвёртого каскада второго порядка. Для этого необходимо задать R10, R11 следующим образом:

Таким образом, определим вид принципиальной схемы (приложение А).

Определив элементы принципиальной схемы фильтра, рассчитаем АЧХ данного фильтра непосредственно через значение элементов.

В выражение передаточной функции для каждого каскада фильтрации подставим коэффициенты с учётом выражений для сопротивлений и ёмкостей.

Построим амплитудно-частотную характеристику:

Сравним АЧФ, полученную через значения элементов цепи и денормированную АЧХ. Так как эти характеристики совпадают, то можно сделать вывод, что элементы цепи рассчитаны верно.

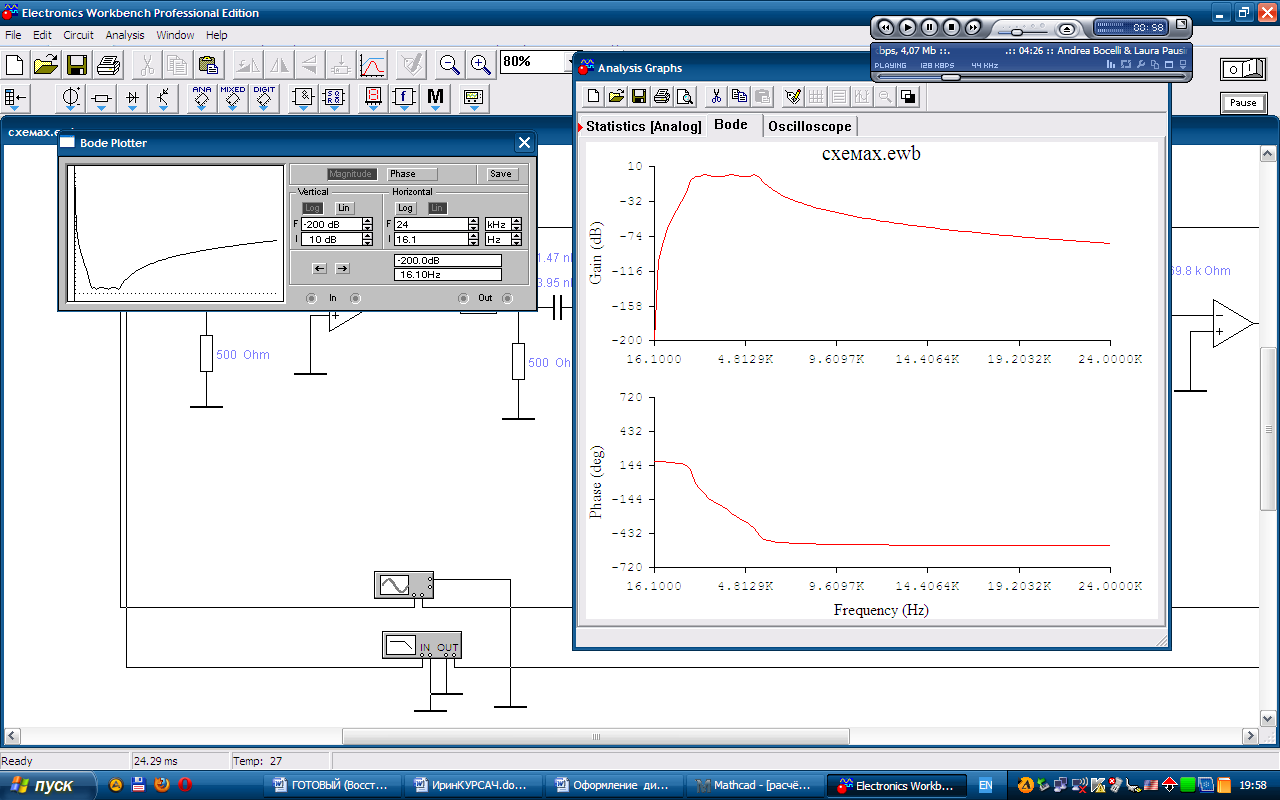

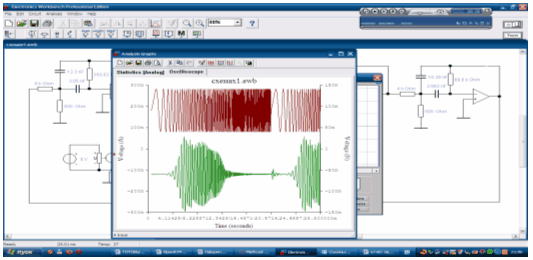

7 МОДЕЛИРОВАНИЕ ФИЛЬТРА НА СХЕМАТЕХНИЧЕСКОМ УРОВНЕ В СИСТЕМЕ ELECTRONIC WORKBENCH В ЧАСТОТНОЙ И ВРЕМЕННОЙ ОБЛАСТЯХ (ИЗМЕРЕНИЕ АЧХ, ФЧХ, ЧРЗ, ИХ, ПХ)

Программа «Electronic Workbench» предназначена для синтеза и анализа дискретных и аналоговых схем на основе стандартных компонентов, входящих в базовый набор программы, используются также при применении созданных пользователем блоков.

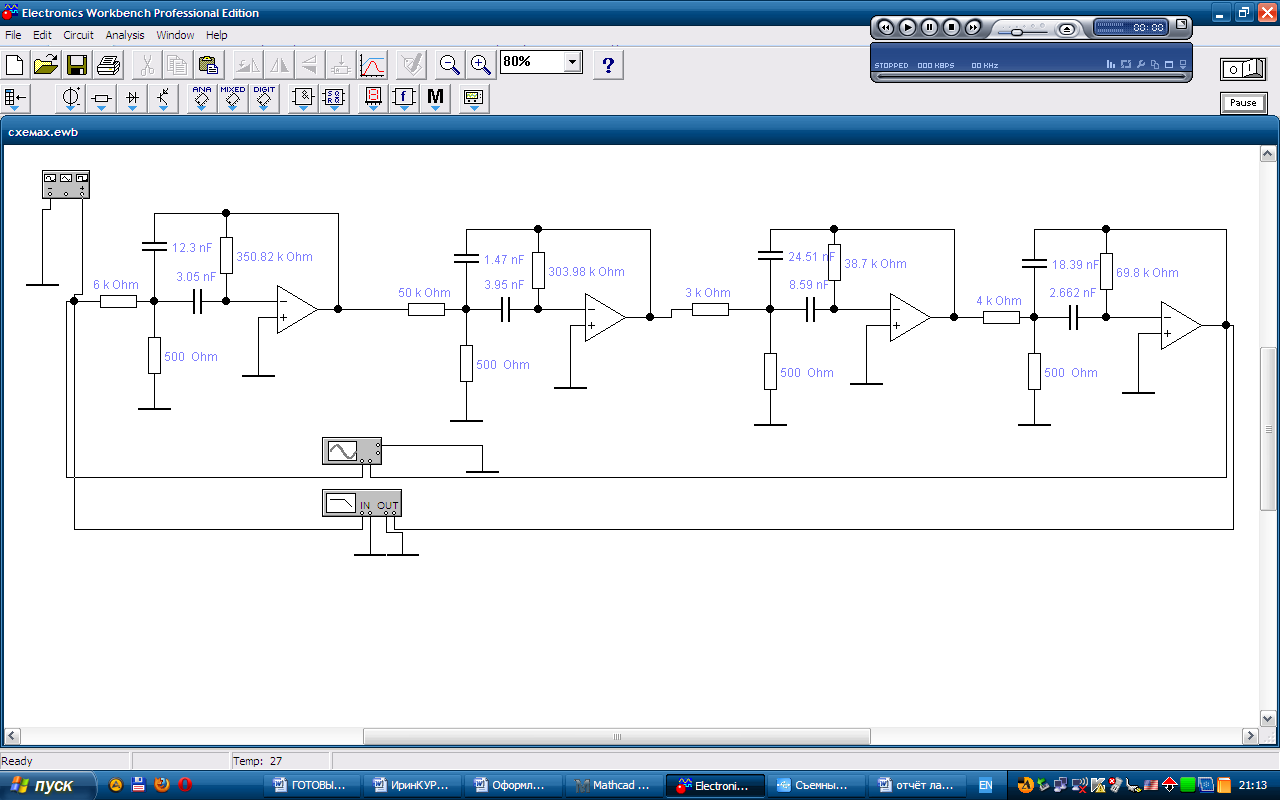

Соберем в Electronics Workbench принципиальную схему, определенную приложением А. Зададим в схеме рассчитанные в разделе 6 номиналы элементов.

К схеме подключим функциональный генератор, осциллограф и измеритель частотных характеристик. Принципиальная схема, позволяющая осуществить измерение перечисленных характеристик, изображена на рисунке 7.1. В функциональном генераторе зададим периодическую последовательность прямоугольных видеоимпульсов частотой следования 100 Гц и амплитудой 100 мВ.

Рисунок 7.1 Электрическая схема системы фильтрации

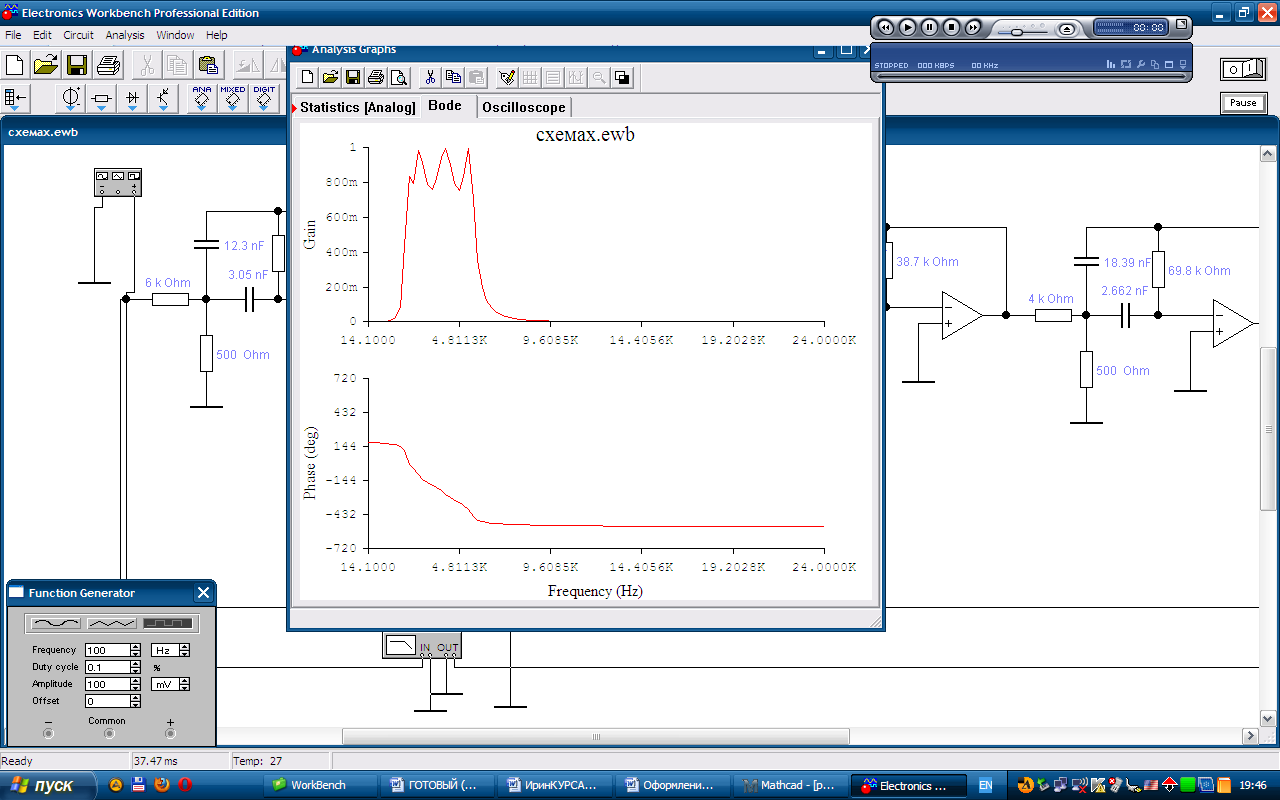

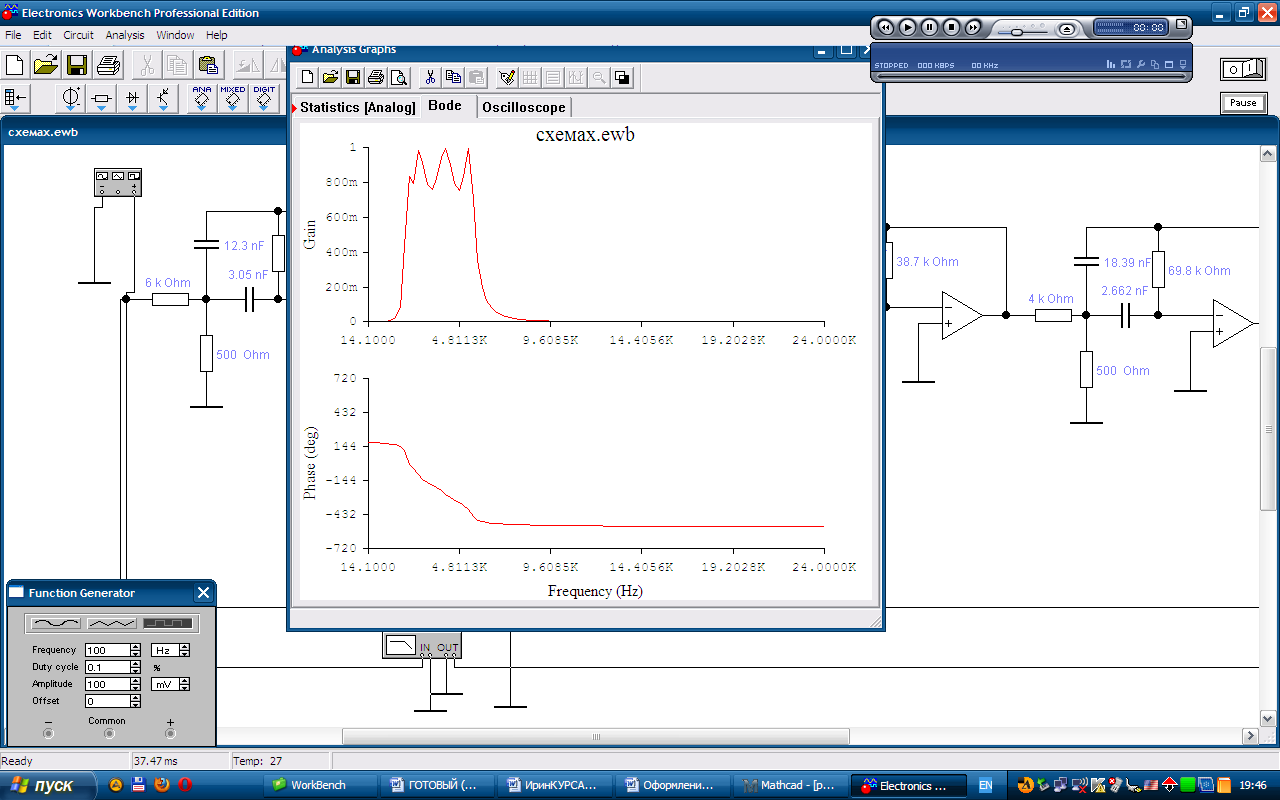

С помощью измерителя частотных характеристик измерим АЧХ, ФЧХ и ХРЗ.

Рисунок 7.2 АЧХ ПФ

Рисунок 7.3 ФЧХ ПФ

Рисунок 7.4 ХРЗ ПФ

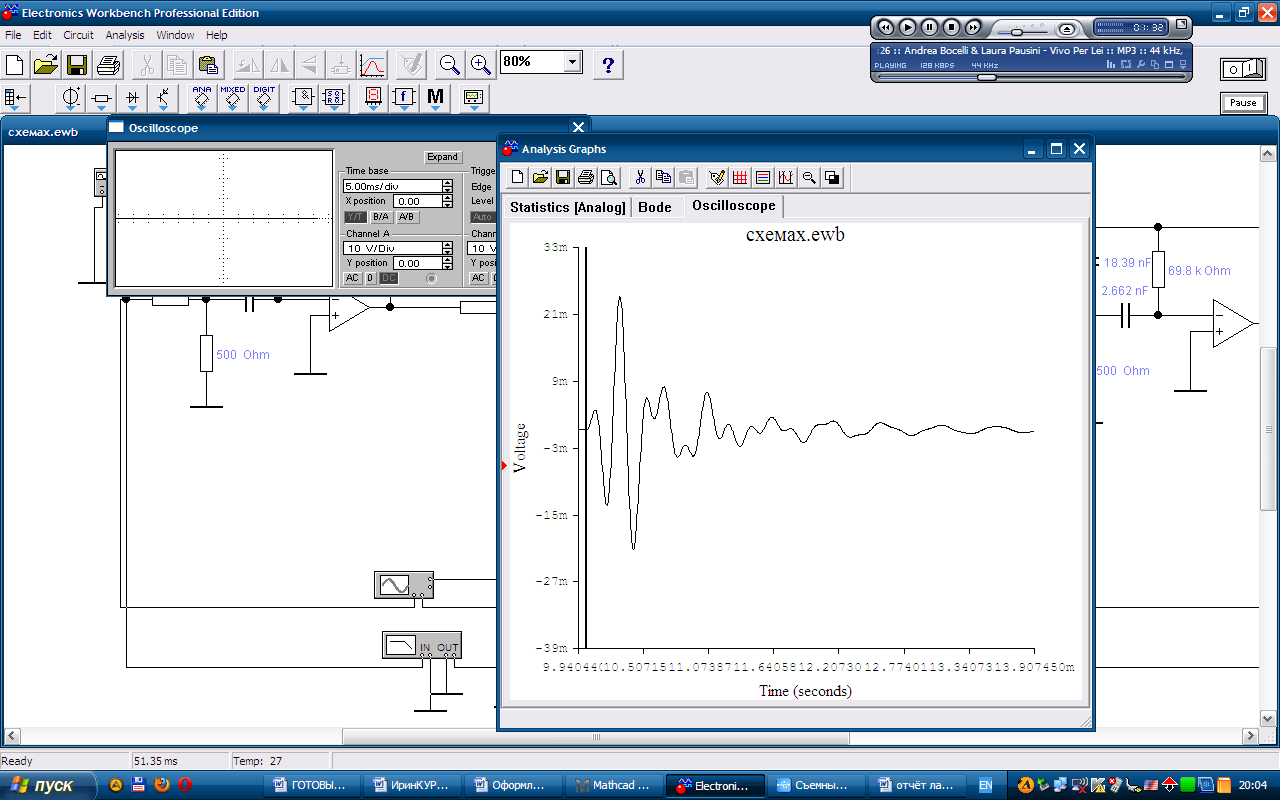

Для измерения импульсной характеристики ввиду невозможности физического моделирования идеального импульсного воздействия зададим скважность входной последовательности видеоимпульсов, равную 1%.

Рисунок 7.5 Импульсная характеристика ПФ

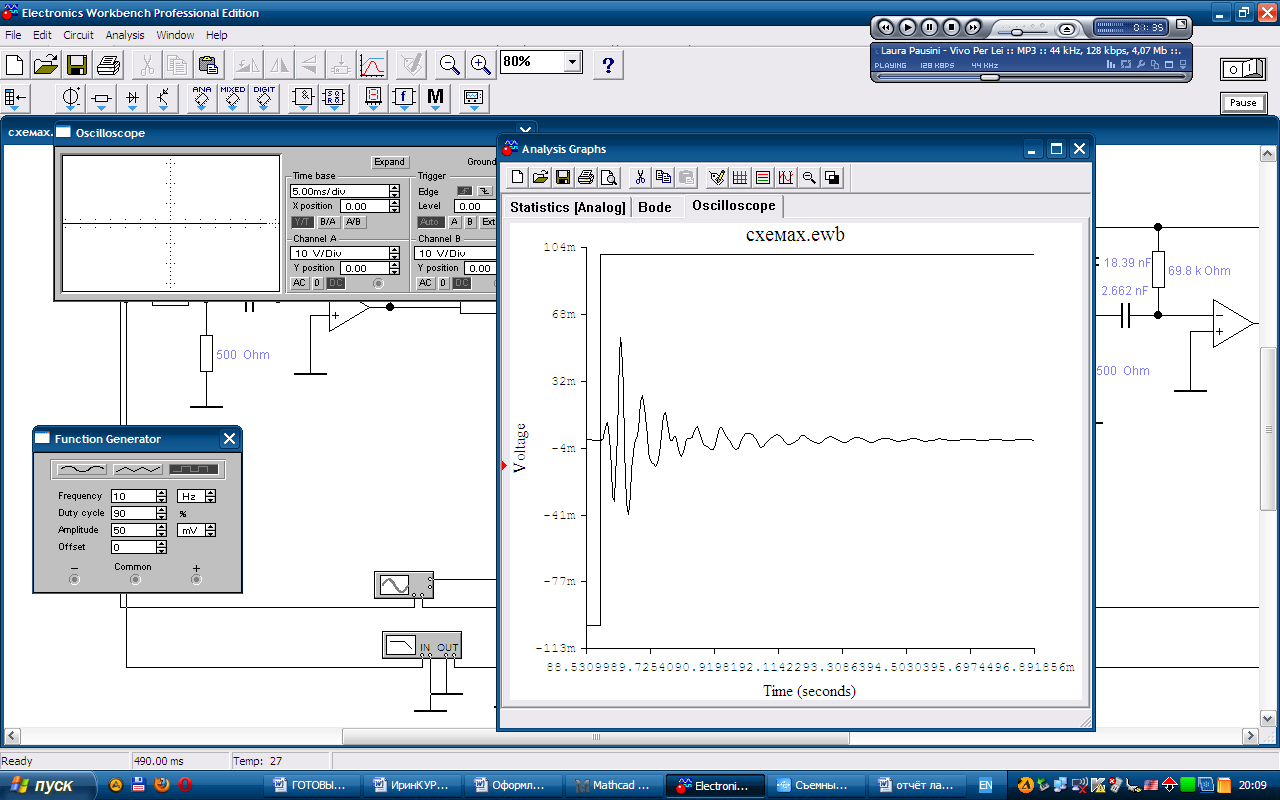

Для измерения переходной характеристики зададим скважность входной последовательности видеоимпульсов, равную 90 %.

Рисунок 7.6 Переходная характеристика ПФ

Измеренные характеристики схожи с характеристиками, построенными в разделе 5 (рисунки 5.8-5.10, 5.12-5.13). Следовательно, можно сделать вывод о корректном проектировании устройства фильтрации на функциональном и схемотехническом уровнях.

8 ИЗМЕРЕНИЕ АЧХ ФИЛЬТРА В СИСТЕМЕ ELECTRONIC WORKBENCH С ПОМОЩЬЮ ЛЧМ СИГНАЛА

У сигналов с линейной частотной модуляцией частота колебания изменяется не по гармоническому, а по линейному закону. При прохождении через линейное звено помимо модуляции частоты по линейному закону они дополнительно приобретают амплитудную модуляцию. Поэтому огибающая ЛЧМ сигнала изменяется по закону амплитудно-частотной характеристики линейного звена.

Соберем схему генератора ЛЧМ сигнала, состоящую из генератора сигнала синусоидальной формы, управляемого напряжением, генератора линейно изменяющегося напряжения, выход которого подключен к управляющему входу генератора сигнала синусоидальной формы. В качестве генератора линейно изменяющегося напряжения используем генератор напряжения пилообразной формы, управляемый напряжением, к управляющему входу которого подключен источник постоянного напряжения.

Сформированный ЛЧМ сигнал подадим на вход фильтра, сигнал от генератора пилообразного напряжения – на вход синхронизации осциллографа. Принципиальная схема для измерения АЧХ ПФ с помощью ЛЧМ-сигнала приведена на рисунке 7.1.

Рисунок 8.1 Принципиальная схема для измерения АЧХ ПФ с помощью ЛЧМ-сигнала

Рассмотрим ЛЧМ-сигнал на входе и выходе ФНЧ

Рисунок 8.2 – ЛЧМ-сигнал на входе и выходе ПФ

Из рисунка 8.2 видно, что огибающая выходного сигнала соответствует форме амплитудно-частотной характеристики проектируемого ПФ.

ЗАКЛЮЧЕНИЕ

В данной курсовой работе спроектирован полосовой фильтр восьмого порядка с аппроксимацией Чебышева. В качестве схемной реализации использовано четыре звена структуры Рауха. Данный фильтр обладает хорошей стабильностью характеристик и низким выходным полным сопротивлением, однако невозможно достичь высокого значения добротности Q без значительного разброса значений элементов и высокой чувствительности к их изменению. Таким образом, его можно сразу соединять каскадно с другими звеньями для реализации фильтра более высокого порядка.

В данной курсовой работе было рассмотрено моделирование фильтра на функциональном уровне и были определены его характеристики во временной и частотной областях, которые соответствуют теоретическим сведеньям о фильтрах. В результате моделирования на схемотехническом уровне были сняты рассчитанные характеристики с помощью измерительных приборов и отмечено их соответствие техническим требования. Кроме того была возможность убедится в правильности вывода операторной функции и расчете электрических элементов.

СПИСОК ИСПОЛЬЗОВАННЫХ ИСТОЧНИКОВ

1 Chip-news [Электронный ресурс]. Режим доступа: www.chip-news.ru/archive/chipnews/200810/Article_05.pdf

2 Window.edu [Электронный ресурс]. Режим доступа: http://window.edu.ru/window_catalog/pdf2txt?p_id=42321&p_page=4

3 Лэм, Г. Аналоговые и цифровые фильтры. Расчет и реализация./Г.Лэм. - Москва: Мир, 1982-589 с.

4 Dspsystem [Электронный ресурс]. Режим доступа: www.dspsystem.narod.ru/content/filters/cH3/cH3.html

5

Антонью, А. Цифровые фильтры: анализ и

проектирование./А.Антонью - Пер. с

англ.-М.: Радио и связь.1983.-320 с.