Управляющие устройства и их виды

Управляющие устройства (УУ): их виды

Операционные устройства позволяют выполнить преобразование некоторых кодов в соответствии с логикой выполняемой операции.

При этом операционное устройство может быть представлено множеством микроопераций, которые могут быть выполнены последовательно или параллельно при инициировании определённых составляющих узлов с помощью выделенных сигналов управления.

Например, сложение/вычитание двоичных кодов выполняется следующей последовательностью сигналов:

Z=X+Y

ПрРг1;

ПрРгВ;

(+) (-)

ПрРгАПК или ПрРгАИК

ПрРгСм или ПрРгСм+1

ПрШДвых

Т.о. возникает необходимость в использовании спец. устройства (устройство управления), которое предназначено для формирования распределённой во времени последовательности управляющих сигналов, подаваемых на компоненты операционного блока вместе с сигналом синхронизации и обеспечивающие выполнение заданной операции.

Существуют 2 принципиально разных подхода к УУ:

1)УУ с жесткой логикой;

2) УУ с микропрограммной логикой или МПУУ

УУ с жесткой логикой строятся на основе жестко заданных связей между его компонентами, реализующих формирование и передачу сигналов управления в требуемой последовательности, учитывая состояние УУ, выполняемую операцию и значения т.н. «осведомительных сигналов», характеризующих результаты выполнения предыдущей операции, а также состояния требуемых компонент операционного устройства.

УУ с жесткой логикой не поддаются модификации и при необходимости изменений должны быть полностью заменены.

Основное их достоинство – высокая производительность, связанная с формированием управляющих сигналов с помощью комбинационных схем.

Управляющие устройства с жесткой логикой представлены координационными схемами, который обеспечивают построение распределения во времени последовательности сигналов управления, в зависимости от кода операции и № такта сигнала синхронизации.

При этом учитывается значение осведомительного сигнала от операционного устройства.

ПоПо ходу операции из Рг команд, дешифратор кода активирует 1 выходную линию, соотв. выполняемой команде. Счетчик тактов запускается с мом. выполнения тек. команды. Дешифратор нового такта активизирует 1 вых. линию, соотв. № такта.

В результате устр. обр. упр. сигналов, в зависимости от № такта и вып. команды, с помощью логических схем «и/или», формирует требуемую последовательность управляющих сигналов, инициализирующих выполняемые последовательности МО в операционных устройствах.

Недостаток данного устройства – ориентация на выполнение команд, требующих одинакового количества тактов, поэтому для ее исп. необх. «выровнять» все команды по команде, треб. max числа тактов.

Команды, треб. min количества тактов – однобайтные команды, или команды с min количеством бит (команды обр. регистров, изм. режимов, команды установки и т.д.).

В отличие от них, длинные команды исп. смешанную адрессацию (регистровую и непосредственную, косвенную).

Поэтому выравнивание команд приводит к неэф-му исп. памяти.

Для повышения эф-ти устр. упр. с ж. л. исп. счетчики тактов, обеспечивающие выполнение требуемого типа команд.

В качестве примера рассмотрим управляемое устройство, обеспечивающее выполнение, или поддержку коротких и длинных команд.

В зависимости от типа команды по длине, схема управления предоставляет возможность активизировать или только счетчик тактов 1, или на определенном такте запускать счетчик тактов 2, реализуя выполнение команд, требующих большего количества тактов.

Рассмотрим, каким образом можно обеспечить образование сигналов управления.

Для этих целей используется комбинации логических элементов «и/или», которые в зависимости от типа команды (код команды), № такта и знач. осведомительных сигналов, формируют необходимые сигналы упр.

На примере форм-я сигнала упр. ВР можно говорить, что этот сигнал генерируется при вып. j-й команды во всех тактах, кроме к-го при наличии освидомит. сигнала L.

Для построения устр. упр. с ж. л. используется объединение микропрограмм, включая все выполняемые микропрограммы, кажд. из кот. соотв. некоторому коду команды.

Микропр-ма предст. собой последовательность, а также разветвление выполнения отдельных микропрограмм, в зависимости от кода вып. команды и знач. осведомит. сигналов.

Объедененная микропрограмма м.б. построена по след. схеме:

Для искл. микроопер., вход. во все микропр-ы, их общие части, связ. с начальной инициализацией, а также корректным завершением выполнения, выделяются в общие части микрокоманды. Исключенные части каждой микропер., инициализируются в зав. от кода выполняемой микропрограммы.

Для исп. понятий автоматов при постр. устр. упр. необходимо выделить состояния устр. упр., а также усл. перехода из 1 сост. в др. Для автомата Мура, в кач. состояний исп. события генерации (возникновение соотв. сигналов упр.).

Некоторые сост. могут порождать в т. сл. формирование нескольких сигналов упр. После этого усл. перехода из сост. в сост. будут иметь значения соотв. осведомит. сигналов.

В т. сл. для хранения инф. о тек. сост. автомата упр. можно исп. набор триггеров, кол-во кот. k=ln r, r – кол-во состояний.

Иными словами мыпронумеруем все сост. и сопоставим всем сост. некоторый 2-й код, соотв. данному сост. Зная порождаемые сигналы упр. каждым сост., можно, исп. логическую схему «или» и дешифратор состояния, обеспечить формир-е требуемых сигналов упр.

Автомат Мили требует меньшего кол-ва триггеров для отобр. состояний, т.к. описывается меньшим кол-ом состояний, но его недостаток – изменение состояния происходит при изм. освед. сигн., что может повлеч изм. упр. сигн., кот. будут преждевременными для текущей выполняемой команды.

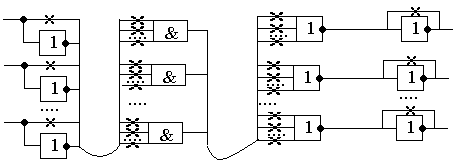

Поэтому аппарат Мили применяют со схемами задержки, либо в комбинации: Мура – Мили. Для построения устр. упр. с ж. л. исп. программируемые логические матрицы, которые содержат слой входных инверторов, слой эл-ов «и», слой эл-ов «или» и слой вых. инверторов. Крестики – возможность разорвать соотв. цепь в процессе программирования матрицы.

Матрица образована т.о., что на любой эл-т «и» м.б. поданы все знач. прямых и инвертных входных сигн. На вход любого эл-та «или» м.б. поданы выходы любого эл-та «и».

МПУУ – требуемый набор управляющих сигналов сохраняется в т.н. «микропрограммной памяти» с доступом только для чтения (read-only).

Каждый набор таких сигналов соответствует некоторой микрооперации и представлен в виде микрокоманд.

В соответствии с логикой выполнения операции каждая микрокоманда в микропрограмме определяет (содержит) адрес следующей микрокоманды, необходимой для выполнения операции.

МПУУ функционируют с использованием доступа к МП-памяти, поэтому их применение стало оправданным лишь с появлением быстрых модулей памяти.

Основное достоинство МПУУ – возможность модернизации процессора или замены множества выполняемых операций путём перехода к новым модулям МП-памяти.

Т.к. МП-память входит в состав процессора в виде компонента УУ, то данное преимущество даёт возможность автоматизированного и автоматического проектирования компонент УУ и микропроцессора в целом.

Для выработки управляющих сигналов используются следующие обозначения:

каждый управляющий сигнал соответствует некоторой операции, реализуемой операционным блоком. Пусть V>1>…V>m> – совокупность управляющих сигналов, причём V>i> инициирует выполнение соответствующей микрооперации.

При выработке управляющих сигналов используются U>1>…U>n> – значения «осведомительных сигналов» о результатах выполнения предыдущей операции, а также о состоянии компонент операционного устройства.

УУ может находиться в одном из состояний множества

Q={Q>1>,Q>2>,…,Q>L>}

Множество выполняемых операций y>1>…y>s>

УУ можно представить некоторым конечным автоматом, соответствующим логике автомата Мура или автомата Мили.

Переход в новое состояние для автомата Мура определяется некоей функцией А от текущего состояний, выполняемой операции и значения.

Q(t+1)=A(Q(t),y>i>,u>1>…u>n>)

вых. сигналы:

V>1>=F>1>(Q(t),y>i>), V>2>=F>2>(Q(t),y>i>), …V>m>=F>m>(Q(t),y>i>)

Т.о. значения управляющих сигналов при построении УУ как автомата Мура, зависят только от состояния УУ.

При построении УУ как автомата Мили, выработка управляющих сигналов зависит также от значений «осведомительных сигналов»

V>1>=f>1>(Q(t),y>i>,u>1>…u>n>), V>2>=f>2>(Q(t),y>i>,u>1>…u>n>), …V>m>=f>m>(Q(t),y>i>,u>1>…u>n>)

Построение автомата Мура требует большего использования компонент для отражения состояния автомата (памяти).

Построение автомата Мили снижает количество элементов памяти для отражения его состояния и требует больше сложных преобразований всех входящих аргументов, поэтому применяют оба подхода.

Каждая микрооперация имеет определенную длительность.

Для использования min количества тактовых импульсов синхросигнала все микрооперации «выравнивают» по самой долгой. Любая микрооперация может быть инициирована только на границе тактов.

Т.о. последовательность микроопераций реализуется последовательностью управляющих сигналов, подаваемых в начале каждого такта сигналов синхронизации.

Не смотря на то, что идея МПУУ была известна с 1951г. как подход к построению УУ с упорядочением формирования управляющих сигналов.

УУ состоит из памяти (матрица С), содержащей 2S различных микрокоманд, где S – код, адрес соотв-щей микрокоманды.

Если по каким-либо правилам задать адрес первой микрокоманды, выполняющей заданную операцию и разместить её в РгАдреса МикроКоманды, а затем подать на дешифратор с сигналами синхронизации, то на выходе ДШ будет активизирована одна выходная горизонтальная линия, соответствующая выполняемой микрооперации.

В таком случае на вертикальных шинах матрицы С, которые связаны с соответствующей горизонтальной линией, появятся сигналы управления.

Матрица С связана с Т, которая аналогичным образом позволяет формировать адрес следующей микрокоманды.

Использование специального триггера условий позволяет учесть значения «осведомительных сигналов» и выполнить разветвление в микропрограмме путём перехода к другой горизонтальной линии, которая задаёт другой адрес следующей микрокоманды.

Задержка сигналов нужна, чтобы формировать новые управляющие сигналы после выполнения текущей микрокоманды.

Последовательность микрокоманд должна получить естественное завершение. Практическая реализация МПУУ связана с использованием различных форматов микрокоманд и различных модулей МП-памяти.

МП-управление с одной стороны позволяет адаптировать систему команд к потребностям выполнения алгоритмов программ. С другой стороны позволяет упростить и автоматизировать процессы проектирования УУ и микропроцессоров в целом.

Состав: УФАМК – устройство формирования адреса микрокоманды; РгАМК – регистр адреса микрокоманды; ПМК – память микрокоманды; РгМК – регистр микрокоманды; ДШМК – дешифратор микрокоманд (дешифратор микрооперации); КОП - код операции.

Начальный источник операции – регистр команд, из которого используется код операции микрокоманды. На основании этого кода УФАМК формирует первой микрокоманды в составе МП-программы, обеспечивающей выполнение данной команды.

Один из вариантов формата микрокоманды следующий: код МО из РгМК попадает в ДшМК, который используется для образования управляющих сигналов.

|

код МО |

адрес след. МК |

Управляющие сигналы идут на операционное устройство и совместно с сигналами синхронизации обеспечивают (синхронизируют) выполнение одной или нескольких микроопераций в составе операционного устройства (АЛУ).

Адресная часть микрокоманды идет в УФАМК для выбора следующей микрокоманды.

На выбор следующей микрокоманды влияют результаты выполнения предыдущей микрооперации, поступающей из операционного блока. Процесс идет до выполнения всех операций в составе команды.

Для кодирования микрокоманд используется несколько форматов:

Горизонтальное кодирование: поле команды, соответствующее коду микрооперации представлялось в виде

V>1>|V>2>|…|V>n>|Адрес.

Каждый разряд поля соответствует одному функциональному сигналу УУ, соответствующему некоторой микрооперации операционного устройства. Если в этом поле - «1» то это значит, что соответствующая микрооперация будет инициализирована независимо от содержания других рядов этого поля. В таком случае каждой микрокоманде единичные разряды поля микрооперации обеспечивают выполнение соответствующих функций операционного устройства.

Недостаток - длина микрокоманды, учитывая, что количество микроопераций может составлять несколько сот. С другой стороны, учитывая, что многие микрокоманды несовместимы, соответствующее поле микрокоманды будет состоять практически из нулей.

Вертикальное кодирование. В поле микрооперации находится код микрооперации, который для дальнейшего использования требует дешифратора. Недостаток – «длинный» микропрограммы, т.к. в каждом такте сигналов синхронизации может быть активизирована только одна микрооперация.

На практике распространено смешанное кодирование в 2-х вариантах: вертикально-горизонтальное и горизонтально-вертикальное.

Ветртикално-горизонтальное: всё множество операций V разбивается на k подмножеств V>i>. Каждое подмножество размещается в составе поля микрооперации, занимая фиксированный размер в составе поля.

Такие микрокоманды называют микрокоманды с полевой структурой. Каждое такое выделенной поле управляет некоторым подмножеством микроопераций, задавая код данной микрооперации. В результате требуется k дешифраторов.

Данный подход позволяет объединять в одном такте выполнение k микроопераций.

Горизонтально-вертикальное содержит поле микрооперации из двух частей:

V>1>|V>2>|…|V>k>| l

Первая область содержит некоторые управляющие сигналы, содержание и значение которых зависит от кода во второй области.

Если нужно совместить в одном такте сигналов синхронизации принципиально несовместимые микрооперации, то используют т.н. многофазные микрокоманды, в которых период сигналов синхронизации делится на фазы, в течении которых выполняются определённые компоненты микрокоманды.

Все форматы микрокоманд обеспечивают одни цели: увеличение производительности, уменьшение времени выполнения, уменьшение требуемых объемов памяти для хранения микрокоманд.

Если микропроцессор предназначен для выполнения строго очерченного множества операций с максимально высокой производительностью, то УУ строится как автомат с жесткой логикой.