Выборочные ответы к государственному экзамену факультета ВМС специальности 2201

Билет №17 вопрос №1

Структура и компоновка ОЗУ основных моделей СМ ЭВМ.

Данный вопрос рассмотрим на примере модулей памяти модели СМ 1810. Модуль оперативный запоминающий МОЗ 256 СМ. Он предназначен для приема, хранения и выдачи оперативной информации в качестве встроенной оперативной памяти в составе микроЭВМ СМ 1810. Модуль имеет следующие технические характеристики:

Объем – 256 Кб

Разрядность – 8 и 16 бит

Порядок обращения – произвольный

Выполняемые операции – запись слова (ЗПС), чтение слова (ЧТС), запись байта (ЗПБ), чтение байта (ЧТБ)

Цикл обращения – при операциях ЧТС, ЗПС, ЧТБ не более 0,7 мкс, при операции ЗПБ не более 1,4 мкс

Модуль обеспечивает коррекцию одинарной и обнаружение двойной ошибки. На рис. показана структурная схема модуля. Узел приема осуществляет формирование адреса обращения к требуемой ячейке памяти при обращении к модулю со стороны интерфейса И41, узел обработки данных осуществляет прием и выдачу данных на (из) интерфейса И41. В его состав входит корректор, обеспечивающий при операциях записи формирование контрольных разрядов накопителя. При операциях чтения корректор формирует признаки одинарной и двойной ошибки и в случае одинарной ошибки производит коррекцию данных и выдачу их через соответствующий буферы на интерфейс И41. Узел управления формирует сигналы управления другими узлами модуля и соответствующую диаграмму. В его состав входит контроллер памяти КМ1810ВТ03, осуществляющий формирование управляющих сигналов для динамических микросхем памяти, прием и мультиплексирование адресов строки и столбца, а также формирует режим регенерации.

Узел накопителя предназначен для записи, хранения и выдачи информации представляет собой матрицу микросхем памяти К565РУ5 (64К х 1). Матрица содержит два ряда по 22 микросхемы. Разряд данных включает в себя по одной микросхеме из каждого ряда; таким образом, в матрице всего по 16 информационных и 6 контрольных разрядов. Полная емкость накопителя 128К х 22 бит, где К=1024бит

Узел портов диагностики осуществляет прием и выдачу информации о диагностики модуля и состоит из портов ввода-вывода, в которых хранится информация о работоспособности модуля.

В состав СМ1810 входит еще один модуль оперативной памяти МОЗ 4М, который отличается от МОЗ256 большей емкостью (до 4 Мбайт). Остальные параметры МОЗ 4М аналогичны МОЗ 256. МОЗ 4М состоит из пяти плат, которые устанавливаются в соответствующие места 1810.40 и 1810.41. Из них одна плата выполняет функции контороллера памяти, остальные четыре платы – функции накопителя. Платы накопителя полностью взаимозаменяемы и служад для наращивания накопителя блоками по 1 Мбайт до 4х. Минимальная емкость МОЗ 4М – 1 Мбайт.

Билет №3 вопрос №1

Общая характеристика микропроцессора. Функции и структурная схема МП.

Развитие технологии и схемотехники БИС привело к появлению в середине 70 – х годов нового типа интегрального электронного прибора, представляющего собой функционально законченное устройство обработки цифровой информации, управляемое хранимой в памяти программой и конструктивно выполненного в виде одного или нескольких БИС и СБИС. Такой прибор получил название микропроцессора, так как по своим логическим функциям и структуре напоминает упрощенный вариант процессора обычных ЭВМ, а именно дешифрация и выполнения команд микропрограммы, организация обращения к оперативной памяти, в нужных случаях инициирование работы каналов и периферийных устройств, восприятие и обработка запросов, поступающих из устройств машины и внешней среды. По выполняемым функциям микропроцессор является центральной частью объекта, управляющим взаимодействием ее устройств. Отличия от процессора можно сформулировать следующим образом: - меньшая разрядность обрабатываемых данных, меньшая точность вычислений;

упрощенная система арифметико-логических команд;

меньшими объемами прямоадресуемой памяти, выполнением операций адресной арифметики операций по обмену данными с внешними устройствами с помощью одного и того же АЛУ, надо отменить, что перспективные модели МП лишены этих отличий.

Структурная схема микропроцессора.

Основными особенностями организации современных микропроцессоров и микро-ЭВМ является:

А) Модульная структура, в которой модули являются функционально законченными устройствами

Б) Магистральная организация связей между модулями, при которой общие шины используются разными модулями

В) Микропрограммное управление

Г) Байтовая адресация памяти и побайтовая обработка данных

Д) Использование внутренних сверхоперативных регистров, см. Рис

В структуре можно выделить три основные части: центральный процессор, блок управления и постоянная память микропрограмм. Центральный процессор содержит АЛУ, сверхоперативную память в виде программно доступных общих регистров и функциональные регистры – командный, индексный, адресный, указатель стека и программный счетчик. АЛУ состоит из двоичного сумматора, сдвигающего регистра, двух регистров операндов и регистра результата. Схемы АЛУ выполняют команды сложения, вычитания, логическое И, ИЛИ, сложение по модулю 2 и сдвигов. Более сложные операции реализуются программно. Блок микропрограммного управления содержит дешифратор кода операции, схему формирования функций перехода к следующему адресу в микропрограмме и регистр адреса микрокоманды. Система прерывания в микропроцессорах достаточно проста и предназначена только для восприятия прерываний от внешних источников. Микропроцессоры имеют упрощенные схемы управления ПУ. В значительной степени управление этими устройствами реализуется посредством микропрограммного управления. Блок постоянной памяти микропрограмм, реализующих команды микропроцессора, обычно выполняется в виде отдельной БИС. В микропроцессорах используют косвенную, непосредственную, индексную адресации основной оперативной памяти и прямую адресацию общих регистров. Сверхоперативная память на общих регистрах, позволяет сократить количество обращений к внешней памяти и уменьшить необходимое количество выводов корпуса за счет сокращения формата команды. Из-за ограниченного числа выводов корпуса БИС не удается реализовать интерфейс микропроцессора с высокой пропускной способностью. Поэтому микропроцессоры имеют так называемый общий интерфейс, обслуживающий как внешнюю оперативную память, так и ПУ. Если не удается выделить для интерфейса достаточное количество выводов, применяют мультиплексирование шин (использование шин для разных целей на основе разделения времени). Для обеспечения совместной работы микропроцессора и внешнего оборудования шины интерфейса снабжаются буферными схемами, в которых используются электронные схемы с тремя состояниями и спец. линии управления выдачи данных.

Билет №4 вопрос №1

Классификация вычислительных устройств, аналоговые и цифровые вычислительные устройства.

Одним из важнейших путей повышения производительности вычислительных машин и систем, их эффективности и надежности является использование различных форм параллелизма в функционировании вычислительного оборудования. Поэтому в основу классификации ВС следует положить в первую очередь, реализуемую форму параллелизма.

По режиму работы ВС делятся на однопрограммные и мультипрограммные, случай, когда в памяти машины находится одна рабочая программа, которая, начав выполняться, завершается до конца, в противоположность этому принципу мультипрограммные ВС выполняют в один и тот же момент времени несколько программ или их частей.

Классификация систем по режиму обслуживания. Режим индивидуального пользования. Машина предоставляется полностью в распоряжение пользователя, по крайней мере, на время решения его задачи. Пользователь имеет непосредственный доступ к машине и имеет право осуществлять операции ввода вывода. Режим пакетной обработки. Пользователь не имеет непосредственного доступа к ВС, подготовленные им программы передаются персоналу, обслуживающему систему, и затем накапливаются во внешней памяти. Система по расписанию выполняет накопленный пакет программ. Режим коллективного пользования или многопользовательский режим. Форма обслуживания, при которой возможен доступ нескольких пользователей к вычислительным ресурсам мощной ВС. Каждому пользователю предоставлен терминал, с помощью которого он устанавливает связь с системой коллективного пользования. Системы коллективного использования с квантованным обслуживанием называются системами с разделением времени. По количеству процессоров (машин) в ВС, определяющему возможность параллельной обработки программ, Вс делятся на однопроцессорные (одномашинные), многомашинные и многопроцессорные. Многомашинные и многопроцессорные ВС создаются для повышения производительности и надежности вычислительных систем и комплексов. По особенностям территориального размещения и организации взаимодействия частей системы различают следующие типы ВС. Сосредоточенные ВС. В них весь комплекс оборудования, включая терминалы пользователя сосредоточен в одном месте и связь между отдельными машинами и устройствами обеспечивается, стандартными для системы внутренними интерфейсами. ВС с телеобработкой. В них отдельные источники и приемники информации, включая терминалы пользователя расположены на таком значительном расстоянии от вычислительных средств что связь их с центральными средствами ВС осуществляется по каналам связи. Вычислительные сети представляет собой территориально рассредоточенную многомашинную систему, состоящую из взаимодействующих ЭВМ, связанных между собой каналами передачи данных. ПО особенностям функционирования ВС во времени различают ВС работающие не в реальном масштабе времени и в реальном масштабе последние должны работать в темпе с процессом , информация о котором автоматически поступает в Вс и обрабатывается. Результаты должны получаться так быстро, чтобы можно было ими воспользоваться для воздействия на сам процесс.

Информацией называются сведения о тех или иных явлениях природы, событиях в общественной жизни и процессах в технических устройствах. Информация воплощенная и зафиксированная в некоторой материальной форме называется сообщением. Сообщения могут быть непрерывными и дискретными (цифровыми). Непрерывное (аналоговое) сообщение представляется некоторой физической величиной (напряжением, током) изменение которой во времени отображают протекание рассматриваемого процесса. Физическая величина, передающая непрерывное сообщение может в определенном интервале принимать любые значения и изменяться в произвольные моменты времени. Для дискретных сообщений характерно наличие фиксированного набора элементов, из которых в некоторые моменты времени формируются некоторые последовательности. Важным является не физическая природа элементов, а то обстоятельство что набор элементов конечен и поэтому любое дискретное сообщение конечной длины передает конечное число значений некоторой величины. Элементы сообщения – буквы (символы). Их набор – алфавит. ЭВМ или компьютеры являются преобразователями информации. В них исходные данные задачи преобразуются в результат ее решения. В соответствии с используемой формой представления информации машины делятся на два класса: непрерывного действия – аналоговые и дискретного действия – цифровые.

Билет №4 вопрос №2

Языки программирования высокого уровня для малых и микроЭВМ.

Ну тут мне и так понятно что говорить

Билет №6 вопрос №2

Архитектура и функции сетей ЭВМ

Вычислительной сетью ВСТ или сетью ЭВМ называется комплекс территориально рассредоточенных ЭВМ и терминальных устройств, связанных между собой каналами передачи данных. Целесообразность создания ВСТ обусловливается возможностью использования территориально рассредоточенными пользователями оборудования ЭВМ, программ и информационных баз, находящихся в различных вычислительных центрах сети, возможностью организации «распределенной обработки» данных путем привлечения вычислительных ресурсов нескольких вычислительных центров сети для решения особо сложных проблем. ВСт можно рассматривать как систему с распределенным по территории аппаратурными, программными и информационными ресурсами. Возможна реализация на основе ВСт распределенного (децентрализованного) банка данных, отдельные информационные базы которого создаются в местных вычислительных центрах сети. Другая возможность – это создание централизованного банка данных, к которому имеет доступ многочисленные, в том числе находящиеся на значительном расстоянии абоненты через свои терминалы местных систем коллективного пользования. Объединение в сеть ЭВМ нескольких вычислительных центров способствует увеличению надежности функционирования вычислительных средств, так как создается возможность резервирования одних вычислительных центров за счет технических ресурсов других узлов. Вычислительная сеть позволяет оперативно перераспределять нагрузку между ЭВМ сети и снижать пиковую нагрузку на вычислительные средства. С созданием ВСТ возникли предпосылки для специализации отдельных ВЦ сети на решении задач определенного класса, что по оценкам специалистов дает значительный эффект, так как позволяет сократить общие затраты высококвалифицированного труда на разработку моделей. Алгоритмов. И пакетов прикладных программ. Специализация отдельных ВЦ сети становится возможной, так как пользователь имеет доступ к уникальным программам и данным, а также уникальным вычислительным средствам любого ВЦ сети. В ВСТ с программно-несовместимыми ЭВМ теряет остроту проблема переноса программных средств с одних машин на другие, так как пользователь может воспользоваться именно той машиной, для которой нужная программа имеется. Обобщенная архитектура сети показана ниже:

Точка стандартн. стыка

Сеть

передачи данных

Сеть

передачи данных

ЭВМ

Основу ВСТ составляют крупные ЭВМ (вычислительные центры коллективного пользования ВЦКП), объединяемые сетью передачи данных. Эти ЭВМ называют главными вычислительными машинами, выполняют основные функции по выполнению программ пользователей, сбору, хранению, выдачи информации. Сеть передачи данных СПД, образуют каналы связи и узлы (центры) коммутации, в которых связные процессоры управляют выбором маршрутов передачи данных в сети, выполняют функции мультиплексоров, концентратора канала, осуществляют коммутацию каналов, сообщений или пакетов. ГВМ подсоединяются к сети непосредственно через точки стандартного стыка, если обеспечена совместимость по физическим сигналам и форматам информации между ГВМ и СП, или с помощью интерфейсных процессоров. Терминалы (Т) пользователей подключаются либо к ГВМ, либо непосредственно к СП, используются терминальные процессоры (концентраторы), часто называемые абонентскими пунктами, в этом случае отпадает необходимость выделения каждому терминалу отдельного канала связи. Абонентский пункт содержит устройство управления и связи (УУС). В качестве терминалов используют телетайпы, пишущие машинки. Дисплеи, и др. УВВ, а также их комбинации. Оборудование терминала может включать в себя микроЭВМ при этом терминал будет выполнять некоторые функции по вспомогательной обработке информации, что служит основанием считать его «интеллектуальным терминалом». Административное управление ВСт включает в себя планирование и учет работы отдельных машин сети, анализ и учет работы сети передачи данных, произведение измерений на сети и т.п. Эти функции возлагают на одну из ГВМ сети, которую называют административным комплексом. Отмеченные выше направления использования ВСТ поддерживаются реализуемыми в сетях специфическими режимами работы, позволяющими осуществлять:

Обмен сообщениями между терминалами

Удаленный ввод заданий с любого терминала через сеть на выполнение пакетной или диалоговой обработки на удаленной ЭВМ

Доступ к удаленным файлам и передача данных между ЭВМ сети.

Билет №7 вопрос №1

Операционные системы, функции, состав и компоненты.

Операционная система (ОС) – является неотъемлемой частью ЭВМ, обеспечивая управление всеми аппаратными компонентами и, позволяя отделить остальные классы программ от непосредственного взаимодействия с аппаратурой. ОС обеспечивает выполнение основных двух задач:

Поддержку работы всех программ, обеспечение их взаимодействия с аппаратурой.

Предоставление пользователям возможностей общего управления машиной.

В простейшем случае ОС содержит в себе следующие основные компоненты

Файловую систему

Драйверы внешних устройств

Процессор командного языка

Определение операционной системы

Операционная система в наибольшей степени определяет облик всей вычислительной системы в целом. Несмотря на это, пользователи, активно использующие вычислительную технику, зачастую испытывают затруднения при попытке дать определение операционной системе. Частично это связано с тем, что ОС выполняет две по существу мало связанные функции: обеспечение пользователю-программисту удобств посредством предоставления для него расширенной машины и повышение эффективности использования компьютера путем рационального управления его ресурсами.

ОС как расширенная машина

Использование большинства компьютеров на уровне машинного языка затруднительно, особенно это касается ввода-вывода. Например, для организации чтения блока данных с гибкого диска программист может использовать 16 различных команд, каждая из которых требует 13 параметров, таких как номер блока на диске, номер сектора на дорожке и т. п. Когда выполнение операции с диском завершается, контроллер возвращает 23 значения, отражающих наличие и типы ошибок, которые, очевидно, надо анализировать. Даже если не входить в курс реальных проблем программирования ввода-вывода, ясно, что среди программистов нашлось бы не много желающих непосредственно заниматься программированием этих операций. При работе с диском программисту-пользователю достаточно представлять его в виде некоторого набора файлов, каждый из которых имеет имя. Работа с файлом заключается в его открытии, выполнении чтения или записи, а затем в закрытии файла. Вопросы подобные таким, как следует ли при записи использовать усовершенствованную частотную модуляцию или в каком состоянии сейчас находится двигатель механизма перемещения считывающих головок, не должны волновать пользователя. Программа, которая скрывает от программиста все реалии аппаратуры и предоставляет возможность простого, удобного просмотра указанных файлов, чтения или записи - это, конечно, операционная система. Точно также, как ОС ограждает программистов от аппаратуры дискового накопителя и предоставляет ему простой файловый интерфейс, операционная система берет на себя все малоприятные дела, связанные с обработкой прерываний, управлением таймерами и оперативной памятью, а также другие низкоуровневые проблемы. В каждом случае та абстрактная, воображаемая машина, с которой, благодаря операционной системе, теперь может иметь дело пользователь, гораздо проще и удобнее в обращении, чем реальная аппаратура, лежащая в основе этой абстрактной машины.

С этой точки зрения функцией ОС является предоставление пользователю некоторой расширенной или виртуальной машины, которую легче программировать и с которой легче работать, чем непосредственно с аппаратурой, составляющей реальную машину.

ОС как система управления ресурсами

Идея о том, что ОС прежде всего система, обеспечивающая удобный интерфейс пользователям, соответствует рассмотрению сверху вниз. Другой взгляд, снизу вверх, дает представление об ОС как о некотором механизме, управляющем всеми частями сложной системы. Современные вычислительные системы состоят из процессоров, памяти, таймеров, дисков, накопителей на магнитных лентах, сетевых коммуникационной аппаратуры, принтеров и других устройств. В соответствии со вторым подходом функцией ОС является распределение процессоров, памяти, устройств и данных между процессами, конкурирующими за эти ресурсы. ОС должна управлять всеми ресурсами вычислительной машины таким образом, чтобы обеспечить максимальную эффективность ее функционирования. Критерием эффективности может быть, например, пропускная способность или реактивность системы. Управление ресурсами включает решение двух общих, не зависящих от типа ресурса задач:

планирование ресурса - то есть определение, кому, когда, а для делимых ресурсов и в каком количестве, необходимо выделить данный ресурс;

отслеживание состояния ресурса - то есть поддержание оперативной информации о том, занят или не занят ресурс, а для делимых ресурсов - какое количество ресурса уже распределено, а какое свободно.

Для решения этих общих задач управления ресурсами разные ОС используют различные алгоритмы, что в конечном счете и определяет их облик в целом, включая характеристики производительности, область применения и даже пользовательский интерфейс. Так, например, алгоритм управления процессором в значительной степени определяет, является ли ОС системой разделения времени, системой пакетной обработки или системой реального времени.

Билет №9 вопрос №1

Представление информации в форме с фиксированной и плавающей запятой. Прямая, обратная и дополнительная форма представления двоичных чисел.

Разряд двоичного числа представляется в ЭВМ некоторым техническим устройством, например триггером, двум различным состояниям которого приписывают значения 0 или 1. Набор соответствующего количества таких устройств служит для представления многоразрядного двоичного числа.

При представлении чисел с фиксированной запятой положение запятой фиксируется в определенном месте относительно разрядов числа. Обычно подразумевается, что запятая находится или перед старшим разрядом, или после младшего. В первом случае могут быть представлены числа, которые по модулю меньше 1, во втором – только целые числа.

-

Знак

2-1

2-2

…

…

2-31

0 1 2 3 4 5 6 ….. 31 - представление двоичных чисел с фиксированной запятой в виде 32 разрядных слов для случая закрепления запятой перед старшим разрядом.

-

Знак

230

…

…

…

20

0 1 2 3 4 5 6 ….. 31 - представление двоичных чисел с фиксированной запятой в виде 32 разрядных слов для случая закрепления запятой после младшего разряда.

Для кодирования знака числа используется «знаковый» разряд. 0 это +, 1 это -. Наибольшее положительное число, представимое в первой разрядной сетке, равно 0,1..1 = 1-2-31 , а наименьшее число 0,00…01 = 2-31 таким образом в разрядной сетке могут быть представлены числа в диапазоне от –(1-2-31) до -2-31 и от 2-31 до (1-2-31). Диапазон чисел, для второго случая:

1 х 231-1. При выполнении на машине вычислений необходимо чтобы все исходные и получающиеся в процессе вычислений данные не выходили за диапазон чисел, представимых в разрядной сетке. Для этого в программировании задачи данные берутся с соответствующими масштабными коэффициентами. Итог: Использование представления с фиксированной точкой позволяет упростить схемы машины, повысить ее быстродействие, но создает трудности при программировании, в машинах, предназначенных для решения широкого круга вычислительных задач, основным является представление с плавающей запятой, не требующее масштабирования данных, однако в таких машинах наряду с этой формой представления используется также и представление с фиксированной точкой для представления целых двоичных чисел и операций над ними, в частности операции над кодами адресов.

Представление числа с плавающей запятой в общем виде имеет вид:

X= spq ; q 1 где q мантисса числа Х, p – порядок, s – основание характеристики.

Обычно число s совпадает с основанием мантиссы q. Мантисса q – правильная дробь. Порядок p, который может быть положительным или отрицательным челым числом, определяет положение запятой в числе Х. Для двоичных чисел х = 2pq; q 1. Рассмотрим пример в котором слова имеют доины 32 двоичных разряда. Пусть число Х =2pq, изображается в машине двоичным словом а>0>в>0>в>1> … в>6>а>1>а>2>…. А>24> которому соответствует следующий формат данных :

|

А>0> |

В>0> |

В>1> |

… |

В>6> |

А>1> |

А>2> |

… |

А>24> |

Разряды в>0..>в>6 >используются для представления порядка> >при этом разряд в>0 >изображает знак порядка, а разряды в>1>.. в>6 >– модуль порядка, остальные разряды а>0 >.. а>24 >отводятся под изображение мантиссы, причем а>0 >– знак мантиссы а>1>.. а>24 >– модуль мантиссы. Двоичное число х= 2pq, называется нормализованным, если мантисса Q удовлетворяет следующему условию 1 q ½, т.е. двоичное число нормализовано если в старшем разряде мантиссы стоит 1. Под порядок отведено со знаком 7 разрядов то порядок может быть от –63 до +63 соответственно. Наибольшее и наименьшее нормализованное положительные числа в этой разрядной сетке соответственно равны: 263*0,111 … 1 = 263(1-2-24) и 2-63*0,1000..0=2-64. Следовательно с учетом знака q в этой разрядной сетке можно представить числа, лежащие в диапазоне от –263(1-224) до –2-64 и от +2-64 до +263(1-2-24), что значительно превышает диапазон чисел с фиксированной точкой, представимых в том же 32 х разрядном слове. При фиксированном количестве разрядов мантиссы любая величина, представляется в машине с наибольшей возможной точностью нормализованным числом. Если в процессе вычислений получается ненормализованное число, то машина с плавающей запятой автоматически нормализует его. Пусть r старших разрядов мантиссы равно 0. Тогда, нормализация заключатся в сдвиге мантиссы на r разрядов влево и уменьшении порядка на r единиц. При этом в младшие r разрядов мантиссы записывается 0. В последних моделях ЭВМ получило распространение представление чисел с плавающей запятой в системах счисления с основанием, равным целой степени числа 2 (S=2w), х = spq(1>q1/s). При этом порядок представляется двоичным целым числом, а мантисса q – числом, в котором группы по w двоичных разрядов изображают цифры мантиссы с основанием системы счисления s=2w. Использование для чисел с плавающей запятой недвоичного основания несколько уменьшает точность вычислений (при заданном количестве разрядом мантиссы), но позволяет увеличить диапазон представимых в машине чисел и ускорить выполнение некоторых операций, в частности нормализации, за счет того, что сдвиг может производиться на несколько разрядов сразу. В ЕС ЭВМ числа с плавающей запятой представляются в шестнадцатеричной системе счисления: х=16pq (1>q1/16) .

|

А>0> |

В>0> |

В>1> |

… |

В>6> |

Г>1> |

Г>2> |

… |

Г6 |

Модуль порядка p изображается целым шестиразрядным двоичным числом,. А мантисса q рассматривается как число, составленное из шестнадцатеричных цифр в виде:

6

q= Г>j>> >16-j (Г>j > = 0,1,2 …, F)

j=1

В случае с шестнадцатиричными числами с плавающей запятой число Х считается нормализованным, если старшая шестнадцатеричная цифра Г>1 >отлична от 0. В нормализованном числе три старшие двоичные цифры могут равняться 0. Диапазон представления нормализованных чисел: -1663(1-16-6) до –16-64 и от +16-64 до 1663(1-16-6). Для упрощения операций над порядками их сводят к действиям над целыми положительными числами, применяя представление чисел с плавающей запятой со смещенным порядком (ЕС ЭВМ). В случае чисел со смещенным порядком при записи числа в память к его порядку p прибавляется целое число – смещение N=2k, где k – число двоичных разрядов, используемых для модуля порядка. Смещенный порядок p>см>=p + N всегда положителен. Для его представления нужно такое же число разрядов как для p со знаком.

Если семи десятичных разрядов не хватает то в ЕС ЭВМ введен формат двойной длины, занимающий два машинных слова (двойная точность), не меняется количество разрядов для изображения порядка, и, следовательно, сохраняется диапазон представления чисел, а длина мантиссы увеличивается до 14 шестнадцатеричных разрядов.

В ЭВМ с целью упрощения арифметических операций применяют специальные коды для представления чисел. Например, упрощается определение знака результата операции, вычитание есть сложение кодов, облегчено определение переполнения разрядной сетки. Положительные числа представляются в прямом коде. Прямой код G>пр >двоичной дроби с (n-1) – разрядной мантиссой G=0,к>1,>к>2 …. >к >n-1> определяется как G>пр >= Gкогда G0 и 1+Gкогда G 0 Прямой код целого n – разрядного двоичного числа G = к>n-2>,k>n-3>, …k>1>,k>0 >имеет вид G>пр>=Gпри G0 и 2n-1+G при G0 Прямой код числа со знаком можно рассматривать как двоичное число без знака , которое определяется этими соотношениями. Операция вычитания (алгебраического сложения) сводится к операции простого арифметического сложения при помощи обратного и дополнительного кодов, используемых для представления отрицательных чисел в машине. Что бы представить двоичное отрицательное число в обратном коде нужно в знаковый разряд поставить 1, а во всех других разрядах заменить 1 нулями, а 0 – единицами. При этом отрицательная двоичная дробь G-= -0,k>1>,k>2>, …, k>n-1>в обратном коде примет вид

G->обр>= 1,r>1,>r>2>, …,r>n-1>> >а отрицательное двоичное число G= - k>n-2>,k>n-3>, …,k>1>,k>0 >соответственно G->обр>= 1,r>n-2,>r>n-3>, …,r>1>,r>0> где r>i=0 >если k>i=1 >и наоборот. При представлении отрицательного двоичного числа в дополнительном коде ставят 1 в разряд знака, а цифровую часть числа заменяют дополнением модуля числа до 2 или соответственно 2n, для дробей и целых чисел. Дополнительный код отрицательного числа G- определяется выражением G->доп>=2- G-, если G- - двоичная дробь, и G->доп >= 2n - G- если G- - целое двоичное число. Таким образом, дополнительный код числа может быть получен из обратного путем прибавления 1 к младшему разряду обратного кода.

Билет № 9 вопрос 2

Внешние ЗУ малых ЭВМ. Основные характеристики.

Для эффективной обработки данных необходимо обеспечить при минимальных затратах хранение больших объемов информации и быстрый доступ к ней. Эти требования противоречивы и при современном уровне технологии компромисс между емкостью, быстродействием памяти и затратами на нее достигается за счет создания иерархической структуры, включающий в себя сверхоперативный, основной, внешний, и архивный уровни. Информация для ЦП непосредственно доступна только из ЗУ сверхоперативного и основного уровней. Каждый последующий уровень в рамках одной ЭВМ характеризуется большей емкостью и меньшим быстродействием ЗУ. Внешний и архивный уровни образуют систему внешней памяти; в ее состав входят разнородные ВЗУ, контроллеры ВЗУ, а также носители информации и хранилища для них.

Классификация и основные характеристики ВЗУ.

ВЗУ, или накопители являются основными компонентами системы внешней памяти. Информация в них располагается в виде блоков, которые становятся доступными для обработки в ЦП в результате выполнения операций ввода, т.е. загрузки из внешней памяти в оперативную. Передача блоков из оперативной памяти во внешнюю осуществляется операцией вывода. В качестве ВЗУ используются устройства, различающиеся типом носителя, способом регистрации и характером использования информации, способом доступа и т.д.

По типу носителя различают ВЗУ с подвижным и неподвижным носителем. При современной технологии наиболее часто реализуют размещение информации на поверхности некоторого тела, называемого носителем. Если поиск, запись и считывание информации сопровождается механическим перемещением носителя, то такие ВЗУ называют накопителями с подвижным носителем, среди которых наиболее распространены накопители на магнитных дисках НМД, оптических дисках НОД, магнитных лентах НМЛ. Носитель может быть гибким и жестким. Если при поиске, записи или считывании механического перемещения носителя не происходит, то ВЗУ называют накопителем с неподвижным носителем; примером может служить накопитель на основе цилиндрических магнитных доменах ЦМД. Реже в ВЗУ используют объемную запись – полупроводниковые ЗУ, приборы с зарядовой записью.

По способу регистрации различают ВЗУ с магнитной и оптической (магнитооптической) записью; По характеру использования информации – постоянные ВЗУ (только чтение), ВЗУ с однократной записью, и с многократной записью (множество циклов чтения \ записи). По способу доступа к информации все ВЗУ делят на накопители с последовательным и прямым доступом. Расположение блоков на поверхности носителя можно представить в виде линейного и двумерного массива. В первом случае для нахождения требуемого блока последовательно просматриваются все блоки. ВЗУ, реализующие такой просмотр называют накопителями с последовательным доступом; примером может служить накопитель на магнитной ленте, максимальное время поиска соответствует полному времени перемещения ленты от начала до конца и достигает 1-2 минут. При расположении блоков информации в виде двумерного массива можно организовать независимый поиск по каждому направлению. Пусть задан номер строки (или дорожки) , где расположен искомый блок IJ; тогда время поиска опеределяется временем просмотра блоков только по этой дорожке. ВЗУ, реализующие такой просмотр, называют накопителями с прямым доступом: поиск в направлении Y в них производится за счет перключения или перемещения органов считывания (головок), а просмотр в направлении X – за счет перемещения носителя или продвижения информации по структуре (ЦМД). В ВЗУ с прямым доступом один и тот же блок доступен для записи или считывания через постоянные промежутки времени, определяемые в случае с НМД временем оборота; поэтому такой доступ называют циклическим.

ВЗУ принято характеризовать следующими параметрами:

емкостью памяти; при этом если носитель информации является сменным, то под емкостью ВЗУ понимают обьем одного тома, который доступен ВС без замены носителя.

пропускной способностью, или скоростью записи считывания; блок на носителе можно рассматривать в виде последовательности бит, расположенных вдоль направления движения носителя. Длительность считывания и записи блока, таким образом, определяется временем, затрачиваемым на прохождение блока под головкой, а пропускная способность определяется отношением объема блока ко времени его прохождения под головкой;

временем доступа, т.е. интервалом времени от момента запроса до момента выдачи блока; этот интервал времени не постоянен и зависит от множества факторов – скорости перемещения носителя, скорости перемещения головки, прямого или последовательного доступа, расстояния от текущего положения головки до запрашиваемого блока на носителе и т.п. В случае подвижного носителя и прямого доступа этот интервал складывается из времени поиска дорожки и времени ожидания (пока блок не появится под головкой). Время поиска дорожки характеризуется минимальным (дорожка – след. дорожка), максимальным (прот. дорожки), и средним значениями. Время ожидания характеризуют средним значением, которое соответствует половине длительности оборота носителя. Данные одного пользователя обычно размещаются на соседних дорожках, что уменьшает время поиска, однако при коллективном использовании ВЗУ в мультипрограммном режиме эта “локальность” данных нарушается и время поиска увеличивается.

В системах внешней памяти преобладающее место занимают накопители с прямым доступом, так как они обеспечивают приемлемое время поиска (несколько миллисекунд) высокую пропускных способность (от 1Мб/с и выше), большую емкость. ВЗУ с последовательным доступом отличает низкая стоимость хранения информации, но по всем другим характеристикам они уступают накопителям с прямым доступом, поэтому НМЛ используют для сохранения информации на случай аварийного разрушения т.е они служат в качестве резервных.

Одной из важнейших характеристик ВЗУ, обычно скрытых от пользователя, является информационная плотность записи. Под плотностью записи з понимают число бит информации, записанных на единице поверхности носителя, - это поверхностная плотность. Различают так же продольную плотность l, бит/мм, т.е. число бит на единице длины носителя вдоль вектора скорости его перемещения, и поперечную плотность q, бит/мм, т.е. число бит на единице длины носителя в направлении перпендикулярном вектору скорости: з = l q , Плотность записи определяет геометрические размеры накопителя, параметры его быстродействия, а также обьем памяти. В свою очередь, информационная плотность записи определяется принципами регистрации информации на носителе, материалами , конструктивными особенностямии технологией изготовления как носителя так, и средств записи считывания.

Билет №12 вопрос №1

Внутреннее построение микропроцессора

(Начало вопроса см. Билет № 3 вопрос №1)

Для микроЭВМ и микропроцессоров типичной является такая организация, при которой их внутренние регистры используются в различных целях. Система связей у этих регистров как правило, централизованная (магистральная), обеспечивающая возможность разнообразных межрегистровых пересылок, в том числе передач в АЛУ и из АЛУ. В связи с этим часто собственные регистры АЛУ (регистры, используемые только для выполнения арифметических и логических операций) в микропроцессорах отсутствуют. Это дает повод рассматривать АЛУ микропроцессоров как комбинационную схему, выполняющую арифметические и логические операции над операндами, находящихся в регистрах микропроцессора. Результат операции засылается в некоторый регистр микропроцессора. Подобные АЛУ входят в состав микропроцессоров К580, К1810 и др.

В процессе выполнения операций комбинационное АЛУ взаимодействует с регистрами микропроцессора, являющиеся обычно источниками и приемниками операндов для такого АЛУ, при этом как правило один и тот же регистр может рассматриваться и как источник и как приемник информации. Для реализации такой возможности необходимо осуществлять временное запоминание промежуточных результатов на отдельных регистрах. С этой целью используют либо регистры для кратковременного запоминания операндов, либо регистры для кратковременного запоминания результата. На рисунке показана схема включения комбинационного АЛУ в контур с регистрами микропроцессора для выполнения арифметических операций. В приведенной схеме имеются регистры процессора РгП (регистр признака результата), РгАкк (Аккумулятор), Рг1, … Ргm, которые могут использоваться произвольным образом, и регистры временного хранения операндов РгА и РгБ, в которые при выполнении арифметических и логических операций загружаются операнды. Пусть , например, выполняется операция сложения двух чисел, находящихся в регистрах процессора Ргi и Ргj, с засылкой результата в Ргj . Эта операция потребует сначала пересылки содержимого Ргi и Ргj в РгА и РгБ , а затем загрузки результата , сформированного АЛУ, в Ргj. Отсутствие РгА привело бы к возникновению порочной петли, так как изменения состояний РгJ влекли бы за собой новые изменения состояний Ргj.

АЛУ , используемые в рассматриваемых схемах , представляют собой комбинационные схемы, настраиваемые сигналами микроопераций на различные преобразования. Это может быть двоичное или двоично – десятичное сложение, вычитание, логическое умножение и т.д. При написании микропрограмм операций в АЛУ в микрокомандах задаются микрооперации , определяющие выбор источников операндов для АЛУ , настраивающие АЛУ на выполнение различных преобразований и указывающие место занесения результата, сформированного АЛУ.

Рассматриваемая схема является фрагментами микропроцессора, в котором те же самые регистры используются для других целей что ведет к усложнению программ.

Билет №13 вопрос №1

Логические вентили ТТЛ. (Ключи)

Схема базового элемента ТТЛ показана на рисунке ниже. Основной особенностью элементов ТТЛ является использование многоэмиттерных транзисторов, специфичных для интегрального исполнения логических элементов. Схема соответствует элементу ТТЛ с повышенной нагрузочной способностью (1ЛБ556), входящему в состав широко применяемой в ЭВМ системы элементов – «серии 155» . В этой серии логический 0 представляется сигналом низкого уровня u>0>0,4 В, а логическая 1 - сигналом высокого уровня u>1>2,4 В. Если на все входы многоэмиттерного транзистора МТ (рис.) поданы положительные сигналы высокого уровня u>1>2,4 В (сигналы 1), то ток через его базовый резистор R>1> течёт в базу транзистора Т>1>, а затем усиленный ток из эмиттера Т>1 >поступает в базу выходного инвертирующего транзистора Т>4>, открывая его. При этом транзистор Т>2> оказывается закрытым. Транзистор Т>3> также закрывается. На выходе элемента возникает сигнал 0 (приблизительно равный потенциалу эмиттера транзистора Т>4>). Если на одном из входов многоэмиттерного транзистора МТ появляется сигнал низкого уровня u>0>0,4 В (сигнал 0), то транзистор Т>1>закрывается, что приводит к запиранию транзистора Т>4>. При этом транзистор Т>2> работает как эмиттерный повторитель, на базу которого через резистор R>2> подаётся высокий уровень от шины питания +Е>к>, и транзистор Т>3> открывается. На выходе элемента И возникает сигнал высокого уровня u>1>2,4 В (сигнал логической 1). Транзистор Т>3> выполняет функции коллекторного резистора с переменным сопротивлением для транзистора Т>4>. Резистор R>3> имеет небольшое сопротивление и служит для ограничения выходного тока. Активное переключение транзисторов Т>3> и Т>4 >позволяет элементу ТТЛ работать на большое число нагрузок. Элемент ТТЛ реализует функцию И – НЕ для сигналов логической 1, представленных высоким уровнем. Логическую функцию такого элемента записывают как И – НЕ. Элемент ТТЛ (рис.) имеет специальные выводы К и Э для расширения группы входов ("входной логики") по ИЛИ. При подключении к точкам К и Э основного элемента ТТЛ точек К` и Э` вспомогательного элемента расширителя (1ЛП551), изображённого на рисунке, логическая функция, выполняемая такой схемой, записывается как 4И – 2ИЛИ – НЕ (рис.). Нагрузочная способность схем ТТЛ допускает подключение к выходу элемента до десяти логических элементов. Время задержки сигнала в элементе ТТЛ следует относить к интегральным логическим элементам среднего быстродействия.

Билет № 14 вопрос №2

Для не резервированных ЭВМ (не содержащих дублированных устройств) последовательность вычислений следующая. Сначала необходимо определить интенсивности отказов устройств

_____

каждого типа >0>>i>>,>i= 1, N >_ >, где N - число устройств, входящих в состав ЭВМ. Величины >0>>i >определяются по формуле __

__ >0>>i >=1/ Т>0>>i>, __

где Т>0>>i> – среднее время наработки на отказ устройства i – го типа. Значения Т>0>>i> берутся из эксплуатационной документации на соответствующие устройства ЭВМ либо вычисляются по результатам наблюдений за работой машины. Интенсивность отказов ЭВМ в целом (суммарная интенсивность отказов ЭВМ) вычисляется по формуле

>N>

>0>= >0>>i>k>i> ,

i=1

где k>i>- коэффициент, определяющий , насколько интенсивно используется устройство i - го типа при совместной работе с другими устройствами в составе ЭВМ. Например:

Тип устройства: Коэффициент использования:

Печатающие устройства … 0,1

ВЗУ 0,9

Графические устройства 0,05

УВВ на ЭЛТ 0,1

При отсутствии устройства какого – либо типа k>i >принимается равным 0. Зная >0> , вычисляем среднее значение наработки на отказ машины: ___

Т>о>=1/>0> __

Среднее время восстановления после отказа работоспособности ЭВМ Т >в.о >вычисляется по формуле :

___ __ N __ __ ___

Т >в.о>= Т>о> (k>i >T>в.о.>>i>)/T>oi >где T>в.о.>>i> – среднее время восстановления i – го устройства

i=1 __

после отказа . Интенсивность потока восстановлений >в.о> = 1/ Т >в.о>.

Билет №1 вопрос №1

Понятие о системах элементов. Состав системы элементов. Функциональные наборы логических элементов.

Системой или (комплексом , серией) логических элементов ЭВМ называется предназначенный для построения цифровых устройств, функционально полный набор логических элементов, объединяемый общими электрическими, конструктивными и технологическими параметрами, использующий одинаковый способ представления информации и одинаковый тип межэлементных связей. Система элементов чаще всего избыточна по своему функциональному составу, что позволяет строить схемы, более экономичные по количеству элементов. (Состав) Системы элементов содержат элементы для выполнения логических операций,а также элементы для усиления и, восстановления и формирования стандартной формы сигналов. В настоящее время применяют в основном системы логических элементов с потенциальным способом представления информации (потенциальные системы логических элементов). Элементы представляют собой микро миниатюризированные электронные схемы, сформированные в кристалле кремния посредством специальных технологических процессов. В большинстве современных серий в качестве типовых используются элементы выполняющие логические операции, такие как И-НЕ,ИЛИ-НЕ,И-ИЛИ,И-ИЛИ-НЕ и др. триггеры и, кроме того, сложные функциональные элементы, представляющие собой узлы ЭВМ. Основными параметрами системы логических элементов являются: питающие напряжения и сигналы для представления логического нуля и единицы, коэффициенты объединения по входам И и ИЛИ, нагрузочная способность (коэффициент разветвления по выходам) помехоустойчивость, рассеиваемая мощность , быстродействие. Для логических элементов указывается полярность и уровни входного и выходного сигналов. В дальнейшем будем считать 0 – низкий уровень, 1 высокий уровень если не оговорено обратное. Коэффициент объединения по входу определяет максимально возможное число входов логического элемента. Увеличение числа входов связано с усложнением схемы элементов и привод к ухудшению других параметров элемента. Коэффициент разветвления по выходу показывает, на сколько входов логических элементов может быть одновременно нагружен выход данного логического элемента. Помехоустойчивость. Помехой называется нежелательное электрическое воздействие (напр. Пульсации напряжения питания и т.д.) на логический элемент, которое может привести к искажению преобразуемых и хранимых данных. Помехоустойчивость есть способность элемента правильно функционировать при наличии помех, она определяется максимально допустимым напряжением помехи, при котором не происходит сбоя в его работе. Быстродействие логических элементов является одним из важнейших параметров и характеризуется средним временем задержки распространения сигнала t >з.ср.>= (t>з.1 >+ t>з.2.>)/2 , где t>з.1 >и t>з.2 >– задержка выходного сигнала относительно фронта и спада входного сигнала. Большинство систем интегральной логики принадлежит к потенциальной системе. Их принято классифицировать по типу компонентов, на которых реализуется логические функции. Основные, часто употребляемые типы интегральных элементов: потенциальные элементы транзисторно – транзисторной логики (ТТЛ), потенциальные элементы транзисторной логики с эмиттерными связями (ЭСЛ) и элементы на МОП – транзисторах.

Билет №10 вопрос №2

Многомашинные и микропроцессорные ВС. Принципы организации. Сравнительный анализ.

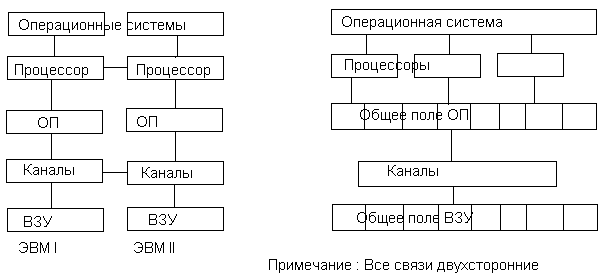

ВТ в своем развитии по пути повышения быстродействия ЭВМ приблизилась к физическим пределам. Время переключения электронных схем достигло долей наносекунды, а скорость распространения сигналов в линиях, связывающие элементы и узлы машины ограничена значением 30 см/нс (скорость света). Поэтому дальнейшее уменьшение времени переключения электронных схем не позволит существенно повысить производительность ЭВМ. В этих условиях требования практики по дальнейшему повышению быстродействия ЭВМ могут быть удовлетворены только путем распространения принципа параллелизма на сами устройства обработки информации и создания многомашинных и многопроцессорных вычислительных систем. Такие системы позволяют производить распараллеливание во времени выполнения программы или параллельное выполнение нескольких программ. Работа в системах обработки данных и управления, особенно при работе в режиме реального времени требует высокой надежности, и готовности что решается на основе принципа избыточности, и ориентирует на построение такого рода комплексов. Различие и принципы организации многомашинной и многопроцессорной ВС поясняет рисунок данный ниже:

М

ногомашинная

(ММС) ВС содержит несколько ЭВМ, каждая

их которых имеет свою ОП и работает под

управлением своей операционной системы,

а так же средства обмена информации

между машинами. Реализация обмена

информацией происходит в конечном итоге

путем взаимодействия операционных

систем разных машин между собой. Это

ухудшает динамические характеристики

процессов межмашинного обмена данными.

Их применение позволяет повысить

надежность вычислительных установок.

При отказе в одной машине обработку

данных может продолжить другая машина.

Однако можно заметить, что при этом

оборудование комплекса недостаточно

эффективно используется для этой цели.

Достаточно в этой системе в каждой из

машин выйти из строя хотя бы по одному

устройству как вся система становится

неработоспособной. Этих недостатков

лишены многопроцессорные системы (МПС).

В них процессоры обретают статус рядовых

агрегатов вычислительной системы,

которые подобно другим агрегатам, таким

как модули памяти, каналы, ПУ, включаются

в состав системы в нужном количестве.

Вычислительная система называется

многопроцессорной, если она содержит

несколько процессоров, работающей с

общей ОП и управляется одной общей

операционной системой. Часто в МПС

организуется общее поле внешней памяти.

Под общим полем подразумевается

равнодоступность устройства. Для памяти

это означает что все модули памяти,

доступны всем процессорам и каналам

ввода вывода (или всем ПУ в случае наличия

общего интерфейса). В МПС по сравнению

с ММС достигается более быстрый обмен

информацией между процессорами через

общую ОП, и поэтому может быть получена

более высокая производительность, более

быстрая реакция на ситуации, возникающими

внутри системы и ее внешней среде, и

более высокую надежности и живучесть,

так как система сохраняет работоспособность

пока работоспособны хотя бы по одному

модулю каждого типа устройства. Однако

построение ММС из стандартно выпускаемых

ЭВМ с их стандартными операционными

системами, значительно проще, чем

построение МПС, требующих преодоления

определенных трудностей, возникающих

при реализации общего поля ОП, и главное

трудоемкой разработки специальной

операционной системы. В настоящее время

данная проблема решена путем создания

плат построенных на чипсете фирмы INTEL

PR440FX второе название Providence

и операционной системы Windows

NT ( New Technology) .При их создании возникает

множество проблем , среди которых

осуществление быстродействующих

экономичных по аппаратурным затратам

межмодульных связей , снижение потерь

производительности из-за конфликтов

при попытке нескольких процессоров

использовать один и тот же ресурс. МПС

и ММС сооздаваемые путем комплесирования

оборудования нескольких серийных ЭВМ

, часто называют вычислительными

комплексами ВК, обычно управляющей

каким – либо обьектом. На основе

многопроцессорности и модульного

принципа построения других устройств

системы возможно создание отказоустойчивых

систем или так назвыаемых

систем повышенной живучести. ММС и МПС

могут быть однородными и неоднородными.

Однородные системы содержат однотипные

ЭВМ или процессоры. Неоднородные ММС

состоят из ЭВМ различного типа а в

неоднородных МПС используются различные

специализированнные процессоры, например

рпоцессоры для операций над числами с

плавающей точкой , для обработки

десятичных чисел, процессор реализующий

функции операционной системы и др. МПС

и ММС могут иметь одноуровневую и

иерархическую структуру. В первом случае

машины (процессоры) системы образуют

один общий уровень обработки данных ,

а во втором система содержит отдельные

машины (процессоры) для выполнения

различных уровней обработки информации

. Обычно менее мощная машина (саттелит)

берет на себя ввод информации с различных

терминалов и ее предварительныю обработку

, разгружая от этих сравнительно простых

операций , основную, более мощную ЭВМ,

чем достигается увеличение общей

пропускной способности комплекса.

Обычно саттелит – микроЭВМ. Важной

структурной особенностью ВС является

способ организации связи между

устройствами (модулями) системы. Он

непосредственно влият на быстроту

обмена информацией между модулями

системы, а следовательно и на

производительность, быстроту реакции

на поступающие запросы , приспособленность

к изменению конфигурации, и , наконец,

на размеры аппаратурных затрат на

осуществление межмодульных связей. В

частности от организации межмодульных

связей зависит частота возникновения

конфликтов при обращении процессора к

одним и тем же ресурсам.и потери

производительности из-за конфликтов.

Используются следующие способы

организации межмодульных связей:

Многоуровневые связи, соответствующие иерархии интерфейсов ЭВМ

Общая шина

Регулярные связи между модулями

Коммутатор межмодульных связей

Принципы организации МПС и ММС существенно отличаются в зависимости от их предназначения . Поэтому целесообразно различать :

ВС, ориентированные на повышение надежности и живучести

ВС, ориентированные на достижение сверхвысокой производительности.

Билет №14 вопрос №1

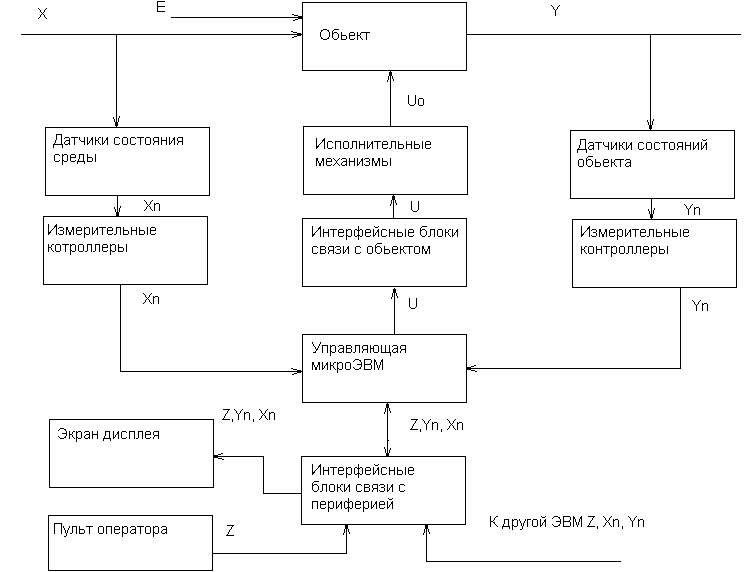

Управляющие микро-ЭВМ и промышленные контроллеры

Под управлением понимают целенаправленное воздействие на объект, в результате которого он переходит в требуемое состояние. Объектом будем называть ту часть окружающей среды, на которую можно воздействовать с определенной целью. Состояние Y объекта можно описать параметрами, характеризующими его в каждый момент времени. Объект управления существует не просто сам по себе, а в окружающей его среде, которая постоянно воздействует на его состояние. Эти воздействия окружающей среды можно разделить на три группы 1) Объективно существующие и наблюдаемые (вход объекта Х). 2) управляющие воздействия, с помощью которых происходит управление объектом (управляющий вход U>0>) 3) возмущения Е (не измеряемые параметры среды, и всякого рода случайные изменения объекта). Управляющие воздействия обьекта U>0>> >подаются на объект с определенной целью. Цель управления – это требуемое состояние или последовательность состояний объекта во времени. Если цель сформулирована иначе, то ее надо перевести на язык состояний объекта управления. Использование микроЭВМ в системах управления имеет ряд особенностей по сравнении с использованием ее в качестве универсальной микроЭВМ. Универсальные микроЭВМ, предназначенные для научно технических расчетов или обработки информации, ориентированны в первую очередь на взаимодействие с пользователем. Задача таких ЭВМ обрабатывать данные по запросу пользователя. Поэтому в универсальной микроЭВМ через блоки сопряжения подключаются блоки ввода вывода информации. (примеры) Основная же задача управляющей ЭВМ состоит в том, чтобы на основании информации, получаемой от датчиков, вычислить и передать на исполнительные механизмы управляющие воздействия. Как правило, управляющие микроЭВМ встраиваются в оборудование и настраиваются на конкретную область применения. Поэтому работают они уже по готовым программам, которые хранятся в ПЗУ. В состав управляющей микро ЭВМ обязательно входят контроллеры для приема данных от датчиков состояния среды и объекта, а также для передачи управляющих воздействий на исполнительные механизмы. В этих блоках данные преобразуются к форме, которую понимает микроЭВМ. МикроЭВМ работает сданными в цифровом виде, датчики выдают ее в аналоговом, следовательно, требуется двустороннее цифроаналоговое преобразование, при котором каждому измеренному значению соответствует определенный цифровой код, с которым и работает микроЭВМ. Отличительной особенностью работы управляющих микроЭВМ является выполнение ими всех операций в реальном масштабе времени. Термин реальное время используют в тех случаях, когда требуется оперативно реагировать на входные сигналы, причем задержка реакций должна быть конечной и не превышать определенного значения. В различных приложениях этот термин определяется по-разному. В управляющих микроЭВМ вычисление управляющих воздействий за время, больше требуемого, приравнивается к получению неправильного результата, так как ЭВМ должна оперативно управлять объектом. При работе микроЭВМ в составе системы управления можно решать следующие задачи:

Принимать информацию от датчиков о состоянии окружающей среды объекта.

Расчитывать в реальном времени управляющие воздействия и передавать их на исполнительные механизмы

Отображать информацию о текущем состоянии системы оператору на дисплее

Принимать и обрабатывать команды оператора по изменению условий процесса управления.

Передавать и принимать информацию от других микроЭВМ. Особенностью управляющих микроЭВМ можно считать повышенное требование к надежности программного обеспечения, так как отказ может привести к серьезным последствиям в работе реальных устройств.

Рассмотрим структуру микропроцессорной системы управления. Устройство управления в данной системе включает в себя управляющую микроЭВМ, но в общем случае может содержать вычислительную систему. Алгоритмы управления реализованы в виде программ, хранящихся в памяти ЭВМ. Интерфейсные блоки предназначены для связи с объектом управления (главными и вспомогательными приводами и электроавтоматикой станка) и периферийным оборудованием; пульт оператора для выдачи команд в микроЭВМ на специальном языке. Измерительные контроллеры преобразуют и выдают в микроЭВМ в цифровом виде показания датчиков о состоянии объекта и среды. В состав интерфейсных блоков связи и контроллеров могут входить микропроцессоры, в этом случае процессор освобождается от рутинных функций по вводу/выводу и предварительной обработки информации.

При построении систем управления сложными объектами такой объект разбивается на части и строится система управления аналогичная этой, затем соединяется через центральную ЭВМ.

Д

ля

управления внешними устройствами

приходится выполнять на микроЭВМ сложную

последовательность действий, связанных

с проверкой различных условий и передачей

данных. Задачи передачи данных требуют

быстрого выполнения логических операций

в многократно выполняющихся алгоритмах,

не меняющихся в процессе работы. Наиболее

эффективно в качестве аппаратной

реализации таких алгоритмов использовать

микроконтроллеры – спец. управляющие

микро ЭВМ, которые работают в реальном

масштабе времени по некоторым фиксированным

рабочим программам, размешенных в ПЗУ.

Использование микроконтроллеров для

управления внешними устройствами

разгружает центральный процессор

микроЭВМ от излишне детального управления.

Наиболее распространены микроконтроллеры

трех типов.1) Ориентированные на реализацию

алгоритмов логического типа и

предназначенные для замены релейных и

логических схем электроавтоматики

командоппаратов. 2) ориентированные на

реализацию алгоритмов автоматического

регулирования аналоговых и аналого-дискретных

технологических процессов и предназначенные

для замены различных аналоговых и

цифровых регуляторов. 3) Ориентированные

на реализацию спец. алгоритмов управления

и предназнач. для управления игровыми

автоматами, светофорами и т.д.

Билет № 14 вопрос №2

Для не резервированных ЭВМ (не содержащих дублированных устройств) последовательность вычислений следующая. Сначала необходимо определить интенсивности отказов устройств

_____

каждого типа >0>>i>>,>i= 1, N >_ >, где N - число устройств, входящих в состав ЭВМ. Величины >0>>i >определяются по формуле __

__ >0>>i >=1/ Т>0>>i>, __

где Т>0>>i> – среднее время наработки на отказ устройства i – го типа. Значения Т>0>>i> берутся из эксплуатационной документации на соответствующие устройства ЭВМ либо вычисляются по результатам наблюдений за работой машины. Интенсивность отказов ЭВМ в целом (суммарная интенсивность отказов ЭВМ) вычисляется по формуле

>N>

>0>= >0>>i>k>i> ,

i=1

где k>i>- коэффициент, определяющий , насколько интенсивно используется устройство i - го типа при совместной работе с другими устройствами в составе ЭВМ. Например:

Тип устройства: Коэффициент использования:

Печатающие устройства … 0,1

ВЗУ 0,9

Графические устройства 0,05

УВВ на ЭЛТ 0,1

При отсутствии устройства, какого – либо типа k>i >принимается равным 0. Зная >0> , вычисляем среднее значение наработки на отказ машины: ___

Т>о>=1/>0> __

Среднее время восстановления после отказа работоспособности ЭВМ Т >в.о >вычисляется по формуле:

___ __ N __ __ ___

Т >в.о>= Т>о> (k>i >T>в.о.>>i>)/T>oi >где T>в.о.>>i> – среднее время восстановления i – го устройства

i=1 __

после отказа . Интенсивность потока восстановлений >в.о> = 1/ Т >в.о>.

Билет №15 вопрос №2

Команды микропроцессора

Выполнение команды состоит из отдельных машинных операций. В данном случае под операцией понимают преобразование информации, выполняемое машиной под воздействием одной команды. Содержанием машинной операции может быть запоминание, передача, арифметическое и логическое преобразование некоторых машинных слов (операндов). Команда представляет собой код, содержащий информацию, необходимую для управления машинной операцией. Команда должна указывать: а) операцию, подлежащую выполнению; б) операнды, над которыми выполняется операция; в) адрес, куда должен быть помещен результат операции; г) следующую команду (или откуда она должна быть взята). Команда состоит из операционной и адресной частей. Операционная часть содержит КОП, т.е. некоторое число, которое задает вид операции (сложение, умножение, передача и т.д.). Адресная часть команды содержит информацию об адресах операндов и результатах операции, а в некоторых случаях информацию об адресе следующей команды. Количество двоичных разрядов, отведенных под код операции, выбирается таким, чтобы можно было представить все выполняемые операции. Если ЭВМ выполняет М различных операции, то число разрядов в КОП должно быть не меньше log>2>M. Для упрощения аппаратуры и упрощения быстродействия ЭВМ длина формата команды должна быть согласована с выбираемой из требований точности вычислений длиной обрабатываемых машиной слов (операндов) с тем, чтобы для операндов и команд можно было эффективно использовать одни и те же память и аппаратные средства обработки информации. Это согласование достигается укорачиванием формата команды путём применения подразумеваемой, а также относительной и косвенной адресации и некоторых других приёмов. Обычно код команды имеет формат машинного слова или полуслова, реже полутора или двух слов. В некоторых машинах для представления команд используется несколько различных форматов. На рисунке схематично показаны различные структуры кода команды. В самом общем случае адресная часть должна содержать четыре адреса или адресных кода (рис.) для указания ячеек, содержащих два операнда, участвующих в операции, ячейки, в которую помещается результат операции, и ячейки, содержащей следующую команду. Такой порядок выборки команд называется принудительным. Он использовался в некоторых первых моделях ЭВМ. Четырехадресные команды в настоящее время не применяются. Можно установить, как это принято для большинства машин, что после выполнения данной команды, расположенной в ячейке k, выполняется команда из следующей по порядку (k+1)-й ячейки. Такой порядок выборки команд называется естественным. Он нарушается только специальными командами. В таком случае теряется необходимость указывать в команде адрес следующей команды. В трёхадресной команде (рис.) первый и второй адреса указывают ячейки памяти, в которых расположены операнды, а третий адрес определяет ячейку, в которую помещается результат операции. Следует отметить, что очень часто в качестве операндов используются результаты предыдущих операций, хранимые в триггерных регистрах машины. В этом случае выполняемая операция приобретает характер одно- или двухадресный, а трёхадресный формат используется неэффективно. По указанным причинам в современных ЭВМ применяют, как правило, одно- и двухадресные команды и их модификации.

|

Код операции |

Первый адрес А >1 > |

Второй адрес А>2> |

Третий адрес А>3> |

Четвёртый адрес А>4> |

|

Код операции |

Первый адрес А >1> |

Второй адрес А>2> |

Третий адрес А>3> |

|

Код операции |

Первый адрес А >1> |

Второй адрес А>2> |

|

Код операции |

Первый адрес А |

По характеру выполняемых операций различают следующие основные группы команд: а)команды арифметических операций для чисел с фиксированной и плавающей запятой; б)команды десятичной арифметики; в) команды логических (поразрядных) операций (И,ИЛИ и др.); г) команды передачи кодов; д) команды операций ввода-вывода; е) команды управления порядком исполнения команд (команды передачи управления) и некоторые другие.

Билет № 16 вопрос №1

Принципы построения семейства микроЭВМ СМ 1800

Семейство микроЭВМ СМ 1800 включает в себя следующие типы микроЭВМ: СМ1800, СМ1804, СМ1810, СМ1814. МикроЭВМ СМ1800 и СМ1804 построены на базе 8-разрядного микропроцессора КР580ИК80А. МикроЭВМ СМ1810 и СМ1814 построены на база 16-разрядного микропроцессора К1810ВМ86. В основу построения семейства микроЭВМ СМ1800 положен модульный принцип, суть которого состоит в том, что машины выполняются из функционально законченных устройств (модулей) в виде одной или двух печатных плат, объединенных интерфейсом И41. Универсальность интерфейса И41 и модульность ЭВМ позволяют комплексировать многопроцессорные системы на уровне печатных плат, что обеспечивает высокую гибкость при создании управляющих и вычислительных комплексов, а так же открытость микроЭВМ как системы. Открытость микроЭВМ создает условия для расширения номенклатуры модулей и развития СМ1800. Так при создании микроЭВМ СМ1810 использованы новая элементная база и конструктивная реализация. Основу элементной базы семейства микроЭВМ СМ1800 составляют микропроцессорные наборы КР580 и К1810. Микропроцессорный набор К1810 представляет собой третье поколение микропроцессоров. Он расширяется арифметическим сопроцессором, аналогичным микропроцессору i8087 фирмы Intel, и процессором ввода-вывода КМ1810ВМ89. Модульная структура набора К1810 базируется на трех основных принципах:

Основные функции проектируемой системы распределены между специальными элементами

Многопроцессорный режим работы реализуется аппаратно

Иерархическая структура интерфейса обеспечивает эффективную обработку потока данных в высокопроизводительных системах.

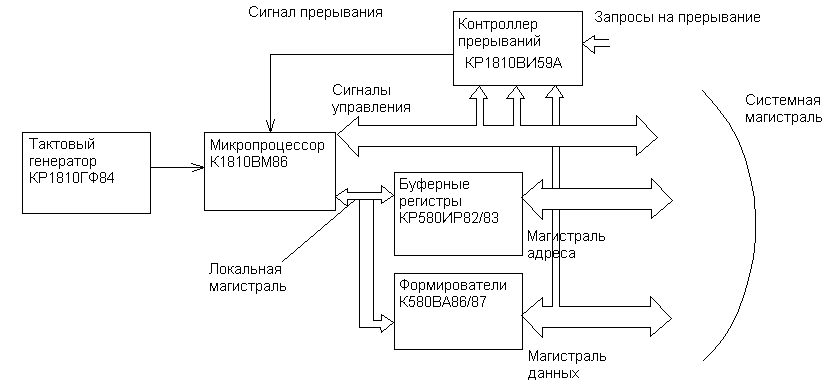

Основной микропроцессор К1810ВМ86 имеет следующие характеристики:

Тактовая частота – 5МГц

Корпус – 40 контактный

Разрядность – 16

Диапазон адресации – до 1 Мб для памяти , 64 Кб для устройств ввода-вывода

Передача данных и адреса – по одной физической линии с мультиплексированием по времени (данные после адреса).

Микропроцессор К1810ВМ86 имеет два режима работы: минимальный и максимальный. В минимальном режиме микропроцессор формирует управляющие сигналы для памяти и устройств ввода-вывода, обеспечивая однопроцессорный режим работы. В максимальном режиме сигналы управления памятью и устройствами ввода-вывода формируются контроллером КР1810ВГ88 на основании информации о состоянии микропроцессора. Линии, используемые в минимальном режиме для управления памятью и устройствами ввода-вывода, в максимальном режиме обеспечивают аппаратную реализацию многопроцессорного режима работы. Сопроцессор i8087 представляет собой 40 –контактную БИС и предназначен для выполнения арифметических операций с плавающей запятой. При его отсутствии они выполняются программно что существенно снижает производительность системы. Микропроцессор ввода-вывода КМ1810ВМ89 обычно работает под управлением центрального процессора К1810ВМ86, но может использоваться самостоятельно в контроллерах ввода-вывода. Он имеет два независимых программно – управляемых канала ввода-вывода, которые осуществляют обмен данными по прямому доступу в память со скоростью до 1,25 Мб/с. Сочетая высокую скорость передачи информации с программируемой логикой, микропроцессор КМ1810ВМ89 повышает эффективность системы, освобождая центральный процессор от рутинных операций по обработке информации устройств ввода-вывода.

Контроллер прерываний К1810ВИ59А предназначен для обработки сигналов прерываний, поступающих от периферийных устройств, и работает совместно с основным микропроцессором К1810ВМ86. Он принимает запросы от восьми источников, при каскадном подключении дополнительных контроллеров ВИ59А число источников можно увеличить до 64. Тактовый генератор К1810ГФ84 предназначен для формирования сигналов частотой 5 МГц, синхронизирующих работу микропроцессора К1810ВМ86, кроме того, формирует сигналы СБРОС и ГОТОВНОСТЬ. Буферные 8 разрядные регистры КР580ИР82 и ИР83 используются при демультиплексирования магистрали адреса – данных микропроцессора К1810ВМ86. Формирователи магистрали 8 – разрядные КР580ВА86 и ВА87 предназначены для обеспечения необходимой мощности интерфейсных сигналов, выходящих за пределы платы, они представляют собой биполярные приемопередатчики с трех стабильными выходами. Контроллер магистрали КР1810ВГ88 предназначен для декодирования байта состояния микропроцессора КМ1810ВМ89 или ВМ86 (в максимальном режиме), осуществляет генерацию во времени команд и управляющих сигналов для системной магистрали. Он также выдает сигнал стробирования адреса в буферные регистры КР580ИР82 и ИР83 во время демультиплексирования адреса – данных от микропроцессора К1810ВМ86. Арбитр шины КР1810ВБ89 предоставляет системную магистраль одному из нескольких задатчиков, которые выставили запрос на захват магистрали для доступа к ресурсам системы, например общей памяти.

На рисунке показана типовая модульная структура системы, которую можно построить на базе микропроцессорных наборов К580 и К1810. Как видно из рисунка, возможны системные и локальные магистрали, объединяющие несколько процессоров. Микропроцессоры всегда связаны с локальной магистралью, а запоминающие устройства, устройства ввода-вывода и модули процессора – с системной магистралью. Локальная магистраль реализуется микропроцессором К1810ВМ86 и координирует работу нескольких процессоров и сопроцессоров. Так в модуле центрального процессора МЦП-16 микроЭВМ СМ 1810 локальная магистраль связывает микропроцессор К1810ВМ86 и сопроцессор i8087. Системная магистраль состоит из пяти наборов сигналов: адреса, данных, управления, прерывания арбитража. Интерфейс И41 – пример общей системной магистрали, которая позволяет координировать работу модулей, выполняющих различные функции. Возможна также локальная системная магистраль, не выходящая за пределы модуля процессора, но позволяющая присоединять дополнительные устройства непосредственно к процессору. Она недоступна со стороны модулей системы, объединенных общей системной магистралью. Локальная системная магистраль разгружает общую и позволяет процессорному модулю осуществлять обмен информацией со своими устройствами, освобождая общую системную магистраль для работы с другими модулями. Таким образом, процессоры, узлы управления интерфейсами, объединенные локальной магистралью, и устройства, объединенные локальной системной магистралью (в данном случае локальная память и локальный ввод вывод), образуют модуль процессора. Простейший модуль состоит из микропроцессора, узла управления локальным интерфейсом, объединяющим локальную память и управления локальными устройствами ввода- вывода. Описанная структура построения используется при проектировании одноплатных ЭВМ, не имеющих возможностей расширения. На рис. Показан модуль процессора, предназначенный для работы в расширяемой модульной многопроцессорной системе. Узлы управления общей системной магистралью обеспечивают доступ модуля к общей памяти и обмен информацией с другими процессорными модулями. Если в системе имеется несколько процессоров, то все запоминающие устройства и устройства ввода-вывода, подсоединенные к общей системной магистрали, доступны процессорным модулям. Арбитры магистрали КР1810ВБ89 в каждом модуле процессора обеспечивают доступ модулей к общей системной магистрали, следовательно, к общей памяти и устройствам ввода - вывода.

Архитектура микроЭВМ

З

начительно

чаще используется минимальный режим

работы с разделением магистрали

адреса-данных. На рис. 2 показана схема

реализации этого режима. Два буферных

регистра КР580ИР82/83

позволяют получить доступ к памяти

объемом 64 Кб. Добавив третий буферный

регистр, объем можно увеличить до 1 Мб.

Этот режим работы позволяет эффективно

использовать компоненты из микропроцессорного

набора К580. Формирователи КР580ВА86/87

могут объединять по схеме ИЛИ магистрали

данных от нескольких источников

информации. Контроллер прерываний

КР1810ВИ59А обеспечивает реакцию процессора

на любой из восьми возможных запросов

на прерывание, при этом не требуется

опрашивать регистры состояний источников

прерываний, так как контроллер формирует

код переданного микропроцессору

источника прерывания. Минимальный режим

работы набора К1810 широко применяется

при проектировании персональных ЭВМ.