16-ти разрядный реверсивный регистр

16-ти разрядный реверсивный регистр сдвига

Техническое задание

Спроектировать 16-ти разрядный реверсивный регистр сдвига. Обеспечить преобразование результата на выходе в код 8-4-2-1 и его индикацию на семисегментном индикаторе.

Описание структурно-электрической схемы устройства

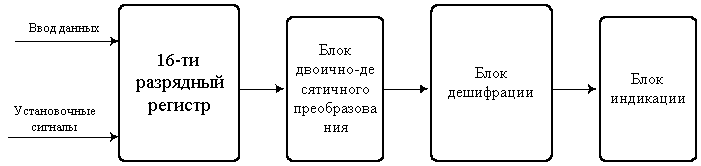

Структурная схема в Приложении 1

Она состоит из четырех основных частей:

Блок регистра

Блок преобразования

Блок дешифрации

Блок индикации

Первоначально информация в двоичном формате поступает на входы Блока регистра, предназначенного для хранения, записи и сдвига информации. Выходы блока регистра соединены с входами Блока преобразования, служащего для преобразования двоичного кода в двоично-десятичный код 8421. Далее выходы преобразователя соединены с входами Блока дешифрации, предназначенного для преобразования двоично-десятичного кода в сигналы управления семисегментными индикаторами. Выходы Блока дешифрации соединены с входами Блока индикации. Он служит для отображения результата на семисегментном индикаторе.

Выбор элементной базы

При разработке данной схемы было использовано несколько серий микросхем. При проектировании блока регистров возможно было использование микросхем типов 155ИР13 или 1533ИР24 как наиболее удовлетворяющих цели задачи. В данном случае были выбраны ИС типа ИР13 по причине более низкого потребления тока. Также для ИР24 потребовалась бы разработка дополнительного блока управления, так как данный регистр работает через двунаправленную восьмиразрядную шину данных.

Описание принципиальной электрической схемы

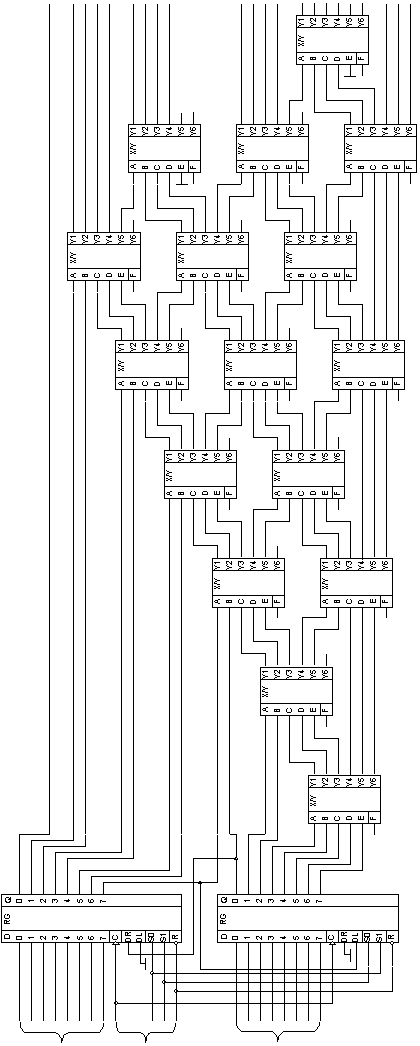

Принципиальная схема представлена в Приложении 2

Блок регистра состоит из 2-х интегральных микросхем 155ИР13, обеспечивающих синхронное функционирование в нескольких режимах.

хранение

параллельный ввод

ввод со сдвигом вправо

ввод со сдвигом влево

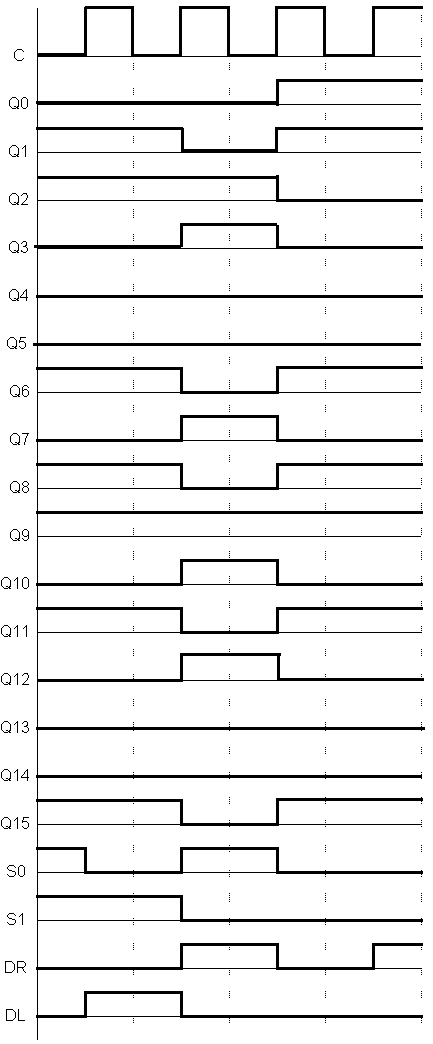

Параллельный ввод

В режиме параллельного ввода информация, представленная в параллельном коде на входе D, записывается в регистр по положительному фронту тактового импульса на входе записи. При этом на вход R подается “1”, а состояния других входов, кроме режимных, могут быть произвольными.

Последовательный ввод

Для последовательного ввода и сдвига в одну из сторон информация подается поразрядно и выбранный вход DR или DL (DR- сдвиг вправо, DL-сдвиг влево) и синхронно с положительными фронтами тактовых импульсов поступает на разрядные выходы Q0-Q7. В этом случае также R=1, на режимных входах устанавливается требуемый код, а состояние других входов произвольное.

Хранение

В режиме хранения содержимое регистра остается неизменным независимо от сигналов, поданных на установочный вход и входы данных.

Асинхронное обнуление регистра происходит при R=0.

Перед началом работы на управляющих входах устанавливается режим работы.

Режим выбирается заданием соответствующего кода на входах S. (ниже приведена таблица режимов)

Таблица режимов ИР13

-

S0

S1

Режим

0

0

Хранение

0

1

Сдвиг влево

1

0

Сдвиг вправо

1

1

Параллельный ввод

Затем на вход данных подается записываемое число.

Исходное число записывается в регистры через входы данных D0-D7 (первый регистр) и D8-D15 (второй регистр)

Входы тактовых импульсов и управляющих сигналов у обоих регистров включены параллельно.

Блок преобразования представляет собой каскадное включение интегральных микросхем типа 155ПР7 для преобразования 16-ти разрядов двоичного кода в двоично-десятичный код 8421.

ИС 155ПР7 построена на основе программируемого в процессе производства ПЗУ емкостью 256 бит и имеет соответствие между входными и выходными кодами согласно таблице истинности.

Блок дешифрации состоит из пяти ИС типа 533-ИД18, предназначенных для управления семисегментными знако-синтезирующими светодиодными матрицами типа АЛС324Б. Одной из функций управления, обеспечиваемой структурой дешифратора, является преобразование двоично-десятичного кода в семисегментный. Реализуется это при входных сигналах LT=RBI=0. В таком режиме вывод BI/RBO является входом, на котором устанавливают либо уровень логической “1”, либо его оставляют свободным. Для гашения индикатора на вход BI/RBO достаточно подать уровень логического “0”, а состояния других входов при этом могут быть произвольными.

Блок индикации представляет собой пять семисегментных знако-синтезирующих светодиодных матриц типа АЛС324Б.

При помощи них индицируется результат работы схемы.

Приложение 1