Дослідження логічних елементів емітерно-зв’язаної логіки

Міністерство Освіти та Науки України

ДНІПРОПЕТРОВСЬКИЙ НАЦІОНАЛЬНИЙ УНІВЕРСИТЕТ

Радіофізичний факультет

Кафедра радіоелектроніки

КУРСОВА РОБОТА

З курсу: Цифрова схемотехніка

На тему

Дослідження логічних елементів емітерно-зв’язаної логіки

Виконала: ст. гр. РБ-99-1

Дубіна О. Л.

Перевірив: ст. викл. каф. РЕ

Груздов В. Є.

Дніпропетровськ

2003

Реферат

Курсова робота: 25 стор., 3 табл., 16 рис., 5 літ. джерел.

ЕМІТЕРНО-ЗВ’ЯЗАНА ЛОГІКА, ЛОГІЧНІ ЕЛЕМЕНТИ, ДОСЛІДЖЕННЯ, МАКЕТ, МІКРОСХЕМА.

В даній роботі надано основні теоретичні дані логічних елементів . Згідно з теорією розроблений макет дослідження логічних елементів емітерно-зв’язаної логіки, а саме – дослідження мікросхеми, яка складається з двох логічних елементів 3АБО-НІ, за допомогою якої можна дослідити принцип роботи всіх інших типів логічних елементів. Також надані рекомендації та методичні вказівки щодо роботи зі розробленим макетом.

ЗМІСТ

Вступ 4

1.Основні теоретичні відомості 5

2.Робота приладу 12

3.Постановка задачі 18

4.Вибір схеми 19

5.Конструкція макету 20

6.Завдання для підготовки до роботи 22

7.Порядок виконання роботи 23

Висновки 24

Список використаних джерел 25

ВСТУП

В даний час у зв'язку з бурхливим розвитком науки і техніки широке застосування одержали схемотехнології, які активно застосовуються в інтегральних схемах. У даній роботі розглянута різні мікросхеми на емітерно-зв’язаній логіці, але досліджується саме мікросхема К137ЛЕ3 на логічних елементах.

ОСНОВНІ ТЕОРЕТИЧНІ ВІДОМОСТІ

Математичною основою цифрової електроніки й обчислювальної техніки є алгебра чи логіки булева алгебра (по імені англійського математика Джона Буля). У булевой алгебрі незалежні змінні чи аргументи (X) приймають тільки два значення: 0 чи 1. Залежні змінні чи функції (Y) також можуть приймати тільки одне з двох значень: 0 чи 1. Функція алгебри логіки (ФАЛ) представляється у вигляді:

Y = F (X>1>; X>2>; X>3> ... X>N> ).

Дана форма завдання ФАЛ називається алгебраїчної.

Основними логічними функціями є:

- логічне заперечення (інверсія)

Y

=

;

;

- логічне додавання (диз’юнкція)

Y = X>1> + X>2> чи Y = X>1> V X>2> ;

- логічне множення (конь’юнкція)

Y = X>1> X>2 > чи Y = X>1> X>2> .

До більш складних функцій алгебри логіки відносяться:

- функція рівнозначності (еквівалентності)

Y

= X>1>

X>2>

+

чи Y = X>1>

~

X>2>

;

чи Y = X>1>

~

X>2>

;

- функція нерівнозначності (додавання по модулі два)

Y

= X>1>

+

+

X>2 >

чи Y = X>1>

> >

X>2>

;

X>2 >

чи Y = X>1>

> >

X>2>

;

- функція Пірса (логічне додавання з запереченням)

Y

=

;

;

- функція Шеффера (логічне множення з запереченням)

Y

=

;

;

Логічний елемент – це електронний пристрій, що реалізує одну з логічних операцій. Логічні елементи являють собою електронні пристрої, у яких оброблювана інформація закодована у вигляді двійкових чисел, відображуваних напругою (сигналом) високого і низького рівня. Термін «логічні» прийшов в електроніку з алгебри логіки, що оперує зі змінними величинами і їхніми функціями, що можуть приймати тільки два значення: «істинно» чи «хибно». Для позначення чи істинності хибності висловлень використовують відповідно символи 1 чи 0. Кожна логічна перемінна може приймати тільки одне значення: 1 чи 0. Ці двійкові змінні і функції від них називаються логічними змінними і логічними функціями. Пристрою, що реалізують логічні функції, називаються логічними чи цифровими пристроями.

На рис. 1 - 10 представлені логічні елементи, що реалізують розглянені вище функції. Там же представлені так називані таблиці чи станів таблиці істинності, що описують відповідні логічні функції в двійковому коді у виді станів вхідних і вихідних перемінних. Таблиця істинності є також табличним способом завдання ФАЛ.

На рис.1 представлений елемент “НІ”, що реалізує функцію логічного заперечення Y = > >.

Рис. 1. Елемент НІ

Елемент “АБО” (рис.2) і елемент “І” (рис.3) реалізують функції логічного додавання і логічного множення відповідно.

Рис. 2. Елемент АБО.

Рис. 3. Елемент І

Функції Пірса і функції Шеффера реалізуються за допомогою елементів “АБО-НІ” і “І-НІ”, представлених на рис.4 і рис. 5 відповідно.

Рис. 4. Елемент АБО-НІ.

Рис. 5. Елемент І-НІ.

Елемент Пірса можна представити у виді послідовного з'єднання елемента “АБО” і елемента “НІ” (рис.6), а елемент Шеффера - у виді послідовного з'єднання елемента “І” і елемента “НІ” (рис.7).

На рисунку 8 і 9 представлені елементи “ Що виключає Або” і “ Що виключає АБО-НІ”, що реалізують функції нерівнозначності і нерівнозначності з запереченням відповідно.

Рис. 8. Елемент, що виключає АБО.

Рис. 9. Елемент, що виключає АБО-НІ.

Логічні елементи, що реалізують операції кон’юнкції, диз’юнкції, функції Пірса і Шеффера, можуть бути, у загальному випадку, n - входові. Так, наприклад, логічний елемент із трьома входами, що реалізує функцію Пірса, має вид, представлений на рис.10.

Рис.10

У таблиці істинності (рис.10) є вісім значень вихідних змінних Y. Ця кількість визначається числом можливих комбінацій вхідних змінних N, що, у загальному випадку, дорівнює: N = 2 n , де n - число вхідних змінних.

Логічні елементи по режиму роботи підрозділяються на статичні і динамічні. Статичні ЛЭ можуть працювати як у статичному, так і динамічному (імпульсному) режимах. Статичні елементи найбільше широко використовуються в сучасних мікросхемах. Динамічні ЛЕ можуть працювати тільки в імпульсному режимі.

Логічні елементи класифікують також за типом транзисторів, які застосовуються. Найбільше поширення одержали ЛЕ на біполярних і МДП - транзисторах і МДП – транзисторах. Крім того, інтенсивно розробляються ЛЕ на арсенід – галієвих МЕП і ГМЕП – транзисторах. Для кожного з перерахованих типів ЛЕ існує число схемотехнічних і конструктивно – технологічних різновидів.

Розглянемо найбільш розповсюджені схемотехнології, які застосовуються в інтегральних схемах:

Транзисторно-транзисторна логіка (ТТЛ).

Емітерно-зв’язана логіка (ЕЗЛ).

Логіка, побудована на основі структури метал-діелетрик-напівпровідник з п-каналом (пМДП).

Логіка, побудована на основі структури метал-діелетрик-напівпровідник із транзисторами різної провідності (КМДП).

Технологія ЕЗЛ.

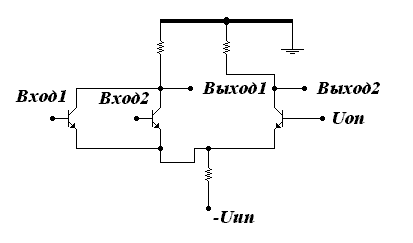

Технологія ЕЗЛ є так само, як і технологія ТТЛ, біполярною, тобто елементи будуються з використанням біполярних структур. Основою елементів ЕЗЛ є так називаний «перемикач струму», на основі якого будується базовий елемент цієї технології - АБО- -НІ (див. рис. 11); по виходу1 даної схеми реалізується логічна функція АБО-НІ, а по виходу2 - АБО.

Через низький вхідний опір схеми ЕЗЛ мають високу швидкодію і працюють переважно в активному режимі, отже, перешкода, яка попадає на вхід, підсилюється. Для підвищення перешкодостійкості шину колекторного живлення роблять дуже товстої і з'єднують із загальною шиною.

Р

ис.

11. Базовий елемент ЕЗЛ.

У порівнянні зі схемами ТТЛ схеми ЕЗЛ мають більш високу швидкодію, але пперешкодостійкість у них набагато нижче. Схеми ЕЗЛ займають велику площу на кристалі, споживають велику потужність у статичному стані, тому що вихідні транзистори відкриті і через них протікає великий струм. Схеми, побудовані за даною технологією не сумісні зі схемами, побудованими по інших технологіях, що використовує джерела позитивної напруги.

Будь-який цифровий пристрій призначений для виконання тієї чи іншої логічної функції, отже, такий пристрій можна представити у виді елементарних комірок, таких як НІ, І-НІ, АБО-НІ, які приведені нижче в таблиці 1.

Т

аблиця

1. Основні логічні функції

РОБОТА ЕЛЕМЕНТА ЕМІТЕРНО-З’ВЯЗАНОЇ ЛОГІКИ

Найбільш швидкодіючими логічними ІМС у даний час є елементи емітерно-зв’язаної логіки (ЕЗЛ) і особливо елементи емітерно-зв’язаної логіки з емітерними повторювачами на вході (ЕЕЗЛ). Ці елементи працюють у режимі переключення струму, і в них висока швидкодія забезпечується, насамперед, за рахунок запобігання насичення транзисторів шляхом введення глибокого зворотного зв’язку по струму за допомогою резистора в колі емітера. Цей зворотний зв’язок одночасно сприяє скороченню тривалості перехідних процесів у базі транзисторів. Немаловажну роль грають обмеження меж зміни перепадів напруги і використання емітерних повторювачів для введення і знімання інформації.

Найбільш простим елементом на перемикачах струму є елемент ЕЗЛ, схема якого показана на рис. 1. Особливості елементів з об’єднаними емітерами зручно пояснити на прикладі цього елемента.

Рис. 12. Мікросхема ЕЗЛ

Основу розглянутої групи ІМС складає перемикач струму, що являє собою ключовий елемент на транзисторах з об’єднаними емітерами, (на рис. 1 транзистори T>1> — Тз і Т). У емітерне коло транзисторів задається струм I>0> постійного значення. Сталість струму I>0 >підтримується або шляхом включення в коло эмиттеров порівняно високоомічного резистора R (рис. 12), або шляхом використання транзисторного джерела струму. Значення струму I>0> вибирають так, щоб у нормальному режимі роботи елемента виключалося насичення транзисторів, що утворюють перемикач струму.

Керування перемикачем струму здійснюється шляхом подачі сигналів на бази транзисторів T>1> — Т>3>. На базу транзистора T подається фіксований опорний потенціал U>оп>, значення якого вибирають так, щоб транзистор Т був здатний пропускати повністю струм I>0> при встановленні на базах вхідних транзисторів низького потенціалу, відповідаючого логічному 0. При подачі високого потенціалу, що відповідає логічній 1, на базу хоча б одного з вхідних транзисторів струм I>0> перемикається в емітерне коло відповідного вхідного транзистора. При цьому транзистор Т с фіксованим зсувом замикається. При перемиканні елемента відбувається зміна вихідних потенціалів: потенціал колекторів вхідних транзисторів знижується на, а потенціал колектора транзистора Т, підвищуючи на , досягає рівня напруги джерела живлення Е>г>.

У колі послідовно

включених перемикачів струму колекторні

потенціали не можна безпосередньо

використовувати

як вхідні напруги для керування наступними

ІМС, тому що вони перевищують рівні

відповідних потенціалів на входах. Для

нормальної роботи ІМС необхідно зробити

зрушення рівня колекторних потенціалів.

Для цієї мети найбільше часто використовують

емітерні повторювачі, що підключаються

до колекторів вхідних транзисторів і

транзистора з фіксованим зсувом (рис.

1 повторювачі

на транзисторах Т>4>

і Т>5>).

При цьому

зрушення рівня дорівнює перепаду напруги

між базою і емітером U>бэ.сд>

транзистора. Цим перепадом напруги

лімітується розмах логічного

сигналу

.

.

Дійсно, на базу вхідного

транзистора в провідному стані подається

вхідна напруга

,

яке відповідає логічній

1, що призводить до відмикання цього

транзистора і зниженню

потенціалу колекторів вхідних

транзисторів.

При цьому, щоб відкритий

транзистор не насичувався, Необхідно

забезпечити виконання умови

,

яке відповідає логічній

1, що призводить до відмикання цього

транзистора і зниженню

потенціалу колекторів вхідних

транзисторів.

При цьому, щоб відкритий

транзистор не насичувався, Необхідно

забезпечити виконання умови

,

що можливо тільки

в тому випадку, якщо перепад напруги на

колекторі не перевищує напруга зрушення,

створена повторювачем, тобто при

,

що можливо тільки

в тому випадку, якщо перепад напруги на

колекторі не перевищує напруга зрушення,

створена повторювачем, тобто при

(1)

(1)

Порушення цієї умови приводить до насичення транзистора, тому що потенціал його колектора виявляється нижче потенціалу бази. Отже, збільшення розмаху логічного сигналу, який визначається перепадом напруги в колекторному колі вхідних транзисторів, припустимо тільки при відповідному збільшенні зсуву рівня U>бэ.сд>. Цього можна досягти, наприклад, шляхом вмикання додаткового діода, що зміщає, у емітерні кола транзисторів Т>4> і Т>5> . Емітерні повторювачі (без зсувних діодів) забезпечують зсув рівня, що складає 0,8 - 0,9 В. Розмах логічного сигналу, дорівнює цьому значенню, виявляється достатнім для більшості цифрових автоматів, побудованих на елементах ЕЗЛ. При цьому, щоб одержати однаковий розмах логічного сигналу на що інвертуючому і неінвертуючому виходах елемента значення опорів резисторів R>Kl> =R>K2> вибираються рівними один одному: R>Kl> =R>K2> = R>K>.

Включення повторювачів призводить також до зменшення вихідного опору елемента, що сприяє підвищенню його навантажувальної здатності і швидкодії. Таким чином, перемикач струму, доповнений емітерними повторювачами, стає логічним елементом, що реалізує операції АБО-НІ і АБО. Сигнал, що відповідають операції АБО-НІ, знімається з виходу повторювача, підключеного до інвертуючої половини елемента (тобто до колекторів вхідних транзисторів), а сигнал, що відповідає операції АБО, — з виходу повторювача, зв’язаного з транзистором Т (рис. 12).

Елементи на перемикачах струму виготовляються у вигляді напівпровідникових чи сполучених ІМС. Так як в цих ІМС транзистори працюють без насичення, то шляхом підключення підкладки та ізолюючих шарів к точкам відповідно з найменшим і найбільшим потенціалами можна замкнути паразитні транзистори, вимкнувши тим самим їх активну дію. Тому в ІМС на перемикачах струму виявляється тільки ємнісний вплив підкладки.

На рис. 13 показана перемикальна характеристика мікросхеми ЕЗЛ для двох її виходів: інвертуючого (U>в>>ых1>) та неінвертуючого (U>в>>ых2>).

рис . 13. Перемикальні характеристики мікросхеми ЕЗЛ.

При вхідних напругах, менших потенціалу відмикання, вхідні транзистори залишаються замкненими і на інвертуючому встановлюється високий потенціал

(2)

(2)

відповідний логічній 1 (l>э>>с>.—.число вхідних транзисторів). При цьому струм I>0> цілком відбирається транзистором Т з фіксованим зсувом і на неінвертуючому виході установлюється низький потенціал

(3)

відповідний

логічному 0. Розмах логічного сигналу

(3)

відповідний

логічному 0. Розмах логічного сигналу

(4)

(4)

Коли напруга U>ВХ> досягає потенціалу відмикання, вхідні транзистори починають проводити, і струм I>0> частково відгалужується в емітери провідних транзисторів. Якщо одночасно проводять l>пр> вхідних транзисторів (із загального числа l>э>>с>), то потенціал колектора цих транзисторів зменшується і відповідно знижується напруга на інвертуючому виході до рівня

(5)

(5)

Через перерозподіл струму I>0> змінюється і напруга на неінвертуючому виході

(6)

(6)

Струми емітерів І>э1> і І>э> відповідно для вхідних транзисторів і транзистора Т визначаються співвідношеннями

(7)

(7)

де U>0> = I>o>R — потенціал об’єднаних емітерів відносно загальної шини живлення.

При

відмиканні вхідних транзисторів

трохи змінюється

струм I>0>

і відповідно

потенціал

об’єднаних емітерів

U>0>.

Зміна струму I>0>

настільки

незначна, що їм

можна не враховувати. Не так істотно

змінюється і потенціал U>0>

(у порівнянні зі своїм середнім значенням).

Однак ця незначна зміна U>0>

порівнянна з напругою на

емітерних переходах транзисторів. Саме

вона призводить до зміни струму емітера

І>э>

транзистора з фіксованим зсувом,

тому .для правильного розрахунку

перемикальної

характеристики

необхідно враховувати зміну

U>0>

зі зміною вхідної напруги U>вх>.

Залежність U>0>

про від U>вх>

можна визначити

із рівняння І>0>

= І>пр>І>э1>+

І>э>,

представивши

його в наступному виді:

необхідно враховувати зміну

U>0>

зі зміною вхідної напруги U>вх>.

Залежність U>0>

про від U>вх>

можна визначити

із рівняння І>0>

= І>пр>І>э1>+

І>э>,

представивши

його в наступному виді:

Визначивши із цього рівняння

можна виразити залежність вихідних напруг від вхідної напруги наступними співвідношеннями:

(8)

(8)

При зміні вхідної напруги трохи міняється і різниця потенціалів U>бэ.сд> на емітерному переході транзисторів у схемах повторювачів. Тому що в робочому діапазоні відхилення U>бэ.сд> від свого середнього значення незначні, то при практичних розрахунках ними можна зневажати, прийнявши

(9)

(9)

Це значення U>бэ.сд> відповідає середньому значенню струму емітера транзистора в схемі повторювача, який визначається зі співвідношення

(10)

(10)

де

Тому що

та

та

визначаються через U>бэ.сд>

, то при первісних

розрахунках зручно замість формули (9)

скористатися

співвідношенням ,

визначаються через U>бэ.сд>

, то при первісних

розрахунках зручно замість формули (9)

скористатися

співвідношенням ,

(11)

(11)

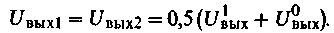

заснованим на рівності

U>оп>

=0,5( +

+

),

до виконання

якого звичайно прагнуть, щоб забезпечити

симетрію елемента

по граничних напругах.

),

до виконання

якого звичайно прагнуть, щоб забезпечити

симетрію елемента

по граничних напругах.

Коли транзистор Т перестає проводити, струм І>0> цілком відбирається провідними вхідними транзисторами. Після цього зі збільшенням вхідної напруги спостерігається зменшення напруги на інвертуючому виході U>в>>ых1> Тому що після повного переключення струму І>0 >провідні вхідні транзистори працюють із глибоким негативним зворотним зв'язком по струму, що протікає через резистор R, то зменшення U>в>>ых1 >незначне. При напрузі U>в>>х.нас> транзистори насичуються, їхній базовий струм відгалужується в колекторний ланцюг, зменшуючи перепад напруги на R>K1>, тому U>в>>ых1> зростає (рис. 13). Насичення вхідних транзисторів порушує нормальний режим роботи ІМС, тому шляхом відповідного підбора параметрів схеми і напруг джерел живлення такий режим роботи вимикається.

Як видно з графіків на рис. 13, перемикальні характеристики U>в>>ых1> і U>в>>ых2> перетинаються в точці 3, координати якої можна визначити з рівняння U>в>>ых1>= U>в>>ых2 > На підставі цього рівняння можна показати, що перемикальні характеристики перетинаються при вхідній напрузі:

При цьому

тобто в точці перетину

(12)

(12)

Якщо опорна напруга

обрана рівним середньому значенню

,

тобто

,

тобто

(13)

(13)

те робочі точки 1 і 2 розташовуються симетрично щодо середньої точки 3 для l>пр> = 1 (рис. 13).

Тому

що в мікросхемі ЕЗЛ транзистори працюють

в активній області у всьому робочому

діапазоні зміни вхідної напруги, те

перешкодостійкість обмежується напругою,

при якій коефіцієнт підсилення логічного

елемента по відповідним виходах зростає

до 1. На підставі (8) можна показати, що

коефіцієнт підсилення по інвертуючому

виходу стає рівним мінус одиниці

при вхідній напрузі

при вхідній напрузі

(14)

(14)

а по неинвертирующему

виході-одиниці

1),

коли вхідна напруга досягає

1),

коли вхідна напруга досягає

(15)

(15)

Коефіцієент К визначається виразом

(16)

(16)

Перешкодостійкість ІМС, яка визначається як різниця вхідних напруг у робочих струмах і при одиничному коефіцієнті підсилення, розраховується за формулами

які виходять на підставі формул, виведених вище. Помітимо, що при l>пр>=1 перешкодостійкість для логічної 1 і логічного 0 по входу виявляється однаковою. Зі збільшенням числа провідних транзисторів l>пр> симетрія ІМС по перешкодостійкості порушується; перешкодостійкість для логічної 1 стає більше перешкодостійкою для логічного 0.

При визначенні навантажувальної здатності і коефіцієнта об'єднання по входу в ИМС на перемикачах струму припустимі значення перешкодостійкості не є визначальними, як це має місце для інших типів логічних елементів. Для розглянутої групи ИМС зазначені параметри визначаються припустимим збільшенням тривалості перехідних процесів, тому що ІМС на перемикачах струму є швидкодіючими і саме цей параметр для них є визначальним.

Підвищення швидкодії елемента ЕЗЛ досягається шляхом помітного збільшення споживаної потужності. Середнє значення цієї потужності можна розрахувати по формулі

(17)

(17)

у який перший доданок

— це потужність,

споживана

перемикачем струму, а другий доданок

— це потужність,

споживана

перемикачем струму, а другий доданок

- середня потужність,

споживана емітерними

повторювачами. Виразивши на підставі

(13) напругу Е>к>

через U>оп>,

- середня потужність,

споживана емітерними

повторювачами. Виразивши на підставі

(13) напругу Е>к>

через U>оп>,

U>лог>

та U>бэ.сд>

, одержимо:

U>лог>

та U>бэ.сд>

, одержимо:

(18)

(18)

Подальше удосконалення логічних елементів на перемикачах струму призвело до розробки ІМС емітерно-зв’язаної логіки з емітерними повторювачами на вході (скорочено ЕЕЗЛ елементи). У мікросхемі елемента ЕЗЛ (рис. 12) емітерні повторювачі вмикаються до виходів елемента для знімання інформації. При цьому перемикач струму складається з вхідних транзисторів, що використовуються для введення інформації і транзистора з опорною напругою. До виходу кожного повторювача підключають транзистори, кожний з який є вхідним елементом наступних перемикачів струму.

3. ПОСТАНОВКА ЗАДАЧІ

Згідно з раніше вказаним, існує багато мікросхем , які працюють на на емітерно-зв’язаній логіці. Для їх дослідження необхідно було розробити та виготовити експериментальний макет, на якому було б можливо проводити дослідження принципа їх роботи.

Крім того необхідно було розробити методичні вказівки щодо дослідження логічних елементів емітерно-зв’язаної логіки на цьому макеті.

4.ВИБІР СХЕМИ

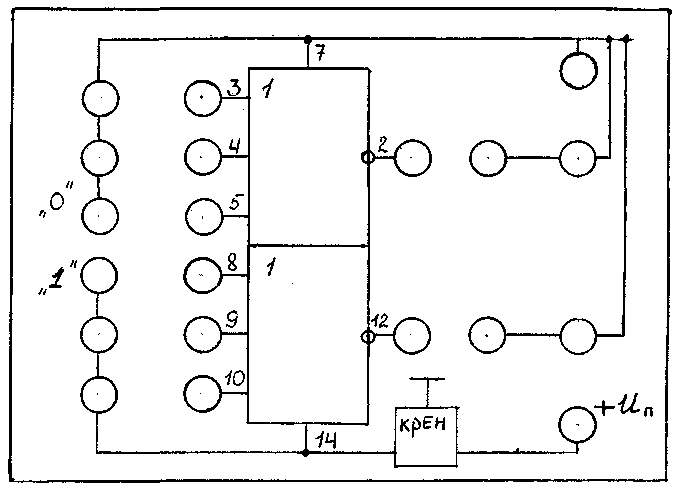

Виберемо нескладну схему на мікросхемі К137ЛЄ3, яка складається з двох елементів АБО-НІ(Рис.14).

Мікросхема має 14 ніжок. 7-ма ніжка відповідає напрузі живлення +5 В, 14-та – заземленню. Перша ніжка не використовується. На рис. 14 також вказана повна цокольовка схеми, а на рис. - таблиця відповідності роботи цієї мікросхеми.

Рис.14. Цокольовка мікросхеми К137ЛЕ3 та її принципова схема

Рис. 15. Таблиця відповідності мікросхеми К137ЛЕ3 .

Таблицю відповідності ми наводимо для одного елемента АБО-НІ тому, що мікросхема складається з двох таких однакових елементів.

Для запобігання пошкодження мікросхеми через перенапругу на вході поставлено стабілізатор напруги КРЕН5А розрахований на напругу 5В. Задля полегшення спостерігання проходження імпульсів на макеті під΄єднано два світлодіоди. Для запобігання їх ушкодження встановлені два резистори на 330 Ом кожний.

5.КОНСТРУКЦІЯ МАКЕТА

Конструктивно макет виконаний у виді набору пластин розмірами 110х80 мм.

Одна з пластин є лицьовою частиною макета. Вона у свою чергу містить дві пластини: верхня – ламінований поліетилен, нижня – ДВП. У них уставлені залізні розйоми верхнім діаметром 8 мм, нижнім – 6мм.

Друга пластина – друкована плата, виготовлена з фольгованого гетинаксу, з витравленими доріжками за допомогою хлорованого заліза (FeCl3).Для кращого контактування на доріжки нанесений припой.

Третя пластина є підставкою під макет, передбаченої щоб уникнути контакту плати зі сторонніми предметами. Вона виконана з ДВП поперечним розміром 3 мм.

Доріжки на платі з лицьовою частиною макета з'єднані дротинками довжиною 30-50 мм і діаметром 0,5 мм.

Усі пластини з'єднані і закріплені за допомогою чотирьох болтів розмірами 4х40 мм із потайною голівкою і шістнадцяти гайок відповідного діаметра.

Таким чином, метод виготовлення макета – друкована плата з елементами начіпного монтажу.

а)

б)

Рис.16. Схематичне зображення лицьової частини макета (а) та (б) - доріжок на платі.

6.ЗАВДАННЯ ДЛЯ ПІДГОТОВКИ ДО РОБОТИ

При підготовці до виконання даної лабораторної роботи студенти повинні:

1. Вивчити теоретичний матеріал відповідних лекцій.

2. Підготувати відповіді на контрольні питання, поміщені наприкінці даного керівництва.

3. Заготовити звіт по даній лабораторній роботі, для чого

- виконати необхідні з'єднання для дослідження схеми даної мікросхеми , підключивши до її інверсних виходів як індикатори світлодіоди;

- нарисувати позначення відповідно до Дст мікросхеми К137ЛЕ3;

- нарисувати схему базового елемента емітерно-звязаної логіки.

- повторити опис лабораторної установки і порядок роботи з нею.

- задавая різні комбінації вхідних логічних сигналів, визначити значення виходного сигналу та за результатами вимірювань заповнити таблицю істиності для одного з елементів, з яких складається мікросхема К137ЛЕ3.

- без допомоги теорії, на основі результатів лабораторної роботи та аналіза складеної таблиці істиності для досліджуваного елемента визначини функціональне значення логічного елемента.

Таблиця 3.

|

X>1> |

X>2> |

X>3> |

Y |

|

0 |

0 |

0 |

|

|

1 |

0 |

0 |

|

|

0 |

1 |

0 |

|

|

1 |

1 |

0 |

|

|

0 |

0 |

1 |

|

|

1 |

0 |

1 |

|

|

0 |

1 |

1 |

|

|

1 |

1 |

1 |

4. Дослідити перемикальні характеристики, які зображені на рис. 13. Також зафіксувати вхідні та вихідні струми логічних 0 та 1; порогові напруги логічних 0 та 1; токи споживання ІМС для станів 0 та 1, про які було сказано вище.

7.ПОРЯДОК ВИКОНАННЯ РОБОТИ

1.Підготувати до роботи вольтомметр. Уключити лабораторну установку, установити напругу живлення — Еж = +5В .

2. Дослідити в лабораторній роботі пристрій, представлений на рис.15. Пристрій являє собою 2 елементи 3АБО-НІ, виконаних на микросхемі серії К137.

3. Задати необхідні значення сигналів Х2, Х1 і, формуючи на кожному з двох елементів АБО-НІ сигнал У1 та У2, дослідити таблицю переходів.

4. Заповнити таблицю переходів у бланку звіту і показати її викладачу з демонстрацією переходів елемента з одного стану в інший безпосередньо на макеті лабораторної установки.

5. Подати на один із входів логічного елемента імпульсний сигнал U>вх>=5В, час імпульсу t>i>=0.5 мс, період Т=1мс; зняти залежність U>вих>=f(U>вх>) та дослідити часові спотворення. Визначити рівень вихідних напруг для мікросхем даної серії.

6. Виявити швидкодію мікросхеми, також зафіксувати вхідні та вихідні струми логічних 0 та 1; порогові напруги логічних 0 та 1; токи споживання ІМС для станів 0 та 1.

8. КОНТРОЛЬНІ ЗАПИТАННЯ

1. Якими значеннями змінних оперує алгебра логіки?

2. Основні форми завдання ФАЛ

3. Виглядд основних логічних функцій в алгебраїчній формі.

4. Що таке “логічний елемент”?

5. Які логічні функції виконують елементи пірса та Шеффера?

6. Чим визначається число можливих комбінацій вхідних змінних для будь-якого логічного елемента?

7. Назвати параметри міпросхеми ЕЗЛ.

ВИСНОВКИ

В результаті виконаної курсової роботи виготовлено лабораторний макет, який виявився працездатним. Розроблені та надані рекомендації і методичні вказівки щодо виконання дослідження на цьому макеті.

СПИСОК ВИКОРИСТАНИХ ДЖЕРЕЛ

Зельдин Е. А. Цифровые интегральные микросхемы в информационно-измерительной литературе. –Л.: Энергоатомиздат, 1986.-276 с.

Каган Б. М. Электронные вычислительные машины и системы. –М.:Энергия, 1979. –525с.

Куценко В. М., Згурский А. В.,Сташук Л.Д. Импульсные и цифровые узлы ЭВМ и техники связи. Лабораторный практикум: Учеб пособие. -К.:Выща шк. Головное издательство,1989.-157 с.

Применение интегральных микросхем в электронной вычислительной технике/Под ред. Б. Н. Файзулаева, Б. В. Тарабрина. –М.:Радио и сязь, 1987. –380 с.

Цифровые вычислительные машины и системы. –М.:Энергия, 1979. –525 с.