–†–∞–Ј—А–∞–±–Њ—В–Ї–∞ –±–ї–Њ–Ї–∞ –і–Є–љ–∞–Љ–Є—З–µ—Б–Ї–Њ–≥–Њ –Ю–Ч–£ —Б –Љ—Г–ї—М—В–Є–њ–ї–µ–Ї—Б–Њ—А–Њ–Љ –Ї–Њ–і–∞ –∞–і—А–µ—Б–∞

–•–Ґ–Ъ–≠–Ь

–Ъ—Г—А—Б–Њ–≤–Њ–є –њ—А–Њ–µ–Ї—В.

–Ґ–µ–Љ–∞:

–†–∞–Ј—А–∞–±–Њ—В–Ї–∞ –±–ї–Њ–Ї–∞ –і–Є–љ–∞–Љ–Є—З–µ—Б–Ї–Њ–≥–Њ –Ю–Ч–£ —Б –Љ—Г–ї—М—В–Є–њ–ї–µ–Ї—Б–Њ—А–Њ–Љ –Ї–Њ–і–∞ –∞–і—А–µ—Б–∞.

–Т—Л–њ–Њ–ї–љ–Є–ї –Х—А–Њ—Е–Є–љ –Т.–Р.

–Я—А–Њ–≤–µ—А–Є–ї –Ъ–∞–ї–Є–љ–Ї–Є–љ–∞ –Ь.–Т.

2000–≥.

–•–Ш–Ь–Ъ–Ш–Э–°–Ъ–Ш–Щ –Ґ–Х–•–Э–Ш–Ъ–£–Ь –Ъ–Ю–°–Ь–Ш–І–Х–°–Ъ–Ю–У–Ю –≠–Э–Х–†–У–Ю–Ь–Р–®–Ш–Э–Ю–°–Ґ–†–Ю–Х–Э–Ш–ѓ

–Ч–Р–Ф–Р–Э–Ш–Х

–Ф–Ы–ѓ –Ъ–£–†–°–Ю–Т–Ю–У–Ю –Я–†–Ю–Х–Ъ–Ґ–Ш–†–Ю–Т–Р–Э–Ш–ѓ –Я–Ю –Ъ–£–†–°–£________________________________

_ ___3________–Ъ–£–†–°–Р____–≠-32

97__–У–†–£–Я–Я–Ђ

–£–І–Р–©–Х–У–Ю–°–ѓ__–Х—А–Њ—Е–Є–љ–∞_________

___3________–Ъ–£–†–°–Р____–≠-32

97__–У–†–£–Я–Я–Ђ

–£–І–Р–©–Х–У–Ю–°–ѓ__–Х—А–Њ—Е–Є–љ–∞_________

–Т–ї–∞–і–Є–Љ–Є—А–∞ –Р–ї–µ–Ї—Б–∞–љ–і—А–Њ–≤–Є—З–∞

(—Д–∞–Љ–Є–ї–Є—П, –Є–Љ—П –Є –Њ—В—З–µ—Б—В–≤–Њ)

—В–µ–Љ–∞ –Ч–Р–Ф–Р–Э–Ш–ѓ –Ш –Ш–°–•–Ю–Ф–Э–Ђ–Х –Ф–Р–Э–Э–Ђ–Х_–†–∞–Ј—А–∞–±–Њ—В–Ї–∞ –±–ї–Њ–Ї –і–Є–љ–∞–Љ–Є—З–µ—Б–Ї–Њ–≥–Њ –Ю–Ч–£ —Б –Љ—Г–ї—М—В–Є–њ–ї–µ–Ї—Б–Њ—А–Њ–Љ –Ї–Њ–і–∞ –∞–і—А–µ—Б–∞ –µ–Љ–Ї–Њ—Б—В—М—О 16–Ъ –±–∞–є—В –і–ї—П 8-—А–∞–Ј—А—П–і–љ—Л—Е –Љ–Є–Ї—А–Њ–њ—А–Њ—Ж–µ—Б—Б–Њ—А–љ—Л—Е —Г—Б—В—А–Њ–є—Б—В–≤

–Я—А–Є –≤—Л–њ–Њ–ї–љ–µ–љ–Є–Є –Ї—Г—А—Б–Њ–≤–Њ–≥–Њ –њ—А–Њ–µ–Ї—В–∞ –љ–∞ —Г–Ї–∞–Ј–∞–љ–љ—Г—О —В–µ–Љ—Г –і–Њ–ї–ґ–љ—Л –±—Л—В—М –њ—А–µ–і—Б—В–∞–≤–ї–µ–љ—Л:

1 .–Я–Њ—П—Б–љ–Є—В–µ–ї—М–љ–∞—П –Ј–∞–њ–Є—Б–Ї–∞

______________________________________________________________________________________________________________________

2.–У—А–∞—Д–Є—З–µ—Б–Ї–∞—П —З–∞—Б—В—М –њ—А–Њ–µ–Ї—В–∞

–Ы–Ш–°–Ґ 1.________________________________________________________________________

2._________________________________________________________________

2._________________________________________________________________

–Ф–∞—В–∞ –≤—Л–і–∞—З–Є ____________________________

–°—А–Њ–Ї –Њ–Ї–Њ–љ—З–∞–љ–Є—П ____________

–Я—А–µ–њ–Њ–і–∞–≤–∞—В–µ–ї—М-—А—Г–Ї–Њ–≤–Њ–і–Є—В–µ–ї—М –Ї—Г—А—Б–Њ–≤–Њ–≥–Њ –њ—А–Њ–µ–Ї—В–Є—А–Њ–≤–∞–љ–Є—П .

–Т–≤–µ–і–µ–љ–Є–µ.

–Ю–Ч–£ –≤—Л–њ–Њ–ї–љ—П—О—В –Ј–∞–њ–Є—Б—М, —Е—А–∞–љ–µ–љ–Є–µ –Є —Б—З–Є—В—Л–≤–∞–љ–Є–µ –њ—А–Њ–Є–Ј–≤–Њ–ї—М–љ–Њ–є –і–≤–Њ–Є—З–љ–Њ–є –Є–љ—Д–Њ—А–Љ–∞—Ж–Є–Є. –Ю–љ–Њ —П–≤–ї—П–µ—В—Б—П –Њ—Б–љ–Њ–≤–љ—Л–Љ —Г—Б—В—А–Њ–є—Б—В–≤–Њ–Љ –њ–∞–Љ—П—В–Є —Ж–Є—Д—А–Њ–≤—Л—Е —Б–Є—Б—В–µ–Љ, –≤ –Ї–Њ—В–Њ—А–Њ–Љ —Е—А–∞–љ—П—В—Б—П –њ—А–Њ–≥—А–∞–Љ–Љ—Л, –Њ–њ—А–µ–і–µ–ї—П—О—Й–Є–µ –њ—А–Њ—Ж–µ—Б—Б —В–µ–Ї—Г—Й–µ–є –Њ–±—А–∞–±–Њ—В–Ї–Є –Є–љ—Д–Њ—А–Љ–∞—Ж–Є–Є –Є –Љ–∞—Б—Б–Є–≤ –Њ–±—А–∞–±–∞—В—Л–≤–∞–µ–Љ—Л—Е –і–∞–љ–љ—Л—Е. –°–Њ–≤—А–µ–Љ–µ–љ–љ—Л–µ —Ж–Є—Д—А–Њ–≤—Л–µ —Б–Є—Б—В–µ–Љ—Л –Ю–Ч–£ —Б—В—А–Њ—П—В—Б—П –Є–Ј —Б–њ–µ—Ж–Є–∞–ї—М–љ—Л—Е –Љ–Є–Ї—А–Њ—Б—Е–µ–Љ –њ–∞–Љ—П—В–Є, –Ї–Њ—В–Њ—А—Л–µ –Њ–±—К–µ–і–Є–љ—П—О—В—Б—П –≤ —Б–Њ–Њ—В–≤–µ—В—Б—В–≤—Г—О—Й–Є–є —Д—Г–љ–Ї—Ж–Є–Њ–љ–∞–ї—М–љ—Л–є –±–ї–Њ–Ї.

–¶–µ–ї—М—О –Ї—Г—А—Б–Њ–≤–Њ–≥–Њ –њ—А–Њ–µ–Ї—В–∞ —П–≤–ї—П–µ—В—Б—П —А–∞–Ј—А–∞–±–Њ—В–Ї–∞ –±–ї–Њ–Ї–∞ –і–Є–љ–∞–Љ–Є—З–µ—Б–Ї–Њ–≥–Њ –Ю–Ч–£ –µ–Љ–Ї–Њ—Б—В—М—О 16–Ъ–±–∞–є—В –і–ї—П 8-—А–∞–Ј—А—П–і–љ—Л—Е –Љ–Є–Ї—А–Њ–њ—А–Њ—Ж–µ—Б—Б–Њ—А–љ—Л—Е —Г—Б—В—А–Њ–є—Б—В–≤ –Є –Ј–∞–Ї—А–µ–њ–ї–µ–љ–Є–µ –њ–Њ–ї—Г—З–µ–љ–љ—Л—Е –≤ –њ—А–Њ—Ж–µ—Б—Б–µ –Є–Ј—Г—З–µ–љ–Є—П –і–Є—Б—Ж–Є–њ–ї–Є–љ—Л –≠–Т–Ь —Б–Є—Б—В–µ–Љ—Л, –Ї–Њ–Љ–њ–ї–µ–Ї—Б—Л –Є —Б–µ—В–Є –Ј–љ–∞–љ–Є–є –њ–Њ –і–Є–љ–∞–Љ–Є—З–µ—Б–Ї–Њ–є –њ–∞–Љ—П—В–Є.

1.–Ю—А–≥–∞–љ–Є–Ј–∞—Ж–Є—П —А–∞–±–Њ—В—Л –±–ї–Њ–Ї–∞ –і–Є–љ–∞–Љ–Є—З–µ—Б–Ї–Њ–≥–Њ –Ю–Ч–£ —Б –Љ—Г–ї—М—В–Є–њ–ї–µ–Ї—Б–Њ—А–Њ–Љ –Ї–Њ–і–∞ –∞–і—А–µ—Б–∞.

–Ф–ї—П —А–µ–∞–ї–µ–Ј–∞—Ж–Є–Є —Г—Б—А–Њ–є—Б—В–≤–∞ –љ–µ–Њ–±—Е–Њ–і–Є–Љ—Л: –љ–∞–Ї–Њ–њ–Є—В–µ–ї—М –Є–љ—Д–Њ—А–Љ–∞—Ж–Є–Є, —Б–Њ—Б—В–Њ—П—Й–Є–є –Є–Ј –Љ–Є–Ї—А–Њ—Б—Е–µ–Љ –њ–∞–Љ—П—В–Є (–Љ–Њ–і—Г–ї—М –њ–∞–Љ—П—В–Є), –Є —Б—Е–µ–Љ—Л —Г–њ—А–∞–≤–ї–µ–љ–Є—П.

–°—В—А—Г–Ї—В—Г—А–љ–∞—П —Б—Е–µ–Љ–∞ —В–∞–Ї–Њ–≥–Њ –±–ї–Њ–Ї–∞ –њ–Њ–Ї–∞–Ј–∞–љ–∞ –≤ –њ—А–Є–ї–Њ–ґ–µ–љ–Є–Є 4.

–Ь–Њ–і—Г–ї—М –њ–∞–Љ—П—В–Є, –Њ–±–Њ–Ј–љ–∞—З–∞–µ–Љ—Л–є –Ї–∞–Ї DD1-DD8 –љ–∞ —Д—Г–љ–Ї—Ж–Є–Њ–љ–∞–ї—М–љ–Њ–є —Б—Е–µ–Љ–µ (–њ—А–Є–ї–Њ–ґ–µ–љ–Є–µ 5), –њ–Њ—Б—В—А–Њ–µ–љ –љ–∞ –Љ–Є–Ї—А–Њ—Б—Е–µ–Љ–∞—Е –Ъ565–†–£3–У –њ—Г—В–µ–Љ —Б–Њ–µ–і–Є–љ–µ–љ–Є—П –Є—Е –Њ–і–љ–Њ–Є–Љ–µ–љ–љ—Л—Е –≤—Л–≤–Њ–і–Њ–≤, –Ї—А–Њ–Љ–µ –Є–љ—Д–Њ—А–Љ–∞—Ж–Є–Њ–љ–љ—Л—Е. –°–Є–≥–љ–∞–ї—Л RAS –Є CAS —Д–Њ—А–Љ–Є—А—Г–µ—В –Ї–Њ–љ—В—А–Њ–ї–ї–µ—А –Ю–Ч–£ CLC. , —Б–Є–≥–љ–∞–ї MWTC —Б —И–Є–љ—Л —Г–њ—А–∞–≤–ї–µ–љ–Є—П –њ–Њ–і–∞–љ –љ–∞ –≤—Е–Њ–і W/R. –Ф–ї—П —Б–љ–Є–ґ–µ–љ–Є—П —Б—В–µ–њ–µ–љ–Є —А–∞—Б—Б–Њ–≥–ї–∞—Б–Њ–≤–∞–љ–Є—П —Б –Ґ–Ґ–Ы —Г–њ—А–∞–≤–ї—П—О—Й–Є–Љ–Є —Н–ї–µ–Љ–µ–љ—В–∞–Љ–Є —Ж–µ–ї–µ—Б–Њ–Њ–±—А–∞–Ј–љ–Њ –њ–Њ–і–Ї–ї—О—З–µ–љ–Є–µ –≤—Б–µ—Е –∞–і—А–µ—Б–љ—Л—Е –Є —Г–њ—А–∞–≤–ї—П—О—Й–Є—Е –ї–Є–љ–Є–є –Ї–Њ –≤—Е–Њ–і–∞–Љ –Љ–Є–Ї—А–Њ—Б—Е–µ–Љ –њ–∞–Љ—П—В–Є –Њ—Б—Г—Й–µ—Б—В–≤–ї—П—В—М —З–µ—А–µ–Ј —А–µ–Ј–Є—Б—В–Њ—А—Л —Б —Б–Њ–њ—А–∞—В–Є–≤–ї–µ–љ–Є–µ–Љ 20-30 –Ю–Љ.

–С—Г—Д–µ—А –≤—Л—Е–Њ–і–љ—Л—Е –і–∞–љ–љ—Л—Е DD13 —А–µ–∞–ї–Є–Ј–Њ–≤–∞–љ –љ–∞ –њ–∞—А—А–∞–ї–µ–ї—М–љ–Њ–Љ 8-—А–∞–Ј—А—П–і–љ–Њ–Љ —А–µ–≥–Є—Б—В—А–µ –Ъ–†580–Ш–†82. –°–Є–≥–љ–∞–ї —Г–њ—А–∞–≤–ї–µ–љ–Є—П —А–µ–≥–Є—Б—В—А–Њ–Љ –≤—Л—А–∞–±–∞—В—Л–≤–∞–µ—В –Ї–Њ–љ—В—А–Њ–ї–ї–µ—А –Ю–Ч–£. –°–Є–≥–љ–∞–ї –Ю–Х —Г–њ—А–∞–≤–ї—П–µ—В –≤—Л—Е–Њ–і–∞–Љ–Є: –њ—А–Є 0 –Њ–љ–Є –Њ—В–Ї—А—Л—В—Л –і–ї—П —Б—З–Є—В—Л–≤–∞–љ–Є—П, –њ—А–Є 1-–њ–µ—А–µ—Е–Њ–і—П—В –≤ —В—А–µ—В—М–µ —Б–Њ—Б—В–Њ—П–љ–Є–µ, —Б–Є–≥–љ–∞–ї –°–Х —Г–њ—А–∞–≤–ї—П–µ—В –≤—Е–Њ–і–∞–Љ–Є: –њ—А–Є 1 –Њ–љ–Є –Њ—В–Ї—А—Л—В—Л –і–ї—П –Ј–∞–њ–Є—Б–Є, –њ—А–Є 0 –±–ї–Њ–Ї–Є—А–Њ–≤–∞–љ—Л.

–Т –±–ї–Њ–Ї–µ –Ю–Ч–£ –±—Г—Д–µ—А–Є–Ј–Њ–≤–∞–љ—Л —В–Њ–ї—М–Ї–Њ –µ–≥–Њ –≤—Л—Е–Њ–і–љ—Л–µ –ї–Є–љ–Є–Є.

–Ь—Г–ї—М—В–Є–њ–ї–µ–Ї—Б–Њ—А DD9-DD12 –≤—Л–њ–Њ–ї–љ–µ–љ–љ—Л–є –љ–∞ —Б—Е–µ–Љ–∞—Е –Ъ555–Ъ–Я2 –Њ–±–µ—Б–њ–µ—З–Є–≤–∞–µ—В –њ–Њ—Б–ї–µ–і–Њ–≤–∞—В–µ–ї—М–љ—Л–є –≤–Њ –≤—А–µ–Љ–µ–љ–Є –≤–≤–Њ–і –∞–і—А–µ—Б–љ–Њ–≥–Њ –Ї–Њ–і–∞ —Б—В—А–Њ–Ї AX {AO-A7} –Є —Б—В–Њ–ї–±—Ж–Њ–≤ AY {A8-A15} –≤ –Љ–Њ–і—Г–ї—М –Ю–Ч–£.

–Р–і—А–µ—Б–љ—Л–µ —Б–Є–≥–љ–∞–ї—Л –њ–Њ—Б—В—Г–њ–∞—О—В –љ–∞ –≤—Е–Њ–і—Л D0.0, D1.0 –Є D0.1, D1.1 –Љ—Г–ї—М—В–Є–њ–ї–µ–Ї—Б–Њ—А–љ—Л—Е –Љ–Є–Ї—А–Њ—Б—Е–µ–Љ –Є –Ї–Њ–Љ–Љ—Г—В–Є—А—Г—О—В—Б—П –љ–∞ –≤—Л—Е–і—Л –њ–Њ–і —Г–њ—А–∞–≤–ї–µ–љ–Є–µ–Љ —Б–Є–≥–љ–∞–ї–∞ –љ–∞ –≤—Е–Њ–і–µ SED2(AY/AX) –њ—А–Є –љ–∞–ї–Є—З–Є–Є –љ–∞ –і—А—Г–≥–Њ–Љ —Г–њ—А–∞–≤–ї—П—О—Й–µ–Љ –≤—Е–Њ–і–µ SED1(REF) —Г—А–Њ–≤–љ—П 0. –£—Б–ї–Њ–≤–Є—П –Ї–Њ–Љ–Љ—Г—В–∞—Ж–Є–Є —Б–Є–≥–љ–∞–ї–Њ–≤: –њ—А–Є AY/AX=0 –Ї –≤—Л—Е–Њ–і–∞–Љ –њ–Њ–і–Ї–ї—О—З–∞—О—В—Б—П –Ї–∞–љ–∞–ї—Л D0.0, D0.1 –Є, —Б–ї–µ–і–Њ–≤–∞—В–µ–ї—М–љ–Њ, –љ–∞ –∞–і—А–µ—Б–љ—Л–µ –≤—Е–Њ–і—Л –Ю–Ч–£ –њ–Њ—Б—В—Г–њ–∞–µ—В –∞–і—А–µ—Б —Б—В—А–Њ–Ї AX; –њ—А–Є AY/AX=1 –Ї –≤—Л—Е–Њ–і–∞–Љ –њ–Њ–і–Ї–ї—О—З–∞—О—В—Б—П –Ї–∞–љ–∞–ї—Л D1.0, D1.1 –Є –Ї –Ю–Ч–£ –љ–∞–њ—А–∞–≤–ї—П–µ—В—Б—П –Ї–Њ–і –∞–і—А–µ—Б–∞ —Б—В–Њ–ї–±—Ж–Њ–≤ AY.

–°–Є–≥–љ–∞–ї—Л —Г–њ—А–∞–≤–ї–µ–љ–Є—П: REF- –њ—А–Є–Ј–љ–∞–Ї —А–µ–ґ–Є–Љ–∞ —А–µ–≥–µ–љ–µ—А–∞—Ж–Є–Є –Є AY/AX-—Б–Є–≥–љ–∞–ї –Љ—Г–ї—М—В–Є–њ–ї–µ–Ї—Б–Є—А–Њ–≤–∞–љ–Є—П –Ї–∞–љ–∞–ї–Њ–≤, –≤—Л—А–∞–±–∞—В—Л–≤–∞–µ—В –Ї–Њ–љ—В—А–Њ–ї–ї–µ—А.

–Т —А–µ–ґ–Є–Љ–µ —А–µ–≥–µ–љ–µ—А–∞—Ж–Є–Є REF=1 –Є –Љ—Г–ї—М—В–Є–њ–ї–µ–Ї—Б–Њ—А –Ї–Њ–Љ–Љ—Г—В–Є—А—Г–µ—В –љ–∞ –≤—Л—Е–Њ–і—Л –њ—А–Є –Є–Ј–Љ–µ–љ–µ–љ–Є–Є AY/AX –Ї–∞–љ–∞–ї—Л D2.0, D3.0 –Є D2.1, D3.1. –Э–Њ —В–∞–Ї –Ї–∞–Ї —Г–Ї–∞–Ј–∞–љ–љ—Л–µ –Ї–∞–љ–∞–ї—Л –њ–Њ–њ–∞—А–љ–Њ —Б–Њ–µ–і–Є–љ–µ–љ—Л, —В–Њ –љ–∞ —А–µ–Ј—Г–ї—М—В–∞—В –Ї–Њ–Љ–Љ—Г—В–∞—Ж–Є–Є —Б–Є–≥–љ–∞–ї AY/AX –≤–ї–Є—П–љ–Є—П –љ–µ –Њ–Ї–∞–Ј—Л–≤–∞–µ—В: –њ—А–Є –ї—О–±—Л—Е –µ–≥–Њ –Ј–љ–∞—З–µ–љ–Є—П—Е –љ–∞ –≤—Л—Е–Њ–і—Л –Љ—Г–ї—М—В–Є–њ–ї–µ–Ї—Б–Њ—А–∞ –њ–Њ—Б—В—Г–њ–∞—О—В –∞–і—А–µ—Б–∞ —А–µ–≥–µ–љ–µ—А–∞—Ж–Є–Є AR, –≤—Л—А–∞–±–∞—В—Л–≤–∞–µ–Љ—Л–µ —Б—З–µ—В—З–Є–Ї–Њ–Љ –Ї–Њ–љ—В—А–Њ–ї–ї–µ—А–∞. –≠—В–Є —Б–Є–≥–љ–∞–ї—Л –∞–і—А–µ—Б—Г—О—В —В–Њ–ї—М–Ї–Њ —Б—В—А–Њ–Ї–Є, —Б–Є–≥–љ–∞–ї—Л –∞–і—А–µ—Б–∞ —Б—В–Њ–ї–±—Ж–Њ–≤ –≤ —Н—В–Њ–Љ —А–µ–ґ–Є–Љ–µ –љ–∞ –∞–і—А–µ—Б–љ—Л—Е –≤—Е–Њ–і–∞—Е –Њ—В—Б—Г—В—Б—В–≤—Г—О—В.

–Я—А–Є –Њ—В—Б—Г—В—Б—В–≤–Є–Є –Њ–±—А–∞—Й–µ–љ–Є—П –Ї –Ю–Ч–£, –Ю–Ч–£ —А–∞–±–Њ—В–∞–µ—В —В–Њ–ї—М–Ї–Њ –≤ —А–µ–ґ–Є–Љ–µ —А–µ–≥–µ–љ–µ—А–∞—Ж–Є–Є. –° –Ї–∞–ґ–і—Л–Љ —В–∞–Ї—В–Њ–Љ –Ї–Њ–љ—В—А–Њ–ї–ї–µ—А —Д–Њ—А–Љ–Є—А—Г–µ—В —Б–Є–≥–љ–∞–ї—Л RAS, REF –Є –Ї–Њ–і –∞–і—А–µ—Б–∞ –Њ—З–µ—А–µ–і–љ–Њ–є —Б—В—А–Њ–Ї–Є, –Є –Є–љ–Є—Ж–Є–Є—А—Г–µ—В —А–∞–±–Њ—В—Г –Љ–Њ–і—Г–ї—П –њ–∞–Љ—П—В–Є –њ–Њ —Ж–Є–Ї–ї—Г —А–µ–≥–µ–љ–µ—А–∞—Ж–Є–Є.

–Я—А–Њ—Ж–µ—Б—Б —А–µ–≥–µ–љ–µ—А–∞—Ж–Є–Є –њ—А–µ–Ї—А–∞—Й–∞–µ—В—Б—П –њ—А–Є –Њ–±—А–∞—Й–µ–љ–Є–Є –Љ–Є–Ї—А–Њ–њ—А–Њ—Ж–µ—Б—Б–Њ—А–∞ –Ї –Ю–Ч–£, –Є –Ї–Њ–љ—В—А–Њ–ї–ї–µ—А –Њ–±—А–∞–±–∞—В—Л–≤–∞–µ—В —В—А–µ–±–Њ–≤–∞–љ–Є–µ –Љ–Є–Ї—А–Њ–њ—А–Њ—Ж–µ—Б—Б–Њ—А–∞. –Т –Ї–Њ–љ—Ж–µ —Ж–Є–Ї–ї–∞ –Њ–±—А–∞—Й–µ–љ–Є—П –Ї–Њ–љ—В—А–Њ–ї–ї–µ—А –њ–µ—А–µ–≤–Њ–і–Є—В –±–ї–Њ–Ї –Ю–Ч–£ –≤ —А–µ–ґ–Є–Љ —А–µ–≥–µ–љ–µ—А–∞—Ж–Є–Є, –њ—А–Њ–і–Њ–ї–ґ–∞—П —Н—В–Њ—В –њ—А–Њ—Ж–µ—Б—Б —Б –∞–і—А–µ—Б–∞, –љ–∞ –Ї–Њ—В–Њ—А–Њ–Љ –Њ–љ –±—Л–ї –њ—А–µ—А–≤–∞–љ.

–†–µ–≥–µ–љ–µ—А–∞—Ж–Є—П, –Њ—Б—Г—Й–µ—Б—В–≤–ї—П–µ–Љ–∞—П –њ–Њ –Њ–њ–Є—Б–∞–љ–љ–Њ–Љ—Г –∞–ї–≥–Њ—А–Є—В–Љ—Г –љ–∞–Ј—Л–≤–∞–µ—В—Б—П вАЬ –њ—А–Њ–Ј—А–∞—З–љ–Њ–євАЭ: –Њ–љ–∞ –љ–µ–Ј–∞–Љ–µ—В–љ–∞ –і–ї—П –Љ–Є–Ї—А–Њ–њ—А–Њ—Ж–µ—Б—Б–Њ—А–∞ –Є –љ–µ —Б–љ–Є–ґ–∞–µ—В —Б–Ї–Њ—А–Њ—Б—В—М –Њ–±—А–∞–±–Њ—В–Ї–Є –њ—А–Њ–≥—А–∞–Љ–Љ. –£—Б–ї–Њ–≤–Є–µ–Љ –і–ї—П –њ—А–Є–Љ–µ–љ–µ–љ–Є—П —Н—В–Њ–≥–Њ —Б–њ–Њ—Б–Њ–±–∞ —П–≤–ї—П–µ—В—Б—П –љ–∞–ї–Є—З–Є–µ –≤—А–µ–Љ–µ–љ–љ—Л—Е –Є–љ—В–µ—А–≤–∞–ї–Њ–≤ –Љ–µ–ґ–і—Г –і–≤—Г–Љ—П –ї—О–±—Л–Љ–Є –Њ–±—А–∞—Й–µ–љ–Є—П–Љ–Є –Љ–Є–Ї—А–Њ–њ—А–Њ—Ж–µ—Б—Б–Њ—А–∞ –Ї –Ю–Ч–£, –і–Њ—Б—В–∞—В–Њ—З–љ—Л—Е –і–ї—П –њ—А–Њ–≤–µ–і–µ–љ–Є—П –Њ–і–љ–Њ–≥–Њ —Ж–Є–Ї–ї–∞ —А–µ–≥–µ–љ–µ—А–∞—Ж–Є–Є, —В.–µ. —А–µ–≥–µ–љ–µ—А–∞—Ж–Є–Є –њ—А–Є –Њ–±—А–∞—Й–µ–љ–Є–Є –Ї –Љ–Њ–і—Г–ї—О –Ю–Ч–£ –њ–Њ –Њ–і–љ–Њ–Љ—Г –∞–і—А–µ—Б—Г.

–Э–∞–њ—А–Є–Љ–µ—А, –∞–ї–≥–Њ—А–Є—В–Љ–Њ–Љ —А–∞–±–Њ—В—Л –Љ–Є–Ї—А–Њ–њ—А–Њ—Ж–µ—Б—Б–Њ—А–∞ –Ъ580–Т–Ь80 —В–∞–Ї–Є–µ –Є–љ—В–µ—А–≤–∞–ї—Л –њ—А–µ–і—Г—Б–Љ–Њ—В—А–µ–љ—Л: –Љ–Є–љ–Є–Љ–∞–ї—М–љ—Л–є —Ж–Є–Ї–ї –Љ–µ–ґ–і—Г –і–≤—Г–Љ—П –ї—О–±—Л–Љ–Є –Њ–±—А–∞—Й–µ–љ–Є—П–Љ–Є –Ї –њ–∞–Љ—П—В–Є —Б–Њ—Б—В–Њ–Є—В –Є–Ј —В—А–µ—Е —В–∞–Ї—В–Њ–≤—Л—Е –њ–µ—А–Є–Њ–і–Њ–≤.

–Я—А–Є –љ–Њ–Љ–Є–љ–∞–ї—М–љ–Њ–є —З–∞—Б—В–Њ—В–µ –≥–µ–љ–µ—А–∞—В–Њ—А–∞ 18–Ь–У—Ж –і–ї–Є—В–µ–ї—М–љ–Њ—Б—В—М —В–∞–Ї—В–∞ —А–∞–≤–љ–∞ 0.5 –Љ–Ї—Б. –Х—Б–ї–Є —Г—З–µ—Б—В—М, —З—В–Њ –љ–∞ –≤—Л–њ–Њ–ї–љ–µ–љ–Є–µ –Њ–і–љ–Њ–≥–Њ —Ж–Є–Ї–ї–∞ —А–µ–≥–µ–љ–µ—А–∞—Ж–Є–Є –Љ–Є–Ї—А–Њ—Б—Е–µ–Љ –Ъ565–†–£3–У —В—А–µ–±—Г–µ—В—Б—П 370 –љ—Б, —В–Њ –Њ—З–µ–≤–Є–і–љ–∞ –≤–Њ–Ј–Љ–Њ–ґ–љ–Њ—Б—В—М —А–µ–∞–ї–Є–Ј–∞—Ж–Є–Є.

2.1.–Я—А–Є–љ—Ж–Є–њ —А–∞–±–Њ—В—Л –Љ–Є–Ї—А–Њ—Б—Е–µ–Љ—Л –і–Є–љ–∞–Љ–Є—З–µ—Б–Ї–Є—Е –Ю–Ч–£ –Ъ565–†–£3–У

–Т –Љ–Є–Ї—А–Њ—Б—Е–µ–Љ–∞—Е –њ–∞–Љ—П—В–Є –і–Є–љ–∞–Љ–Є—З–µ—Б–Ї–Њ–≥–Њ —В–Є–њ–∞ —Д—Г–љ–Ї—Ж–Є–Є –≠–Я –≤—Л–њ–Њ–ї–љ—П–µ—В —Н–ї–µ–Ї—В—А–Є—З–µ—Б–Ї–Є–є –Ї–Њ–љ–і–µ–љ—Б–∞—В–Њ—А, –Њ–±—А–∞–Ј–Њ–≤–∞–љ–љ—Л–є –≤–љ—Г—В—А–Є –Ь–Ф–Я —Б—В—А—Г–Ї—В—Г—А—Л. –Ш–љ—Д–Њ—А–Љ–∞—Ж–Є—П –њ—А–µ–і—Б—В–∞–≤–ї—П–µ—В—Б—П –≤ –≤–Є–і–µ –Ј–∞—А—П–і–∞: –љ–∞–ї–Є—З–Є–µ –Ј–∞—А—П–і–∞ –љ–∞ –Ї–Њ–љ–і–µ–љ—Б–∞—В–Њ—А–µ —Б–Њ–Њ—В–≤–µ—В—Б—В–≤—Г–µ—В –ї–Њ–≥–Є—З–µ—Б–Ї–Њ–є 1, –Њ—В—Б—Г—В—Б—В–≤–Є–µ-–ї–Њ–≥–Є—З–µ—Б–Ї–Њ–Љ—Г 0. –Я–Њ—Б–Ї–Њ–ї—М–Ї—Г –≤—А–µ–Љ—П —Б–Њ—Е—А–∞–љ–µ–љ–Є—П –Ї–Њ–љ–і–µ–љ—Б–∞—В–Њ—А–Њ–Љ –Ј–∞—А—П–і–∞ –Њ–≥—А–∞–љ–Є—З–µ–љ–Њ, –њ—А–µ–і—Г—Б–Љ–∞—В—А–Є–≤–∞—О—В –њ–µ—А–Є–Њ–і–Є—З–µ—Б–Ї–Њ–µ –≤–Њ—Б—Б—В–∞–љ–Њ–≤–ї–µ–љ–Є–µ (—А–µ–≥–µ–љ–µ—А–∞—Ж–Є—О) –Ј–∞–њ–Є—Б–∞–љ–љ–Њ–є –Є–љ—Д–Њ—А–Љ–∞—Ж–Є–Є. –Ъ—А–Њ–Љ–µ —В–Њ–≥–Њ, –і–ї—П –љ–Є—Е –љ–µ–Њ–±—Е–Њ–і–Є–Љ–∞ —Б–Є–љ—Е—А–Њ–љ–Є–Ј–∞—Ж–Є—П, –Њ–±–µ—Б–њ–µ—З–Є–≤–∞—О—Й–∞—П —В—А–µ–±—Г–µ–Љ—Г—О –њ–Њ—Б–ї–µ–і–Њ–≤–∞—В–µ–ї—М–љ–Њ—Б—В—М –≤–Ї–ї—О—З–µ–љ–Є–є –Є –≤—Л–Ї–ї—О—З–µ–љ–Є–є —Д—Г–љ–Ї—Ж–Є–Њ–љ–∞–ї—М–љ—Л—Е —Г–Ј–ї–Њ–≤.

–Ф–ї—П –Є–Ј–≥–Њ—В–Њ–≤–ї–µ–љ–Є—П –Љ–Є–Ї—А–Њ—Б—Е–µ–Љ –і–Є–љ–∞–Љ–Є—З–µ—Б–Ї–Њ–≥–Њ –Ю–Ч–£ –≤ –Њ—Б–љ–Њ–≤–љ–Њ–Љ –њ—А–Є–Љ–µ–љ—П—О—В n-–Ь–Ф–Я —В–µ—Е–љ–Њ–ї–Њ–≥–Є—О, –Ї–Њ—В–Њ—А–∞—П –њ–Њ–Ј–≤–Њ–ї—П–µ—В –њ–Њ–≤—Л—И–∞—В—М –±—Л—Б—В—А–Њ–і–µ–є—Б—В–≤–Є–µ –Є —Г—А–Њ–≤–µ–љ—М –Є–љ—В–µ–≥—А–∞—Ж–Є–Є –Љ–Є–Ї—А–Њ—Б—Е–µ–Љ, –Њ–±–µ—Б–њ–µ—З–Є–≤–∞—В—М –Љ–∞–ї—Л–µ —В–Њ–Ї–Є —Г—В–µ—З–Ї–Є –Є –Ј–∞ —Н—В–Њ—В —Б—З–µ—В —Г–≤–µ–ї–Є—З–Є–≤–∞—В—М –≤—А–µ–Љ—П —Б–Њ—Е—А–∞–љ–µ–љ–Є—П –Ј–∞—А—П–і–∞ –љ–∞ –Ј–∞–њ–Њ–Љ–Є–љ–∞—О—Й–µ–Љ –Ї–Њ–љ–і–µ–љ—Б–∞—В–Њ—А–µ.

- –≤

—Л—Е–Њ–і

–љ–∞ —В—А–Є —Б–Њ—Б—В–Њ—П–љ–Є—П;

—Л—Е–Њ–і

–љ–∞ —В—А–Є —Б–Њ—Б—В–Њ—П–љ–Є—П;

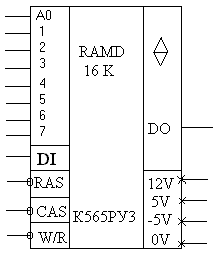

DI- –≤—Е–Њ–і–љ—Л–µ –і–∞–љ–љ—Л–µ; W/R- –Ј–∞–њ–Є—Б—М-—Б—З–Є—В—Л–≤–∞–љ–Є–µ;

DO- –≤—Л—Е–Њ–і–љ—Л–µ –і–∞–љ–љ—Л–µ; A- –∞–і—А–µ—Б;

RAS- —Б—В—А–Њ–± –∞–і—А–µ—Б–∞ —Б—В—А–Њ–Ї–Є;

CAS- —Б—В—А–Њ–± –∞–і—А–µ—Б–∞ —Б—В–Њ–ї–±—Ж–∞;

–Ь–Є–Ї—А–Њ—Б—Е–µ–Љ–∞ –Ъ565–†–£3–У –Є–љ—Д–Њ—А–Љ–∞—Ж–Є–Њ–љ–љ–Њ–є –µ–Љ–Ї–Њ—Б—В—М—О 16–Ъx1–±–Є—В. –Т –µ–µ —Б—В—А—Г–Ї—В—Г—А–љ—Г—О —Б—Е–µ–Љ—Г (–њ—А–Є–ї–Њ–ґ–µ–љ–Є–µ 1) –≤—Е–Њ–і—П—В –≤—Л–њ–Њ–ї–љ–µ–љ–љ—Л–µ –≤ –Њ–і–љ–Њ–Љ –Ї—А–µ–Љ–љ–Є–µ–≤–Њ–Љ –Ї—А–Є—Б—В–∞–ї–ї–µ –Љ–∞—В—А–Є—Ж–∞ –љ–∞–Ї–Њ–њ–Є—В–µ–ї—П, —Б–Њ–і–µ—А–ґ–∞—Й–∞—П 16384 —Н–ї–µ–Љ–µ–љ—В–Њ–≤ –њ–∞–Љ—П—В–Є, —А–∞—Б–њ–Њ–ї–Њ–ґ–µ–љ–љ—Л—Е –љ–∞ –њ–µ—А–µ—Б–µ—З–µ–љ–Є—П—Е 128 —Б—В—А–Њ–Ї –Є 128 —Б—В–Њ–ї–±—Ж–Њ–≤, 128 —Г—Б–Є–ї–Є—В–µ–ї–µ–є —Б—З–Є—В—Л–≤–∞–љ–Є—П –Є —А–µ–≥–µ–љ–µ—А–∞—Ж–Є–Є, –і–µ—И–Є—Д—А–∞—В–Њ—А—Л —Б—В—А–Њ–Ї –Є —Б—В–Њ–ї–±—Ж–Њ–≤, —Г—Б—В—А–Њ–є—Б—В–≤–Њ —Г–њ—А–∞–≤–ї–µ–љ–Є—П, —Г—Б—В—А–Њ–є—Б—В–≤–Њ –≤–≤–Њ–і–∞-–≤—Л–≤–Њ–і–∞ –Є –Љ—Г–ї—М—В–Є–њ–ї–µ–Ї—Б–љ—Л–є —А–µ–≥–Є—Б—В—А –∞–і—А–µ—Б–∞.

–Ь–∞—В—А–Є—Ж–∞ –љ–∞–Ї–Њ–њ–Є—В–µ–ї—П —А–∞–Ј–і–µ–ї–µ–љ–∞ –љ–∞ –і–≤–µ —З–∞—Б—В–Є –њ–Њ 64x64 –≠–Я –≤ –Ї–∞–ґ–і–Њ–є. –Ь–µ–ґ–і—Г –љ–Є–Љ–Є —А–∞–Ј–Љ–µ—Й–µ–љ—Л —Г—Б–Є–ї–Є—В–µ–ї–Є, —В–∞–Ї —З—В–Њ –Ї–∞–ґ–і—Л–є —Б—В–Њ–ї–±–µ—Ж —Б–Њ—Б—В–Њ–Є—В –Є–Ј –і–≤—Г—Е —Б–µ–Ї—Ж–Є–є, –њ–Њ–і–Ї–ї—О—З–µ–љ–љ—Л—Е –Ї —А–∞–Ј–љ—Л–Љ –њ–ї–µ—З–∞–Љ —Г—Б–Є–ї–Є—В–µ–ї—П (–њ—А–Є–ї–Њ–ґ–µ–љ–Є–µ 2).

–≠–ї–µ–Љ–µ–љ—В –њ–∞–Љ—П—В–Є —Б–Њ–±—А–∞–љ –њ–Њ –Њ–і–љ–Њ-—В—А–∞–љ–Ј–Є—Б—В–Њ—А–љ–Њ–є —Б—Е–µ–Љ–µ –Є –≤–Ї–ї—О—З–∞–µ—В –Ї–Њ–љ–і–µ–љ—Б–∞—В–Њ—А Cij. –Ґ—А–∞–љ–Ј–Є—Б—В–Њ—А –≤—Л–њ–Њ–ї–љ—П–µ—В —Д—Г–љ–Ї—Ж–Є–Є –Ї–ї—О—З–∞: –њ—А–Є —Б–Є–≥–љ–∞–ї–µ –љ–∞ –∞–і—А–µ—Б–љ–Њ–є —И–Є–љ–µ —Б—В—А–Њ–Ї–Є Xi=1 –Њ–љ –Њ—В–Ї—А—Л–≤–∞–µ—В—Б—П –Є —Б–Њ–µ–і–Є–љ—П–µ—В –Ї–Њ–љ–і–µ–љ—Б–∞—В–Њ—А Cij —Б j-—А–∞–Ј—А—П–і–љ–Њ–є —И–Є–љ–Њ–є. –Я—А–µ–і–≤–∞—А–Є—В–µ–ї—М–љ–Њ –≤ –њ–∞—Г–Ј–∞—Е –Љ–µ–ґ–і—Г –Њ–±—А–∞—Й–µ–љ–Є—П–Љ–Є –Ї –љ–∞–Ї–Њ–њ–Є—В–µ–ї—О –µ–Љ–Ї–Њ—Б—В–Є –њ–Њ–ї—Г—И–Є–љ –°–®–Р –Є –°–®–С –Ј–∞—А—П–ґ–∞–µ—В –Є—Б—В–Њ—З–љ–Є–Ї –љ–∞–њ—А—П–ґ–µ–љ–Є—П UO —З–µ—А–µ–Ј –Њ—В–Ї—А—Л—В—Л–µ –Ї–ї—О—З–µ–≤—Л–µ —В—А–∞–љ–Ј–Є—Б—В–Њ—А—Л VT5 –Є VT6. –Я—А–Є –Њ–±—А–∞—Й–µ–љ–Є–Є –Ї –љ–∞–Ї–Њ–њ–Є—В–µ–ї—О —Н—В–Є —В—А–∞–љ–Ј–Є—Б—В–Њ—А—Л –Ј–∞–Ї—А—Л–≤–∞—О—В—Б—П –Є –Є–Ј–Њ–ї–Є—А—Г—О—В –њ–Њ–ї—Г—И–Є–љ—Л Aj –Є Bj –Њ—В –Є—Б—В–Њ—З–љ–Є–Ї–∞ –љ–∞–њ—А—П–ґ–µ–љ–Є—П U–Ю

–Ч–∞–њ–Њ–Љ–Є–љ–∞—О—Й–Є–є –Ї–Њ–љ–і–µ–љ—Б–∞—В–Њ—А –°ij –≤—Л–±—А–∞–љ–љ–Њ–≥–Њ –≠–Я –њ–Њ–і–Ї–ї—О—З–∞–µ—В—Б—П —З–µ—А–µ–Ј –Њ—В–Ї—А—Л—В—Л–є —В—А–∞–љ–Ј–Є—Б—В–Њ—А Vtij –Ї –њ–Њ–ї—Г—И–Є–љ–µ Aj –Є –Є–Ј–Љ–µ–љ—П–µ—В –µ–µ –њ–Њ—В–µ–љ—Ж–Є–∞–ї. –≠—В–Њ –Є–Ј–Љ–µ–љ–µ–љ–Є–µ –љ–µ–Ј–љ–∞—З–Є—В–µ–ї—М–љo, —ВпАЃ–ЇпАЃ –µ–Љ–Ї–Њ—Б—В—М –Ј–∞–њ–Њ–Љ–Є–љ–∞—О—Й–µ–≥–Њ –Ї–Њ–љ–і–µ–љ—Б–∞—В–Њ—А–∞пАђ —А–∞–≤–љ–∞—П 0пАЃ1-0пАЃ2 –њ–§пАђ –Љ–љ–Њ–≥–Њ –Љ–µ–љ—М—И–µ –µ–Љ–Ї–Њ—Б—В–Є —И–Є–љ—ЛпАЃ –Я–Њ—Н—В–Њ–Љ—Г –і–ї—П –Є–љ–і–Є–Ї–∞—Ж–Є–Є –Љ–∞–ї–Њ–≥–Њ –Є–Ј–Љ–µ–љ–µ–љ–Є—П –њ–Њ—В–µ–љ—Ж–Є–∞–ї–∞ —И–Є–љ—Л –њ—А–Є —Б—З–Є—В—Л–≤–∞–љ–Є–Є –Є–љ—Д–Њ—А–Љ–∞—Ж–Є–Є –њ—А–Є–Љ–µ–љ–µ–љ –≤—Л—Б–Њ–Ї–Њ —З—Г–≤—Б—В–≤–Є—В–µ–ї—М–љ—Л–є –і–Є—Д—Д–µ—А–µ–љ—Ж–Є–∞–ї—М–љ—Л–є —Г—Б–Є–ї–Є—В–µ–ї—М —В—А–Є–≥–µ—А–љ–Њ–≥–Њ —В–Є–њ–∞ –љ–∞ —В—А–∞–љ–Ј–Є—Б—В–Њ—А–∞—Е VT1-VT4пАђ –≤–Ї–ї—О—З–µ–љ–љ—Л–є –≤ —Б–µ—А–µ–і–Є–љ—Г –†–®пАЃ

–Ъ—А–Њ–Љ–µ –Љ–∞—Б—Б–Є–≤–∞ –≠–Я –Є —Г—Б–Є–ї–Є—В–µ–ї–µ–єпАђ –Љ–∞—В—А–Є—Ж–∞ –Є–Љ–µ–µ—В –≤ —Б–≤–Њ–µ–є —Б—В—А—Г–Ї—В—Г—А–µ –Њ–њ–Њ—А–љ—Л–µ —Н–ї–µ–Љ–µ–љ—В—Л (–≠–Ю) –њ–Њ –Њ–і–љ–Њ–Љ—Г –µ–ї–µ–Љ–µ–љ—В—Г –≤ –Ї–∞–ґ–і–Њ–є –њ–Њ–ї—Г—И–Є–љ–µпАЃ –≠—В–Є —Н–ї–µ–Љ–µ–љ—В—Л –≤–Ї–∞–ґ–і–Њ–є –њ–Њ–ї–Њ–≤–Є–љ–µ –Љ–∞—В—А–Є—Ж—Л —Б–Њ—Б—В–Њ–≤–ї—П—О—В –Њ–њ–Њ—А–љ—Г—О —Б—В—А–Њ–Ї—Г (–Ю–°)пАЃ

–Ю–њ–Њ—А–љ—Л–є —Н–ї–µ–Љ–µ–љ—В –њ–Њ—Б—В—А–Њ–µ–љ –∞–љ–∞–ї–Њ–≥–Є—З–љ–Њ –Ј–∞–њ–Њ–Љ–Є–љ–∞—О—Й–µ–Љ—ГпАЃ –Х–≥–Њ –љ–∞–Ј–љ–∞—З–µ–љ–Є–µ —Б–Њ—Б—В–Њ–Є—В –≤ –њ–Њ–і–і–µ—А–ґ–∞–љ–Є–Є –Њ–њ–Њ—А–љ–Њ–≥–Њ –љ–∞–њ—А—П–ґ–µ–љ–Є—П UOпАђ c –Ї–Њ—В–Њ—А—Л–Љ —Г—Б–Є–ї–Є—В–µ–ї—М —Б—А–∞–≤–љ–Є–≤–∞–µ—В –њ–Њ—В–µ–љ—Ж–Є–∞–ї –њ–Њ–ї—Г—И–Є–љ—Л —Б –≤—Л–±—А–∞–љ–љ—Л–Љ –≠–Я –Є —А–µ–∞–≥–Є—А—Г–µ—В –љ–∞ –њ–Њ–ї—Г—З–∞—О—Й—Г—О—Б—П –њ—А–Є —Б—А–∞–≤–љ–µ–љ–Є–Є —А–∞–Ј–љ–Њ—Б—В—М

–њ–Њ—В–µ–љ—Ж–Є–∞–ї–Њ–≤ –њ–Њ–ї–Њ–ґ–Є—В–µ–ї—М–љ–Њ–≥–Њ –Є –Њ—В—А–Є—Ж–∞—В–µ–ї—М–љ–Њ–≥–Њ –Ј–љ–∞–Ї–∞ –≤ –Ј–∞–≤–Є—Б–Є–Љ–Њ—Б—В–Є –Њ—В —Б—З–Є—В—Л–≤–∞–µ–Љ–Њ–≥–Њ —Г—А–Њ–≤–љ—ПпАЃ

–≠—В–∞ –Њ–њ–µ—А–∞—Ж–Є—П –њ—А–Њ–Є—Б—Е–Њ–і–Є—В —Б–ї–µ–і—Г—О—Й–µ–Љ –Њ–±—А–∞–Ј–Њ–Љ: –µ—Б–ї–Є –≤—Л–±—А–∞–љ–∞ –і–ї—П –Њ–±—А–∞—Й–µ–љ–Є—П —Б—В—А–Њ–Ї–∞ –≤–µ—А—Е–љ–µ–є –њ–Њ–ї—Г–Љ–∞—В—А–Є—Ж—Л Xi пАђ —В–Њ —Б–Є–≥–љ–∞–ї –Р6 —Б—В–∞—А—И–µ–≥–Њ —А–∞–Ј—А—П–і–∞ –Ї–Њ–і–∞ –∞–і—А–µ—Б–∞ —Б—В—А–Њ–Ї–Є –Ї–Њ–Љ–Љ—Г—В–Є—А—Г–µ—В –≤ —Б–µ–ї–µ–Ї—В–Њ—А–µ –Њ–њ–Њ—А–љ–Њ–є —Б—В—А–Њ–Ї–Є —Ж–µ–њ—М —З–µ—А–µ–Ј –Ї–ї—О—З–µ–≤–Њ–є —В—А–∞–љ–Ј–Є—Б—В–Њ—А VT12 –і–ї—П —Б–Є–≥–љ–∞–ї–∞ F2 –Ї –Ю–°2пАђ —А–∞—Б–њ–Њ–ї–Њ–ґ–µ–љ–љ–Њ–є –≤ –љ–Є–ґ–љ–µ–є –њ–Њ–ї—Г–Љ–∞—В—А–Є—Ж–µпАЃ –Ґ–∞–Ї–Є–Љ –Њ–±—А–∞–Ј–Њ–ЉпАђ –≤ –Ї–∞–ґ–і–Њ–Љ –Є–Ј 128 —Б—В–Њ–ї–±—Ж–Њ–≤ –Ї —Г—Б–Є–ї–Є—В–µ–ї—О —Б —А–∞–Ј–љ—Л—Е —Б—В–Њ—А–Њ–љ –њ–Њ–і–Ї–ї—О—З–µ–љ—Л –≠–Я –Є –≠–ЮпАЃ –Я–Њ—Б–Ї–Њ–ї—М–Ї—Г –њ–Њ—В–µ–љ—Ж–Є–∞–ї –њ–Њ–ї—Г—И–Є–љ—Л —Б –≠–Я –Њ—В–ї–Є—З–∞–µ—В—Б—П –Њ—В –Њ–њ–Њ—А–љ–Њ–≥–ЊпАђ –≤ –њ—А–Њ–≤–Њ–і–Є–Љ–Њ—Б—В–Є —В—А–∞–љ–Ј–Є—Б—В–Њ—А–Њ–≤ —А–∞–Ј–љ—Л—Е –њ–ї–µ—З —Г—Б–Є–ї–Є—В–µ–ї—П-—В—А–Є–≥–≥–µ—А–∞ –њ–Њ—П–≤–ї—П–µ—В—Б—П –∞—Б–Є–Љ–Љ–µ—В—А–Є—ПпАђ –Ї–Њ—В–Њ—А–∞—П –њ—А–Є –≤–Ї–ї—О—З–µ–љ–Є–Є —Ж–µ–њ–Є –µ–≥–Њ –њ–Є—В–∞–љ–Є—П —Б–Є–≥–љ–∞–ї–Њ–Љ F3 –≤—Л–Ј—Л–≤–∞–µ—В –Њ–њ—А–Њ–≥–Є–і–Њ–≤–∞–љ–Є–µ —В—А–Є–≥–≥–µ—А–∞ –њ–Њ –њ—А–µ–Њ–±–ї–∞–і–∞—О—Й–µ–Љ—Г —Г—А–Њ–≤–љ—ОпАЃ –Т –Є—В–Њ–≥–µ –љ–∞ –≤—Л—Е–Њ–і–∞—Е-–≤—Е–Њ–і–∞—Е –Р –Є –Т —В—А–Є–≥–≥–µ—А–∞ —Д–Њ—А–Љ–Є—А—Г—О—В—Б—П –њ–Њ–ї–љ—Л–µ —Г—А–Њ–≤–љ–Є 1 –Є 0пАЃ –Ґ–Њ—В –Є–Ј —Б–Є–≥–љ–∞–ї–Њ–≤пАђ –Ї–Њ—В–Њ—А—Л–є –Њ—В—А–∞–ґ–∞–µ—ВпАђ —Б—З–Є—В—Л–≤–∞–µ–Љ—Г—О –Є–љ—Д–Њ—А–Љ–∞—Ж–Є—ОпАђ –≤ –і–∞–љ–љ–Њ–Љ –њ—А–Є–Љ–µ—А–µ —Б–Є–≥–љ–∞–ї —Б –њ–ї–µ—З–∞ –РпАђ –Ї–Њ–Љ–Љ—Г—В–Є—А—Г–µ—В—Б—П –љ–∞ –≤—Е–Њ–і —Г—Б—В—А–Њ–є—Б—В–≤–∞ –≤—Л–≤–Њ–і–∞ —З–µ—А–µ–Ј –Ї–ї—О—З–µ–≤—Л–µ —В—А–∞–љ–Ј–Є—Б—В–Њ—А—Л VT7пАђVT9 –Є VT10пАђ –Њ—В–Ї—А—Л–≤–∞–µ–Љ—Л–µ —Б–Є–≥–љ–∞–ї–∞–Љ–Є –Р6пАђ F4 –Є YjпАЃ –Ю—З–µ–≤–Є–і–љ–ЊпАђ —Б—З–Є—В–∞–љ –Љ–Њ–ґ–µ—В –±—Л—В—М —В–Њ–ї—М–Ї–Њ –Њ–і–Є–љ —Б–Є–≥–љ–∞–ї —Б –≤—Л–±—А–∞–љ–љ–Њ–≥–Њ –і–µ—И–Є—Д—А–∞—В–Њ—А–Њ–Љ —Б—В–Њ–ї–±—Ж–∞ : Yj=1пАЃ –£ –Њ—Б—В–∞–ї—М–љ—Л—Е —Б—В–Њ–ї–±—Ж–Њ–≤ –Ї–ї—О—З–Є VT10 –Ј–∞–Ї—А—Л—В—Л пАЃ –°–Є–≥–љ–∞–ї F4 –Ј–∞–≤–Є—Б–Є—В –Њ—В –љ–∞–ї–Є—З–Є—П —Б–Є–≥–љ–∞–ї–∞ CAS: –њ—А–Є –Њ—В—Б—Г—В—Б—В–≤–Є–Є –њ–Њ—Б–ї–µ–і–љ–µ–≥–Њ –Њ–љ –љ–µ —Д–Њ—А–Љ–Є—А—Г–µ—В—Б—П –Є –Ї–ї—О—З VT9 –Ј–∞–Ї—А—Л—ВпАЃ

–°–Є–≥–љ–∞–ї –љ–∞ –≤—Е–Њ–і–µ-–≤—Л—Е–Њ–і–µ –Р —В—А–Є–≥–≥–µ—А–∞-—Г—Б–Є–ї–Є—В–µ–ї—П –≤—Л–њ–Њ–ї–љ—П–µ—В —В–∞–Ї–ґ–µ —Д—Г–љ–Ї—Ж–Є—О –≤–Њ—Б—Б—В–∞–љ–Њ–≤–ї–µ–љ–Є—П —Г—А–Њ–≤–љ—П –Ј–∞—А—П–і–∞ –Ј–∞–њ–Њ–Љ–Є–љ–∞—О—Й–µ–≥–Њ –Ї–Њ–љ–і–µ–љ—Б–∞—В–Њ—А–∞ Cij , —В.–µ. —Д—Г–љ–Ї—Ж–Є—О —А–µ–≥–µ–љ–µ—А–∞—Ж–Є–Є –Є–љ—Д–Њ—А–Љ–∞—Ж–Є–Є. –Я—А–Є—З–µ–Љ —Н—В–∞ –Њ–њ–µ—А–∞—Ж–Є—П –њ—А–Њ–Є—Б—Е–Њ–і–Є—В –≤–Њ –≤—Б–µ—Е –≠–Я –≤—Л–±—А–∞–љ–љ–Њ–є —Б—В—А–Њ–Ї–Є –Њ–і–љ–Њ–≤—А–µ–Љ–µ–љ–љ–Њ.

–Ґ–∞–Ї–Є–Љ –Њ–±—А–∞–Ј–Њ–Љ, –њ—А–Є –Ї–∞–ґ–і–Њ–Љ –Њ–±—А–∞—Й–µ–љ–Є–Є –Ї –Љ–∞—В—А–Є—Ж–µ –і–ї—П —Б—З–Є—В—Л–≤–∞–љ–Є—П –Є–љ—Д–Њ—А–Љ–∞—Ж–Є–Є –∞–≤—В–Њ–Љ–∞—В–Є—З–µ—Б–Ї–Є –Њ—Б—Г—Й–µ—Б—В–≤–ї—П–µ—В—Б—П —А–µ–≥–µ–љ–µ—А–∞—Ж–Є—П –Є–љ—Д–Њ—А–Љ–∞—Ж–Є–Є –≤–Њ –≤—Б–µ—Е –≠–Я, –њ—А–Є–љ–∞–і–ї–µ–ґ–∞—Й–Є—Е –≤—Л–±—А–∞–љ–љ–Њ–є —Б—В—А–Њ–Ї–µ.

–Ф–ї—П –∞–і—А–µ—Б–∞—Ж–Є–Є 16 –Ъ —Н–ї–µ–Љ–µ–љ—В–Њ–≤ –њ–∞–Љ—П—В–Є –љ–µ–Њ–±—Е–Њ–і–Є–Љ 16-—А–∞–Ј—А—П–і–љ—Л–є –Ї–Њ–і, –∞ —Г –Љ–Є–Ї—А–Њ—Б—Е–µ–Љ—Л —В–Њ–ї—М–Ї–Њ –≤–Њ—Б–µ–Љ—М –∞–і—А–µ—Б–љ—Л—Е –≤—Е–Њ–і–Њ–≤. –° —Ж–µ–ї—М—О —Г–Љ–µ–љ—М—И–µ–љ–Є—П —З–Є—Б–ї–∞ –љ–µ–Њ–±—Е–Њ–і–Є–Љ—Л—Е –≤—Л–≤–Њ–і–Њ–≤ –Ї–Њ—А–њ—Г—Б–∞ –≤ –Љ–Є–Ї—А–Њ—Б—Е–µ–Љ–∞—Е –і–Є–љ–∞–Љ–Є—З–µ—Б–Ї–Њ–≥–Њ –Ю–Ч–£ –Ї–Њ–і –∞–і—А–µ—Б–∞ –≤–≤–Њ–і—П—В –њ–Њ —З–∞—Б—В—П–Љ: –≤–љ–∞—З–∞–ї–µ —Б–µ–Љ—М –Љ–ї–∞–і—И–Є—Е —А–∞–Ј—А—П–і–Њ–≤ –Р–Ю-–Р7, —Б–Њ–њ—А–Њ–≤–Њ–ґ–і–∞—П –Є—Е —Б—В—А–Њ–±–Є—А—Г—О—Й–Є–Љ —Б–Є–≥–љ–∞–ї–Њ–Љ RAS, –Ј–∞—В–µ–Љ —Б–µ–Љ—М —Б—В–∞—А—И–Є—Е —А–∞–Ј—А—П–і–Њ–≤ –Р8-–Р15 —Б–Њ —Б—В—А–Њ–±–Є—А—Г—О—Й–Є–Љ —Б–Є–≥–љ–∞–ї–Њ–Љ CAS. –Т–љ—Г—В—А–Є –Љ–Є–Ї—А–Њ—Б—Е–µ–Љ—Л –Ї–Њ–і—Л –∞–і—А–µ—Б–∞ —Б—В—А–Њ–Ї –Є —Б—В–Њ–ї–±—Ж–Њ–≤

—Д–Є–Ї—Б–Є—А—Г—О—В—Б—П –љ–∞ –∞–і—А–µ—Б–љ–Њ–Љ —А–µ–≥–Є—Б—В—А–µ, –Ј–∞—В–µ–Љ –і–µ—И–Є—Д—А—Г—О—В—Б—П –Є –Њ—Б—Г—Й–µ—Б—В–≤–ї—П—О—В –≤—Л–±–Њ—А–Ї—Г –∞–і—А–µ—Б—Г–µ–Љ–Њ–≥–Њ –≠–Я.

–Ґ–∞–±–ї–Є—Ж–∞ –Є—Б—В–Є–љ–љ–Њ—Б—В–Є –Љ–Є–Ї—А–Њ—Б—Е–µ–Љ—Л –Ъ565–†–£3–У

RAS |

CAS |

W/R |

A |

DI |

DO |

–†–µ–ґ–Є–Љ —А–∞–±–Њ—В—Л |

|

1 1 0 0 0 0 |

1 0 1 0 0 0 |

–• –• –• 0 0 1 |

–• –• –Р –Р –Р –Р |

–• –• –• 0 1 –• |

Z Z Z Z Z D |

–•—А–∞–љ–µ–љ–Є–µ –•—А–∞–љ–µ–љ–Є–µ –†–µ–≥–µ–љ–µ—А–∞—Ж–Є—П –Ч–∞–њ–Є—Б—М 0 –Ч–∞–њ–Є—Б—М 1 –°—З–Є—В—Л–≤–∞–љ–Є–µ |

–Ф–ї—П —Д–Њ—А–Љ–Є—А–Њ–≤–∞–љ–Є—П –≤–љ—Г—В—А–µ–љ–љ–Є—Е —Б–Є–≥–љ–∞–ї–Њ–≤ F1-F4, —Г–њ—А–∞–≤–ї—П—О—Й–Є—Е –≤–Ї–ї—О—З–µ–љ–Є–µ–Љ –Є –≤—Л–Ї–ї—О—З–µ–љ–Є–µ–Љ –≤ –Њ–њ—А–µ–і–µ–ї–µ–љ–љ–Њ–є –њ–Њ—Б–ї–µ–і–Њ–≤–∞—В–µ–ї—М–љ–Њ—Б—В–Є —Д—Г–љ–Ї—Ж–Є–Њ–љ–∞–ї—М–љ—Л—Е —Г–Ј–ї–Њ–≤ –Љ–Є–Ї—А–Њ—Б—Е–µ–Љ—Л, –≤ –µ–µ —Б—В—А—Г–Ї—В—Г—А–µ –њ—А–µ–і—Г—Б–Љ–Њ—В—А–µ–љ–Њ —Г—Б—В—А–Њ–є—Б—В–≤–Њ —Г–њ—А–∞–≤–ї–µ–љ–Є—П, –і–ї—П –Ї–Њ—В–Њ—А–Њ–≥–Њ –≤—Е–Њ–і–љ—Л–Љ–Є —П–≤–ї—П—О—В—Б—П —Б–Є–≥–љ–∞–ї—Л RAS,CAS,W/R.

–£—Б—В—А–Њ–є—Б—В–≤–Њ –≤–≤–Њ–і–∞-–≤—Л–≤–Њ–і–∞ –Њ–±–µ—Б–њ–µ—З–Є–≤–∞–µ—В –≤–≤–Њ–і –Њ–і–љ–Њ–≥–Њ –±–Є—В–∞ –Є–љ—Д–Њ—А–Љ–∞—Ж–Є–Є DO –≤ —А–µ–ґ–Є–Љ–µ —Б—З–Є—В—Л–≤–∞–љ–Є—П –Є –≤–≤–Њ–і –Њ–і–љ–Њ–≥–Њ –±–Є—В–∞ –Є–љ—Д–Њ—А–Љ–∞—Ж–Є–Є DI —Б –µ–µ —Д–Є–Ї—Б–∞—Ж–Є–µ–є —Б –њ–Њ–Љ–Њ—Й—М—О —В—А–Є–≥–≥–µ—А–∞-–Ј–∞—Й–µ–ї–Ї–Є –≤ —А–µ–ґ–Є–Љ–µ –Ј–∞–њ–Є—Б–Є. –Т–Њ –≤—Б–µ—Е —А–µ–ґ–Є–Љ–∞—Е, –Ї—А–Њ–Љ–µ —А–µ–ґ–Є–Љ–∞ —Б—З–Є—В—Л–≤–∞–љ–Є—П –≤—Л—Е–Њ–і –њ—А–Є–љ–Є–Љ–∞–µ—В –≤—Л—Б–Њ–Ї–Њ–Њ–Љ–љ–Њ–µ (—В—А–µ—В—М–µ) —Б–Њ—Б—В–Њ—П–љ–Є–µ. –Э–∞–ї–Є—З–Є–µ —Г –≤—Л—Е–Њ–і–∞ –≤—Л—Б–Њ–Ї–Њ–Њ–Љ–љ–Њ–≥–Њ —Б–Њ—Б—В–Њ—П–љ–Є—П –њ–Њ–Ј–≤–Њ–ї—П–µ—В –Њ–±—К–µ–і–Є–љ—П—В—М –Є–љ—Д–Њ—А–Љ–∞—Ж–Є–Њ–љ–љ—Л–µ –≤—Е–Њ–і –Є –≤—Л—Е–Њ–і –њ—А–Є –њ–Њ–і–Ї–ї—О—З–µ–љ–Є–Є –Љ–Є–Ї—А–Њ—Б—Е–µ–Љ—Л –Ї –Њ–±—Й–µ–є –Є–љ—Д–Њ—А–Љ–∞—Ж–Є–Њ–љ–љ–Њ–є —И–Є–љ–µ.

–Я–Њ –≤—Е–Њ–і–∞–Љ –Є –≤—Л—Е–Њ–і—Г –Љ–Є–Ї—А–Њ—Б—Е–µ–Љ–∞ –Ъ565–†–£3–У —Б–Њ–≤–Љ–µ—Б—В–Є–Љ–∞ —Б –Ґ–Ґ–Ы –Љ–Є–Ї—А–Њ—Б—Е–µ–Љ–∞–Љ–Є, —З—В–Њ –Њ–Ј–љ–∞—З–∞–µ—В —Б–Њ–Њ—В–≤–µ—В—Б—В–≤–Є–µ –Є—Е –≤—Е–Њ–і–љ—Л—Е –Є –≤—Л—Е–Њ–і–љ—Л—Е —Б–Є–≥–љ–∞–ї–Њ–≤ –Ґ–Ґ–Ы —Г—А–Њ–≤–љ—П–Љ.

–Ь–Є–Ї—А–Њ—Б—Е–µ–Љ—Л –і–Є–љ–∞–Љ–Є—З–µ—Б–Ї–Є—Е –Ю–Ч–£ —А–∞–±–Њ—В–∞—О—В –≤ —Б–ї–µ–і—Г—О—Й–Є—Е —А–µ–ґ–Є–Љ–∞—Е: –Ј–∞–њ–Є—Б–Є, —Б—З–Є—В—Л–≤–∞–љ–Є—П, —Б—З–Є—В—Л–≤–∞–љ–Є—П-–Љ–Њ–і–Є—Д–Є–Ї–∞—Ж–Є—П-–Ј–∞–њ–Є—Б–Є, —Б—В—А–∞–љ–Є—З–љ–Њ–є –Ј–∞–њ–Є—Б–Є, —Б—В—А–∞–љ–Є—З–љ–Њ–≥–Њ —Б—З–Є—В—Л–≤–∞–љ–Є—П, —А–µ–≥–µ–љ–µ—А–∞—Ж–Є–Є.

–Ф–ї—П –Њ–±—А–∞—Й–µ–љ–Є—П –Ї –Љ–Є–Ї—А–Њ—Б—Е–µ–Љ–µ –і–ї—П –Ј–∞–њ–Є—Б–Є –Є —Б—З–Є—В—Л–≤–∞–љ–Є—П –Є–љ—Д–Њ—А–Љ–∞—Ж–Є–Є –љ–µ–Њ–±—Е–Њ–і–Є–Љ–Њ –њ–Њ–і–∞—В—М (–њ—А–Є–ї–Њ–ґ–µ–љ–Є–µ 3 –∞) –Ї–Њ–і –∞–і—А–µ—Б–∞ —Б—В—А–Њ–Ї –Р0-–Р7 –Њ–і–љ–Њ–≤—А–µ–Љ–µ–љ–љ–Њ —Б –љ–Є–Љ –Є–ї–Є —Б –љ–µ–Ї–Њ—В–Њ–є (–љ–µ —А–µ–Ї–Њ–Љ–µ–љ–і—Г–µ—В—Б—П)

–Ј–∞–і–µ—А–ґ–Ї–Њ–є —Б–Є–≥–љ–∞–ї RAS, –Ј–∞—В–µ–Љ —Б –љ–Њ—А–Љ–Є—А–Њ–≤–∞–љ–љ–Њ–є –Ј–∞–і–µ—А–ґ–Ї–Њ–є –љ–∞ –≤—А–µ–Љ—П —Г–і–µ—А–ґ–∞–љ–Є—П –∞–і—А–µ—Б–∞ —Б—В—А–Њ–Ї –Њ—В–љ–Њ—Б–Є—В–µ–ї—М–љ–Њ —Б–Є–≥–љ–∞–ї–∞ RAS –і–Њ–ї–ґ–µ–љ –±—Л—В—М –њ–Њ–і–∞–љ –Ї–Њ–і –∞–і—А–µ—Б–∞ —Б—В–Њ–ї–±—Ж–Њ–≤ –Є —З–µ—А–µ–Ј –≤—А–µ–Љ—П –Є —З–µ—А–µ–Ј –≤—А–µ–Љ—П —Г—Б—В–∞–љ–Њ–≤–ї–µ–љ–Є—П t—Г—Б –∞ CAS-—Б–Є–≥–љ–∞–ї CAS.

–Ъ –Љ–Њ–Љ–µ–љ—В—Г –њ–Њ–і–∞—З–Є –Ї–Њ–і–∞ –∞–і—А–µ—Б–∞ —Б—В–Њ–ї–±—Ж–Њ–≤ –љ–∞ –≤—Е–Њ–і DI –њ–Њ–і–≤–Њ–і—П—В –Ј–∞–њ–Є—Б—Л–≤–∞–µ–Љ—Л–є –±–Є—В –Є–љ—Д–Њ—А–Љ–∞—Ж–Є–Є, –Ї–Њ—В–Њ—А—Л–є —Б–Є–≥–љ–∞–ї–Њ–Љ W/R –њ—А–Є –љ–∞–ї–Є—З–Є–Є CAS=0 —Д–Є–Ї—Б–Є—А—Г–µ—В—Б—П –љ–∞ –≤—Е–Њ–і–љ–Њ–Љ —В—А–Є–≥–≥–µ—А–µ-–Ј–∞—Й–µ–ї–Ї–µ. –°–Є–≥–љ–∞–ї –Ј–∞–њ–Є—Б–Є W/R –Љ–Њ–ґ–µ—В –±—Л—В—М –њ–Њ–і–∞–љ —Г—А–Њ–≤–љ–µ–Љ –Є–ї–Є –Є–Љ–њ—Г–ї—М—Б–Њ–Љ. –Т –њ–Њ—Б–ї–µ–і–љ–µ–Љ —Б–ї—Г—З–∞–µ –Њ–љ –і–Њ–ї–ґ–µ–љ –Є–Љ–µ—В—М –і–ї–Є—В–µ–ї—М–љ–Њ—Б—В—М –љ–µ –Љ–µ–љ–µ–µ –Њ–њ—А–µ–і–µ–ї–µ–љ–љ–Њ–≥–Њ –њ–∞—А–∞–Љ–µ—В—А–Њ–Љ пБіWR –Ј–љ–∞—З–µ–љ–Є—П. –Х—Б–ї–Є —Б–Є–≥–љ–∞–ї –Ј–∞–њ–Є—Б–Є –њ–Њ–і–∞–љ —Г—А–Њ–≤–љ–µ–Љ, —В–Њ —Д–Є–Ї—Б–∞—Ж–Є—О DI —В—А–Є–≥–≥–µ—А–Њ–Љ-–Ј–∞—Й–µ–ї–Ї–Њ–є –њ—А–Њ–Є–Ј–≤–Њ–і–Є—В –Њ—В—А–Є—Ж–∞—В–µ–ї—М–љ—Л–є –њ–µ—А–µ–њ–∞–і —Б–Є–≥–љ–∞–ї–∞ CAS (–њ—А–Є –љ–∞–ї–Є—З–Є–Є RAS=0). –Я–Њ –Њ–Ї–Њ–љ—З–∞–љ–Є–Є –Ј–∞–њ–Є—Б–Є –і–Њ–ї–ґ–љ–∞ –±—Л—В—М –≤—Л–і–µ—А–ґ–∞–љ–∞ –њ–∞—Г–Ј–∞ пБіRAS, —А–∞–≤–љ–∞—П –Є–љ—В–µ—А–≤–∞–ї—Г –Љ–µ–ґ–і—Г —Б–Є–≥–љ–∞–ї–∞–Љ–Є RAS, –і–ї—П –≤–Њ—Б—Б—В–∞–љ–Њ–≤–ї–µ–љ–Є—П —Б–Њ—Б—В–Њ—П–љ–Є—П –≤–љ—Г—В—А–µ–љ–љ–Є—Е —Ж–µ–њ–µ–є –Љ–Є–Ї—А–Њ—Б—Е–µ–Љ—Л.

–Т –∞–љ–∞–ї–Њ–≥–Є—З–љ–Њ–Љ –њ–Њ—А—П–і–Ї–µ –і–Њ–ї–ґ–љ—Л –±—Л—В—М –њ–Њ–і–∞–љ—Л –∞–і—А–µ—Б–љ—Л–µ –Є —Г–њ—А–∞–≤–ї—П—О—Й–Є–µ —Б–Є–≥–љ–∞–ї—Л –њ—А–Є —Б—З–Є—В—Л–≤–∞–љ–Є–Є –Є–љ—Д–Њ—А–Љ–∞—Ж–Є–Є (–њ—А–Є–ї–Њ–ґ–µ–љ–Є–µ 3 –±). –°–Є–≥–љ–∞–ї W/R=1 –Љ–Њ–ґ–µ—В –±—Л—В—М –њ–Њ–і–∞–љ –Є–Љ–њ—Г–ї—М—Б–Њ–Љ –Є–ї–Є —Г—А–Њ–≤–љ–µ–Љ. –Т—А–µ–Љ—П –њ–Њ—П–≤–ї–µ–љ–Є—П –≤—Л—Е–Њ–і–љ–Њ–≥–Њ —Б–Є–≥–љ–∞–ї–∞ –Љ–Њ–ґ–љ–Њ –Њ—В—Б—З–Є—В—Л–≤–∞—В—М –Њ—В –Љ–Њ–Љ–µ–љ—В–∞ –њ–Њ—Б—В—Г–њ–ї–µ–љ–Є—П —Б–Є–≥–љ–∞–ї–Њ–≤ –∞–і—А–µ—Б–∞ t–≤–∞ –ї–Є–±–Њ —Б–Є–≥–љ–∞–ї–Њ–≤ —Г–њ—А–∞–≤–ї–µ–љ–Є—П, –≤—А–µ–Љ—П –≤—Л–±–Њ—А–Ї–Є —Б–Є–≥–љ–∞–ї–∞ RAS t –Т RAS , –≤—А–µ–Љ—П –≤—Л–±–Њ—А–Ї–Є —Б–Є–≥–љ–∞–ї–∞ CAS t –Т CAS. –С–Њ–ї–µ–µ –Є–љ—Д–Њ—А–Љ–∞—В–Є–≤–љ—Л–Љ —П–≤–ї—П–µ—В—Б—П –њ–∞—А–∞–Љ–µ—В—А t –Т CAS , —В.–Ї. –Є–љ—Д–Њ—А–Љ–∞—Ж–Є—О –≤—Л–≤–Њ–і–Є—В –Є–Ј –Љ–Є–Ї—А–Њ—Б—Е–µ–Љ—Л —Б–Є–≥–љ–∞–ї CAS –њ—А–Є –љ–∞–ї–Є—З–Є–Є —Б–Є–≥–љ–∞–ї–∞ W/R=1.

–Ш–Ј –њ—А–Є–ї–Њ–ґ–µ–љ–Є—П 5 –± —Б–ї–µ–і—Г–µ—В: t –Т RAS=t –Т CAS+t –£–° RAS CAS.

–Ф–ї—П –Њ—Ж–µ–љ–Ї–Є –±—Л—Б—В—А–Њ–і–µ–є—Б—В–≤–Є—П –Љ–Є–Ї—А–Њ—Б—Е–µ–Љ—Л –њ–∞–Љ—П—В–Є –≤ —А–∞—Б—З–µ—В –њ—А–Є–љ–Є–Љ–∞—О—В –≤—А–µ–Љ—П —Ж–Є–Ї–ї–∞ –Ј–∞–њ–Є—Б–Є (—Б—З–Є—В—Л–≤–∞–љ–Є—П) t –¶ –Ч–Я, t –¶ –°–І. –Ф—А—Г–≥–Є–µ –≤—А–µ–Љ–µ–љ–љ—Л–µ –њ–∞—А–∞–Љ–µ—В—А—Л –љ–µ–Њ–±—Е–Њ–і–Є–Љ—Л –і–ї—П –Њ–±–µ—Б–њ–µ—З–µ–љ–Є—П –±–µ—Б—Б–±–Њ–є–љ–Њ–≥–Њ —Д—Г–љ–Ї—Ж–Є–Њ–љ–Є—А–Њ–≤–∞–љ–Є—П –Љ–Є–Ї—А–Њ—Б—Е–µ–Љ –≤ —Б–Њ—Б—В–∞–≤–µ —Н–ї. –∞–њ–њ–∞—А–∞—В—Г—А—Л.

–Ф–Є–љ–∞–Љ–Є—З–µ—Б–Ї–Є–µ –њ–∞—А–∞–Љ–µ—В—А—Л –Љ–Є–Ї—А–Њ—Б—Е–µ–Љ—Л –Ъ565–†–£3–У (–љ—Б)

|

t –¶ –Ч–Я (–°–І) |

370 |

t –£–° CAS RAS |

65 |

пБі CAS ** |

80 |

|

t –¶ –°–І-–Ь-–Ч–Я * |

420 |

t –£ –Р RAS |

25 |

пБі –Т CAS |

135 |

|

t –¶ –Ч–Я (–°–І) ** |

225 |

t –£–° CAS A |

10 |

T –†–Х–У , –Љ—Б |

2 |

|

пБі RAS |

200 |

t –£ –Р CAS |

55 |

||

|

пБі RAS |

120 |

пБі WR |

55 |

||

|

пБі CAS |

135 |

t –£ DI CAS |

55 |

*–Т—А–µ–Љ—П —Ж–Є–Ї–ї–∞ –≤ —А–µ–ґ–Є–Љ–µ (—Б—З–Є—В—Л–≤–∞–љ–Є–µ-–Љ–Њ–і–Є—Д–Є–Ї–∞—Ж–Є—П-–Ј–∞–њ–Є—Б—М) ** –Т —Б—В—А–∞–љ–Є—З–љ–Њ–Љ —А–µ–ґ–Є–Љ–µ

–Ф–ї—П –Њ–±–µ—Б–њ–µ—З–µ–љ–Є—П –љ–∞–і–µ–ґ–љ–Њ–≥–Њ —Б–Њ—Е—А–∞–љ–µ–љ–Є—П –Ј–∞–њ–Є—Б–∞–љ–љ–Њ–є –≤ –љ–∞–Ї–Њ–њ–Є—В–µ–ї–µ –Є–љ—Д–Њ—А–Љ–∞—Ж–Є–Є —А–µ–∞–ї–Є–Ј—Г—О—В —А–µ–ґ–Є–Љ –њ—А–Є–љ—Г–і–Є—В–µ–ї—М–љ–Њ–є —А–µ–≥–µ–љ–µ—А–∞—Ж–Є–Є. –†–µ–≥–µ–љ–µ—А–∞—Ж–Є—П –Є–љ—Д–Њ—А–Љ–∞—Ж–Є–Є –≤ –Ї–∞–ґ–і–Њ–Љ –≠–Я –і–Њ–ї–ґ–љ–∞ –Њ—Б—Г—Й–µ—Б—В–≤–ї—П—В—М—Б—П –љ–µ —А–µ–ґ–µ —З–µ–Љ —З–µ—А–µ–Ј 2 –Љ—Б.

–Т—А–µ–Љ—П, –≤ —В–µ—З–µ–љ–Є–Є –Ї–Њ—В–Њ—А–Њ–≥–Њ –љ–µ–Њ–±—Е–Њ–і–Є–Љ–Њ –Њ–±—А–∞—В–Є—В—М—Б—П –Ї —Б—В—А–Њ–Ї–µ –і–ї—П —А–µ–≥–µ–љ–µ—А–∞—Ж–Є–Є, –Њ–њ—А–µ–і–µ–ї—П–µ—В –њ–∞—А–∞–Љ–µ—В—А вАЬ–Я–µ—А–Є–Њ–і —А–µ–≥–µ–љ–µ—А–∞—Ж–Є–ЄвАЭ –Ґ—А–µ–≥.

–Я–Њ—Б–Ї–Њ–ї—М–Ї—Г –Њ–±—А–∞—Й–µ–љ–Є–µ –Ї —А–∞–Ј–љ—Л–Љ —Б—В—А–Њ–Ї–∞–Љ –њ—А–Њ–Є—Б—Е–Њ–і–Є—В —Б —А–∞–Ј–ї–Є—З–љ—Л–Љ–Є –њ–Њ –і–ї–Є—В–µ–ї—М–љ–Њ—Б—В–Є –Є–љ—В–µ—А–≤–∞–ї–∞–Љ–Є –≤—А–µ–Љ–µ–љ–Є, —А–∞—Б—З–Є—В—Л–≤–∞—В—М —В–Њ–ї—М–Ї–Њ –љ–∞ –∞–≤—В–Њ–Љ–∞—В–Є—З–µ—Б–Ї—Г—О —А–µ–≥–µ–љ–µ—А–∞—Ж–Є—О –љ–µ–ї—М–Ј—П.

–¶–Є–Ї–ї —А–µ–≥–µ–љ–µ—А–∞—Ж–Є–Є —Б–Њ—Б—В–Њ–Є—В –Є–Ј m –Њ–±—А–∞—Й–µ–љ–Є–є –Ї –Љ–∞—В—А–Є—Ж–µ, –≥–і–µ m-—З–Є—Б–ї–Њ —Б—В—А–Њ–Ї, –њ—Г—В–µ–Љ –њ–µ—А–µ–±–Њ—А–∞ –∞–і—А–µ—Б–Њ–≤ —Б—В—А–Њ–Ї —Б –њ–Њ–Љ–Њ—Й—М—О –≤–љ–µ—И–љ–µ–≥–Њ —Б—З–µ—В—З–Є–Ї–∞ —Ж–Є–Ї–ї–Њ–≤ –Њ–±—А–∞—Й–µ–љ–Є–є. –Ю–±—А–∞—Й–µ–љ–Є–µ –Ї –Љ–∞—В—А–Є—Ж–µ –і–ї—П —А–µ–≥–µ–љ–µ—А–∞—Ж–Є–Є –Љ–Њ–ґ–µ—В –±—Л—В—М –Њ—А–≥–∞–љ–Є–Ј–Њ–≤–∞–љ–Њ –њ–Њ –ї—О–±–Њ–Љ—Г –Є–Ј —А–µ–ґ–Є–Љ–Њ–≤: –Ј–∞–њ–Є—Б–Є, —Б—З–Є—В—Л–≤–∞–љ–Є—П, —Б—З–Є—В—Л–≤–∞–љ–Є—П-–Љ–Њ–і–Є—Д–Є–Ї–∞—Ж–Є–Є-–Ј–∞–њ–Є—Б–Є, –∞ —В–∞–Ї–ґ–µ –њ–Њ —Б–њ–µ—Ж–Є–∞–ї—М–љ–Њ–Љ—Г —А–µ–ґ–Є–Љ—Г —А–µ–≥–µ–љ–µ—А–∞—Ж–Є–Є- —Б–Є–≥–љ–∞–ї–Њ–Љ RAS.

–†–µ–ґ–Є–Љ —А–∞–±–Њ—В—Л вАЬ–°—З–Є—В—Л–≤–∞–љ–Є–µ-–Љ–Њ–і–Є—Д–Є–Ї–∞—Ж–Є—П-–Ј–∞–њ–Є—Б—МвАЭ –Ј–∞–Ї–ї—О—З–∞–µ—В—Б—П –≤ —Б—З–Є—В—Л–≤–∞–љ–Є–Є –Є–љ—Д–Њ—А–Љ–∞—Ж–Є–Є —Б –њ–Њ—Б–ї–µ–і—Г—О—Й–µ–є –Ј–∞–њ–Є—Б—М—О –≤ –Њ–і–Є–љ –Є —В–Њ—В –ґ–µ –≠–Я. –Т–Њ –≤—А–µ–Љ–µ–љ–љ—Л—Е –і–Є–∞–≥—А–∞–Љ–Љ–∞—Е —Б–Є–≥–љ–∞–ї–Њ–≤ –і–ї—П —Н—В–Њ–≥–Њ —А–µ–ґ–Є–Љ–∞ —Б–Њ–≤–Љ–µ—Й–µ–љ—Л –і–Є–∞–≥—А–∞–Љ–Љ—Л –і–ї—П —Б—З–Є—В—Л–≤–∞–љ–Є—П (–њ—А–Є–ї–Њ–ґ–µ–љ–Є–µ 3 –±) –Є –Ј–∞–њ–Є—Б–Є (–њ—А–Є–ї–Њ–ґ–µ–љ–Є–µ 3 –∞) –Є–љ—Д–Њ—А–Љ–∞—Ж–Є–Є: –њ—А–Є –љ–µ–Є–Ј–Љ–µ–љ–µ–љ–љ—Л—Е —Б–Є–≥–љ–∞–ї–∞—Е RAS –Є CAS —А–µ–ґ–Є–Љ —Б—З–Є—В—Л–≤–∞–љ–Є—П —Б–Љ–µ–љ—П–µ—В —А–µ–ґ–Є–Љ –Ј–∞–њ–Є—Б–Є –і–∞–љ–љ—Л—Е –њ–Њ —В–Њ–Љ—Г –ґ–µ –∞–і—А–µ—Б—Г. –Ь–Њ–і–Є—Д–Є–Ї–∞—Ж–Є—П —А–µ–ґ–Є–Љ–∞ –Ј–∞–Ї–ї—О—З–∞–µ—В—Б—П –≤ —Б–Љ–µ–љ–µ —Б–Є–≥–љ–∞–ї–∞ —Б—З–Є—В—Л–≤–∞–љ–Є—П –љ–∞ —Б–Є–≥–љ–∞–ї –Ј–∞–њ–Є—Б–Є –Є –≤ –њ–Њ–і–≤–µ–і–µ–љ–Є–Є –Ї–Њ –≤—Е–Њ–і—Г DI –Ј–∞–њ–Є—Б—Л–≤–∞–µ–Љ–Њ–є –Є–љ—Д–Њ—А–Љ–∞—Ж–Є–Є. –Т—А–µ–Љ—П —Ж–Є–Ї–ї–∞ –≤ —Н—В–Њ–Љ —А–µ–ґ–Є–Љ–µ –Њ–±—А–∞—Й–µ–љ–Є—П –±–Њ–ї—М—И–µ —З–µ–Љ –≤ –і—А—Г–≥–Є—Е.

–Я—А–Є –Њ—А–≥–∞–љ–Є–Ј–∞—Ж–Є–Є –њ—А–Є–љ—Г–і–Є—В–µ–ї—М–љ–Њ–є —А–µ–≥–µ–љ–µ—А–∞—Ж–Є–Є —П–≤–ї—П–µ—В—Б—П —А–µ–ґ–Є–Љ —А–µ–≥–µ–љ–µ—А–∞—Ж–Є–Є —Б–Є–≥–љ–∞–ї–Њ–Љ RAS (–њ—А–Є–ї–Њ–ґ–µ–љ–Є–µ 3 –≤), –њ—А–Є –Ї–Њ—В–Њ—А–Њ–Љ –Њ—Б—Г—Й–µ—Б—В–≤–ї—П—О—В –њ–µ—А–µ–±–Њ—А –∞–і—А–µ—Б–Њ–≤ –≤ —Б–Њ–њ—А–Њ–≤–Њ–ґ–і–µ–љ–Є–Є —Б—В—А–Њ–±–Є—А—Г—О—Й–µ–≥–Њ —Б–Є–≥–љ–∞–ї–∞ RAS –њ—А–Є CAS=1.

–Т —А–∞—Б—З–µ—В –≤—А–µ–Љ–µ–љ–Є —А–µ–≥–µ–љ–µ—А–∞—Ж–Є–Є —Б–ї–µ–і—Г–µ—В –њ—А–Є–љ–Є–Љ–∞—В—М –≤—А–µ–Љ—П —Ж–Є–Ї–ї–∞ –њ—А–Є –≤—Л–±—А–∞–љ–љ–Њ–Љ —А–µ–ґ–Є–Љ–µ —А–µ–≥–µ–љ–µ—А–∞—Ж–Є–Є, —Г–Љ–љ–Њ–ґ–Є–≤ –µ–≥–Њ –љ–∞ —З–Є—Б–ї–Њ —Б—В—А–Њ–Ї. –Э–∞ —А–µ–≥–µ–љ–µ—А–∞—Ж–Є—О –Є–љ—Д–Њ—А–Љ–∞—Ж–Є–Є –≤ –≠–Я –Њ–і–љ–Њ–є —Б—В—А–Њ–Ї–Є —Г –Љ–Є–Ї—А–Њ—Б—Е–µ–Љ—Л –Ъ565–†–£3–У –≤ —А–µ–ґ–Є–Љ–µ вАЬ–°—З–Є—В—Л–≤–∞–љ–Є–µ-–Љ–Њ–і–Є—Д–Є–Ї–∞—Ж–Є—П-–Ј–∞–њ–Є—Б—МвАЭ –љ–µ–Њ–±—Е–Њ–і–Є–Љ–Њ 420 –љ—Б, —В–Њ–≥–і–∞ –і–ї—П —А–µ–≥–µ–љ–µ—А–∞—Ж–Є–Є –≠–Я –≤—Б–µ—Е 128 —Б—В—А–Њ–Ї –њ–Њ—В—А–µ–±—Г–µ—В—Б—П 54 –Љ–Ї—Б, —З—В–Њ —Б–Њ—Б—В–∞–≤–Є—В 2.7% —А–∞–±–Њ—З–µ–≥–Њ –≤—А–µ–Љ–µ–љ–Є –Љ–Є–Ї—А–Њ—Б—Е–µ–Љ—Л. –Т —А–µ–ґ–Є–Љ–µ —А–µ–≥–µ–љ–µ—А–∞—Ж–Є–Є —В–Њ–ї—М–Ї–Њ —Б–Є–≥–љ–∞–ї–Њ–Љ RAS –Њ–±—Й–µ–µ

–≤—А–µ–Љ—П —А–µ–≥–µ–љ–µ—А–∞—Ж–Є–Є —Г–Љ–µ–љ—М—И–∞–µ—В—Б—П –і–Њ 47.4 –Љ–Ї—Б —З—В–Њ —Б–Њ—Б—В–∞–≤–Є 2.3% –≤—А–µ–Љ–µ–љ–Є —Д—Г–љ–Ї—Ж–Є–Њ–љ–Є—А–Њ–≤–∞–љ–Є—П –Љ–Є–Ї—А–Њ—Б—Е–µ–Љ—Л.

m-—З–Є—Б–ї–Њ

—Б—В—А–Њ–Ї

m-—З–Є—Б–ї–Њ

—Б—В—А–Њ–Ї

t–Ч–Р–Э-–≤—А–µ–Љ—П –Ј–∞–љ—П—В–Њ—Б—В–Є

–°—В—А–∞–љ–Є—З–љ—Л–µ —А–µ–ґ–Є–Љ—Л –Ј–∞–њ–Є—Б–Є –Є —Б—З–Є—В—Л–≤–∞–љ–Є—П —А–µ–∞–ї–Є–Ј—Г—О—В –Њ–±—А–∞—Й–µ–љ–Є–µ–Љ –Ї –Љ–Є–Ї—А–Њ—Б—Е–µ–Љ–µ –њ–Њ –∞–і—А–µ—Б—Г —Б—В—А–Њ–Ї–Є —Б –≤—Л–±–Њ—А–Ї–Њ–є –≠–Я —Н—В–Њ–є —Б—В—А–Њ–Ї–Є –Є–Ј–Љ–µ–љ–µ–љ–Є–µ –∞–і—А–µ—Б–∞ —Б—В–ї–±—Ж–Њ–≤. –Т —Н—В–Є—Е —А–µ–ґ–Є–Љ–∞—Е –Ј–љ–∞—З–Є—В–µ–ї—М–љ–Њ —Г–Љ–µ–љ—М—И–∞–µ—В—Б—П –≤—А–µ–Љ—П —Ж–Є–Ї–ї–∞ –Ј–∞–њ–Є—Б–Є (—Б—З–Є—В—Л–≤–∞–љ–Є—П) –њ–Њ—Б–Ї–Њ–ї—М–Ї—Г –њ—А–Є –љ–µ–Є–Ј–Љ–µ–љ–љ—Л—Е —Б–Є–≥–љ–∞–ї–∞—Е RAS=0 –Є –Ї–Њ–і–∞ –∞–і—А–µ—Б–∞ —Б—В—А–Њ–Ї–Є –Є—Б–њ–Њ–ї—М–Ј–Њ–≤–∞–љ–∞ —З–∞—Б—В—М –њ–Њ–ї–љ–Њ–≥–Њ —Ж–Є–Ї–ї–∞ –Ј–∞–њ–Є—Б–Є (—Б—З–Є—В—Л–≤–∞–љ–Є—П), –Њ—В–љ–Њ—Б—П—Й–∞—П—Б—П –Ї –∞–і—А–µ—Б–∞—Ж–Є–Є —Б—В–Њ–ї–±—Ж–Њ–≤.

–Ь–Є–Ї—А–Њ—Б—Е–µ–Љ–∞ –Ъ565–†–£3–У –љ—Г–ґ–і–∞–µ—В—Б—П –≤ —В—А–µ—Е –Є—Б—В–Њ—З–љ–Є–Ї–∞—Е –њ–Є—В–∞–љ–Є—П –Є —Б–ї–µ–і—Г–µ—В —Г—З–Є—В—Л–≤–∞—В—М —В—А–µ–±–Њ–≤–∞–љ–Є—П –њ–Њ –њ–Њ—А—П–і–Ї—Г –≤–Ї–ї—О—З–µ–љ–Є—П –Є –≤—Л–Ї–ї—О—З–µ–љ–Є—П –Є—Б—В–Њ—З–љ–Є–Ї–Њ–≤ –њ–Є—В–∞–љ–Є—П: –њ–µ—А–≤—Л–Љ –≤–Ї–ї—О—З–∞—О—В –Є—Б—В–Њ—З–љ–Є–Ї вАУ5–Т, –∞ –Њ—В–Ї–ї—О—З–∞—О—В –њ–Њ—Б–ї–µ–і–љ–Є–Љ. –≠—В–Њ —В—А–µ–±–Њ–≤–∞–љ–Є–µ –Њ–±—Г—Б–ї–Њ–≤–ї–µ–љ–Њ —В–µ–Љ, —З—В–Њ –љ–∞–њ—А—П–ґ–µ–љ–Є–µ вАУ5–Т –њ–Њ–і–∞–µ—В—Б—П –љ–∞ –њ–Њ–і–ї–Њ–ґ–Ї—Г (–Ї—А–Є—Б—В–∞–ї–ї) –Є –µ—Б–ї–Є –µ–≥–Њ –љ–µ –њ–Њ–і–Ї–ї—О—З–Є—В—М –њ–µ—А–≤—Л–Љ, —В–Њ –≤–Њ–Ј–і–µ–є—Б—В–≤–Є–µ–Љ, –і–∞–ґ–µ –Ї—А–∞—В–Ї–Њ–≤—А–µ–Љ–µ–љ–љ—Л–Љ, –љ–∞–њ—А—П–ґ–µ–љ–Є–є –і–≤—Г—Е –і—А—Г–≥–Є—Е –Є—Б—В–Њ—З–љ–Є–Ї–Њ–≤ —Б –љ–∞–њ—А—П–ґ–µ–љ–Є–µ–Љ 5 –Є 12–Т –Љ–Њ–ґ–µ—В –њ—А–Њ–Є–Ј–Њ–є—В–Є –≤ –Ї—А–Є—Б—В–∞–ї–ї–µ —В–µ–њ–ї–Њ–≤–Њ–є –њ—А–Њ–±–Њ–є. –Я–Њ—А—П–і–Њ–Ї –≤–Ї–ї—О—З–µ–љ–Є—П –і–≤—Г—Е –і—А—Г–≥–Є—Е –љ–∞–њ—А—П–ґ–µ–љ–Є–є –њ–Є—В–∞–љ–Є—П –Љ–Њ–ґ–µ—В –±—Л—В—М –ї—О–±—Л–Љ.

–Я–Њ—Б–ї–µ –њ–Њ–і–∞—З–Є –љ–∞–њ—А—П–ґ–µ–љ–Є—П –њ–Є—В–∞–љ–Є—П –Љ–Є–Ї—А–Њ—Б—Е–µ–Љ–∞ –Ъ565–†–£3–У –њ–µ—А–µ—Е–Њ–і–Є—В –≤ –љ–Њ—А–Љ–∞–ї—М–љ—Л–є —А–µ–ґ–Є–Љ —Д—Г–љ–Ї—Ж–Є–Њ–љ–Є—А–Њ–≤–∞–љ–Є—П —З–µ—А–µ–Ј –≤–Њ—Б–µ–Љ—М —А–∞–±–Њ—З–Є—Е —Ж–Є–Ї–ї–Њ–≤.

2.2.–Я–∞—А–∞–Љ–µ—В—А—Л –Љ–Є–Ї—А–Њ—Б—Е–µ–Љ—Л –Ъ565–†–£3–У

–•–∞—А–∞–Ї—В–µ—А–Є—Б—В–Є–Ї–∞ –Љ–Є–Ї—А–Њ—Б—Е–µ–Љ—Л –Ъ565–†–£3–У

–Х–Љ–Ї–Њ—Б—В—М,–±–Є—В -16–Ъ x 1

–Т—А–µ–Љ—П —Ж–Є–Ї–ї–∞ –Ј–∞–њ–Є—Б–Є —Б—З–Є—В—Л–≤–∞–љ–Є—П- 370–љ—Б

–Э–∞–њ—А—П–ґ–µ–љ–Є–µ –њ–Є—В–∞–љ–Є—П- 5–Т,12–Т,-12–Т

–Я–Њ—В—А–µ–±–ї—П–µ–Љ–∞—П –Љ–Њ—Й–љ–Њ—Б—В—М: –≤ —А–µ–ґ–Є–Љ–µ —Е—А–∞–љ–µ–љ–Є—П- 40 –Љ–Т—В

–≤ —А–µ–ґ–Є–Љ–µ –Њ–±—А–∞—Й–µ–љ–Є—П- 460–Љ–Т—В

–Ґ–Є–њ –Ї–Њ—А–њ—Г—Б–∞- –Ф–Ш–Я;16;7.5

–°—В–∞—В–Є—З–µ—Б–Ї–Є–µ –њ–∞—А–∞–Љ–µ—В—А—Л –Љ–Є–Ї—А–Њ—Б—Е–µ–Љ—Л –Ъ565–†–£3–У

I –њ–Њ—В—А–µ–±–ї–µ–љ–Є—П –і–Є–љ–∞–Љ–Є—З–µ—Б–Ї–Є–є- 45–Љ–Р I –њ–Њ—В—А–µ–±–ї–µ–љ–Є—П —Б—В–∞—В–Є—З–µ—Б–Ї–Є–є- 4–Ь–∞

U –≤—Е –љ–Є–Ј–Ї–Њ–≥–Њ —Г—А–Њ–≤–љ—П –Љ–∞—Е 0.8B min вАУ1B U –≤—Е –≤—Л—Б–Њ–Ї–Њ–≥–Њ —Г—А–Њ–≤–љ—П –≤–∞—Е 6–Т min 2.4B

U –≤—Л—Е –љ–Є–Ј–Ї–Њ–≥–Њ —Г—А–Њ–≤–љ—П –Љ–∞—Е 0.4B

U –≤—Л—Е –≤—Л—Б–Њ–Ї–Њ–≥–Њ —Г—А–Њ–≤–љ—П min 2.4B

I –≤—Л—Е –љ–Є–Ј–Ї–Њ–≥–Њ —Г—А–Њ–≤–љ—П –Љ–∞—Е 4–Љ–Р

I –≤—Л—Е –≤—Л—Б–Њ–Ї–Њ–≥–Њ —Г—А–Њ–≤–љ—П –Љ–∞—Е 2–Љ–Р

–Т—Л—Е–Њ–і–љ–Њ–є —В–Њ–Ї —Г—В–µ—З–Ї–Є –Љ–∞—Е 10–Љ–Ї–Р

–Т—Е–Њ–і–љ–Њ–є —В–Њ–Ї —Г—В–µ—З–Ї–Є –Љ–∞—Е 10–Љ–Ї–Р

–Т—Е–Њ–і–љ–∞—П –µ–Љ–Ї–Њ—Б—В—М –њ–Њ –≤—Е–Њ–і–∞–Љ WR/RD, RAS, CAS –Љ–∞—Е 10–њ–§

–њ–Њ –≤—Е–Њ–і–∞–Љ A, DI –Љ–∞—Е 6 –њ–§

–Т—Л—Е–Њ–і–љ–∞—П –µ–Љ–Ї–Њ—Б—В—М –Љ–∞—Е 10 –њ–§

–Ь–∞–Ї—Б–Є–Љ–∞–ї—М–љ–∞—П –µ–Љ–Ї–Њ—Б—В—М –љ–∞–≥—А—Г–Ј–Ї–Є 100 –њ–§

2.3.–†–∞—Б—З–µ—В –љ–∞–≥—А—Г–Ј–Њ—З–љ–Њ–є —Б–њ–Њ—Б–Њ–±–љ–Њ—Б—В–Є –Љ–Є–Ї—А–Њ—Б—Е–µ–Љ—Л –Ъ565–†–£3–У

–•–∞—А–∞–Ї—В–µ—А–љ—Л–Љ –і–ї—П –Ф–С–Ш–° –Ч–£, –Є–Ј–≥–Њ—В–Њ–≤–ї—П–µ–Љ—Л—Е –њ–Њ –Ь–Ф–Я-—В–µ—Е–љ–Њ–ї–Њ–≥–Є–Є, —П–≤–ї—П–µ—В—Б—П –≤—Л—Б–Њ–Ї–Њ–µ –≤—Е–Њ–і–љ–Њ–µ –Њ–Љ–Є—З–µ—Б–Ї–Њ–µ —Б–Њ–њ—А–Њ—В–Є–≤–ї–µ–љ–Є–µ. –Я—А–Є –Њ–њ—А–µ–і–µ–ї–µ–љ–Є–Є —З–Є—Б–ї–∞ Q –Ф–С–Ш–° –Ч–£, –љ–∞–≥—А—Г–ґ–∞–µ–Љ—Л—Е –љ–∞ –Ґ–Ґ–Ы-—Б—Е–µ–Љ—Г, —Г—З–Є—В—Л–≤–∞–µ—В—Б—П –≤ –Њ—Б–љ–Њ–≤–љ–Њ–Љ –µ–Љ–Ї–Њ—Б—В—М –≤—Е–Њ–і–Њ–≤ –Љ–Є–Ї—А–Њ—Б—Е–µ–Љ—Л –њ–∞–Љ—П—В–Є.

–°–Ь–Р–•- –Љ–∞–Ї—Б–Є–Љ–∞–ї—М–љ–∞—П –µ–Љ–Ї–Њ—Б—В—М –љ–∞–≥—А—Г–Ј–Ї–Є –Ґ–Ґ–Ы-—Б—Е–µ–Љ—Л

–°I- –µ–Љ–Ї–Њ—Б—В—М –≤—Е–Њ–і–∞ –Ф–С–Ш–° –Ч–£

–Ґ.–Ї. –і–ї—П –Ъ555–Ъ–Я2 –µ–Љ–Ї–Њ—Б—В—М –°MAXвЙ§150–Я—Д, –∞ –і–ї—П –Ъ565–†–£3–У –µ–Љ–Ї–Њ—Б—В—М –°IвЙИ 6-10–Я—Д, —В–Њ QвЙ§15-25.

–Т—Л—Е–Њ–і –Ъ565–†–£3–У –Є–Љ–µ–µ—В —Б–Њ–±—Б—В–≤–µ–љ–љ—Г—О –µ–Љ–Ї–Њ—Б—В—М –°–Т–Ђ–•=10–њ–§ –Є —А–∞–±–Њ—В–∞–µ—В –љ–∞ –µ–Љ–Ї–Њ—Б—В–љ—Г—О –љ–∞–≥—А—Г–Ј–Ї—Г –і–Њ 100–њ–§. –Я–Њ—Н—В–Њ–Љ—Г –њ–Њ –≤—Е–Њ–і—Г –Љ–Њ–ґ–љ–Њ –Њ–±—К–µ–і–Є–љ–Є—В—М –і–Њ 10 –Љ–Є–Ї—А–Њ—Б—Е–µ–Љ –њ–∞–Љ—П—В–Є.

3.1.–Ь—Г–ї—М—В–Є–њ–ї–µ–Ї—Б–Њ—А—Л –±–ї–Њ–Ї–∞ –і–Є–љ–∞–Љ–Є—З–µ—Б–Ї–Њ–≥–Њ –Ю–Ч–£.

–Ь—Г–ї—М—В–Є–њ–ї–µ–Ї—Б–Њ—А—Л –≤—Л–њ–Њ–ї–љ–µ–љ—Л –љ–∞ —Б—Е–µ–Љ–∞—Е –Ъ555–Ъ–Я2.

–Ґ–∞–±–ї–Є—Ж–∞ –Є—Б—В–Є–љ–љ–Њ—Б—В–Є

|

–Т—Е–Њ–і—Л |

–Т—Л—Е–Њ–і |

||||||

|

E |

SED2 |

SED1 |

DO |

D1 |

D2 |

D3 |

D |

|

H |

X |

X |

X |

X |

X |

X |

L |

|

L |

L |

L |

L |

X |

X |

X |

L |

|

L |

L |

L |

H |

X |

X |

X |

H |

|

L |

L |

H |

X |

L |

X |

X |

L |

|

L |

L |

H |

X |

H |

X |

X |

H |

|

L |

H |

L |

X |

X |

L |

X |

L |

|

L |

H |

L |

X |

X |

H |

X |

H |

|

L |

L |

H |

X |

X |

X |

L |

L |

|

L |

L |

H |

X |

X |

X |

H |

H |

–Э–∞–Ј–љ–∞—З–µ–љ–Є–µ –≤—Л–≤–Њ–і–Њ–≤ –Ш–° –Ъ555–Ъ–Я2

-

1

–Т—Е–Њ–і –≤—Л–±–Њ—А–∞ S1

EO

2

–Т—Е–Њ–і –∞–і—А–µ—Б–∞ A1

SED2

3

–Т—Е–Њ–і X1.4

D3.0

4

–Т—Е–Њ–і X1.3

D2.0

5

–Т—Е–Њ–і X1.2

D1.0

6

–Т—Е–Њ–і X1.1

D0.0

7

–Т—Л—Е–Њ–і Y1

D.O

8

–Ю–±—Й–Є–є

GND

9

–Т—Л—Е–Њ–і Y2

D.1

10

–Т—Е–Њ–і X2.1

D0.1

11

–Т—Е–Њ–і X2.2

D1.1

12

–Т—Е–Њ–і X2.3

D2.1

13

–Т—Е–Њ–і X2.4

D3.1

14

–Т—Е–Њ–і –∞–і—А–µ—Б–∞ A0

SED1

15

–Т—Е–Њ–і –≤—Л–±–Њ—А–∞ S2

E.1

16

–Я–Є—В–∞–љ–Є–µ

UCC

–£—Б–ї–Њ–≤–љ–Њ–µ –≥—А–∞—Д–Є—З–µ—Б–Ї–Њ–µ –Њ–±–Њ–Ј–љ–∞—З–µ–љ–Є–µ –Ш–° –Ъ–Я555–Ъ–Я2 (—А–Є—Б –∞) –Є —Д—Г–љ–Ї—Ж–Є–Њ–љ–∞–ї—М–љ–∞—П —Б—Е–µ–Љ–∞ –Њ–і–љ–Њ–≥–Њ —Н–ї–µ–Љ–µ–љ—В–∞ (—А–Є—Б –±).

(–∞)

(–±)

3.2.–Ю—А–≥–∞–љ–Є–Ј–∞—Ж–Є—П —А–∞–±–Њ—В—Л –Љ–Є–Ї—А–Њ—Б—Е–µ–Љ—Л –Ъ555–Ъ–Я2.

–Ь—Г–ї—М—В–Є–њ–ї–µ–Ї—Б–Њ—А –Ъ555–Ъ–Я2- —Н—В–Њ –і–≤–∞ –Љ—Г–ї—М—В–Є–њ–ї–µ–Ї—Б–Њ—А–∞ 1пВЃ4 —Б –Њ–±—Й–Є–Љ –і–µ—И–µ—Д—А–∞—В–Њ—А–Њ–Љ –∞–і—А–µ—Б–∞ –Ї–∞–љ–∞–ї–∞ –Є –≤—Е–Њ–і–∞–Љ–Є –≤—Л–±–Њ—А–∞ (—Б—В—А–Њ–±–Є—А—Г—О—Й–Є–Љ–Є –≤—Е–Њ–і–∞–Љ–Є) –Њ–і–љ–Њ–≥–Њ –Є–Ј –Љ—Г–ї—М—В–Є–њ–ї–µ–Ї—Б–Њ—А–Њ–≤ –Х.0 –Є E.1.

–Ш–љ–≤–µ—А—В–Њ—А—Л –љ–∞ –≤—Е–Њ–і–∞—Е –Х.0 –Є –Х.1 –њ—А–µ–і–љ–∞–Ј–љ–∞—З–µ–љ—Л –і–ї—П —А–∞–Ј–≤—П–Ј–Ї–Є –≤–љ—Г—В—А–µ–љ–љ–Є—Е —Ж–µ–њ–µ–є –Њ—В –≤—Е–Њ–і–љ—Л—Е —И–Є–љ –Є –Њ–±–µ—Б–њ–µ—З–Є–≤–∞—О—В –њ–Њ–Љ–µ—Е–Њ—Г—Б—В–Њ–є—З–Є–≤–Њ—Б—В—М —Б—Е–µ–Љ—Л –њ–Њ –≤—Е–Њ–і—Г.

–Ч–∞–њ—А–µ—Й–µ–љ–∞ –њ–µ—А–µ–і–∞—З–∞ –Є–љ—Д–Њ—А–Љ–∞—Ж–Є–Є —З–µ—А–µ–Ј –Љ—Г–ї—М—В–Є–њ–ї–µ–Ї—Б–Њ—А, –Ї–Њ–≥–і–∞ –Њ–љ –љ–∞—Е–Њ–і–Є—В—Б—П –≤ –љ–µ–≤—Л–±—А–∞–љ–љ–Њ–Љ —Б–Њ—Б—В–Њ—П–љ–Є–Є (–њ—А–Є —Н—В–Њ–Љ –≤—Л—Е–Њ–і –љ–∞—Е–Њ–і–Є—В—Б—П –≤ —Б–Њ—Б—В–Њ—П–љ–Є–Є –љ–Є–Ј–Ї–Њ–≥–Њ —Г—А–Њ–≤–љ—П). –Ъ–∞–ґ–і—Л–є –Є–Ј –Љ—Г–ї—М—В–Є–њ–ї–µ–Ї—Б–Њ—А–Њ–≤ –Є–Љ–µ–µ—В –њ–Њ —З–µ—В—Л—А–µ –Є–љ—Д–Њ—А–Љ–∞—Ж–Є–Њ–љ–љ—Л—Е –≤—Е–Њ–і–∞ –Є —Б–≤–Њ–Є —Б—В—А–Њ–±–Є—А—Г—О—Й–Є–µ –≤—Е–Њ–і—Л –Х.0 –Є –Х1. –Ф–≤–∞ –∞—А–µ—Б–љ—Л—Е –≤—Е–Њ–і–∞ SED1 –Є SED2 —Г–њ—А–∞–≤–ї—П—О—В –Њ–і–љ–Њ–≤—А–µ–Љ–µ–љ–љ–Њ –і–≤—Г–Љ—П –Љ—Г–ї—М—В–Є–њ–ї–µ–Ї—Б–Њ—А–∞–Љ–Є.

–Ъ–Њ–і, –Ї–Њ—В–Њ—А—Л–є –љ–∞–±—А–∞–љ –љ–∞ –∞–і—А–µ—Б–љ—Л—Е –≤—Е–Њ–і–∞—Е SED1 –Є SED2, —А–∞–Ј—А–µ—И–∞–µ—В —А–∞–±–Њ—В—Г —В–Њ–ї—М–Ї–Њ –Њ–і–љ–Њ–≥–Њ –Є–Ј –Є–љ—Д–Њ—А–Љ–∞—Ж–Є–Њ–љ–љ—Л—Е –≤—Е–Њ–і–Њ–≤ –Ї–∞–ґ–і–Њ–≥–Њ –Љ—Г–ї—М—В–Є–њ–ї–µ–Ї—Б–Њ—А–∞. –°–Є–≥–љ–∞–ї —Б –≤—Л–±—А–∞–љ–љ–Њ–≥–Њ –Є–љ—Д–Њ—А–Љ–∞—Ж–Є–Њ–љ–љ–Њ–≥–Њ –≤—Е–Њ–і–∞ –њ–Њ—П–≤–ї—П–µ—В—Б—П –љ–∞ –≤—Л—Е–Њ–і–µ —В–Њ–ї—М–Ї–Њ –њ—А–Є –љ–∞–ї–Є—З–Є–Є –љ–∞ —Б—В—А–Њ–±–Є—А—Г—О—Й–µ–Љ –≤—Е–Њ–і–µ –Х –љ–Є–Ј–Ї–Њ–≥–Њ —Г—А–Њ–≤–љ—П.

–Я–µ—А–≤–∞—П —Б—В—Г–њ–µ–љ—М –Љ—Г–ї—М—В–Є–њ–ї–µ–Ї—Б–Њ—А–∞ –≤—Л–њ–Њ–ї–љ–µ–љ–∞ –љ–∞ –Є–љ–≤–µ—А—В–Њ—А–∞—Е, –≤—В–Њ—А–∞—П –љ–∞ –ї–Њ–≥–Є—З–µ—Б–Ї–Є—Е —Н–ї–µ–Љ–µ–љ—В–∞—Е –Ш-–Ш–Ы–Ш (–±–µ–Ј –Є–љ–≤–µ—А—Б–Є–Є), –Є—Б–њ–Њ–ї—М–Ј—Г–µ—В —Б—В—А–Њ–±–Є—А—Г—О—Й–Є–µ —Б–≤–Њ–є—Б—В–≤–∞ —Д—Г–љ–Ї—Ж–Є–Є –Ш –∞—А–≥—Г–Љ–µ–љ—В–Њ–≤ –Ї–∞–љ–∞–ї–∞ –Є–љ—Д–Њ—А–Љ–∞—Ж–Є–Є –Є –∞–і—А–µ—Б–∞.

–Ш–° –Ъ555–Ъ–Я2 –≤–Ї–ї—О—З–∞–µ—В –≤—Е–Њ–і—Л —Г–њ—А–∞–≤–ї–µ–љ–Є—П —Б –њ–µ—А–µ–і–∞—З–Є –њ—А–Є –љ–Є–Ј–Ї–Њ–Љ —Г—А–Њ–≤–љ–µ –љ–∞–њ—А—П–ґ–µ–љ–Є—П –љ–∞ –≤—Е–Њ–і–µ –Є —Б –Ј–∞–њ—А–µ—В–Њ–Љ –њ–µ—А–µ–і–∞—З–Є –њ—А–Є –≤—Л—Б–Њ–Ї–Њ–Љ —Г—А–Њ–≤–љ–µ –љ–∞–њ—А—П–ґ–µ–љ–Є—П –љ–∞ –≤—Е–Њ–і–µ.

3.3.–•–∞—А–∞–Ї—В–µ—А–Є—Б—В–Є–Ї–Є –Љ–Є–Ї—А–Њ—Б—Е–µ–Љ—Л –Ъ555–Ъ–Я2

I–Т–• –љ–Є–Ј–Ї–Њ–≥–Њ —Г—А–Њ–≤–љ—П -0.4–Љ–Р

I–Т–• –≤—Л—Б–Њ–Ї–Њ–≥–Њ —Г—А–Њ–≤–љ—П 0.04–Љ–Р

I–Т–Ђ–• –љ–Є–Ј–Ї–Њ–≥–Њ —Г—А–Њ–≤–љ—П 4–Љ–Р

I–Т–Ђ–• –≤—Л—Б–Њ–Ї–Њ–≥–Њ —Г—А–Њ–≤–љ—П -0.4 –Љ–Р

U–Т–• –Ь–Р–• 5.5–Т

U–Т–• MIN вАУ0.4B

U–Т–• –љ–Є–Ј–Ї–Њ–≥–Њ —Г—А–Њ–≤–љ—П 0.4–Т

U–Т–• –≤—Л—Б–Њ–Ї–Њ–≥–Њ —Г—А–Њ–≤–љ—П 2.5–Т

–Э–∞–≥—А—Г–Ј–Њ—З–љ–∞—П —Б–њ–Њ—Б–Њ–±–љ–Њ—Б—В—М 10

–Т—А–µ–Љ—П –Ј–∞–і–µ—А–ґ–Ї–Є —А–∞—Б–њ—А–Њ—Б—В—А–∞–љ–µ–љ–Є—П —Б–Є–≥–љ–∞–ї–∞:

–њ—А–Є –≤–Ї–ї—О—З–µ–љ–Є–Є 20–љ—Б (–°–Э=15–њ–§)

–њ—А–Є –≤—Л–Ї–ї—О—З–µ–љ–Є–Є 20–љ—Б (–°–Э=15–Я—Д)

–°—А–µ–і–љ–Є–є —В–Њ–Ї –њ–Њ—В—А–µ–±–ї–µ–љ–Є—П –љ–µ –±–Њ–ї–µ–µ 3–Љ–Р

–Я–Њ–Љ–µ—Е–Њ—Г—Б—В–Њ–є—З–Є–≤–Њ—Б—В—М 0.3B

–І–∞—Б—В–Њ—В–∞ –њ–µ—А–µ–Ї–ї—О—З–µ–љ–Є—П –љ–µ –±–Њ–ї–µ–µ 25–Ь–У—Ж

U–Ь–Р–• –њ–Є—В–∞–љ–Є—П 5.5B

–°–Э –Ь–Р–•=150–њ–§

–Ф–Є–∞–њ–∞–Ј–Њ–љ —А–∞–±–Њ—З–Є—Е —В–µ–Љ–њ–µ—А–∞—В—Г—А -10 +70¬∞–°

4.1.–Я—А–Є–љ—Ж–Є–њ —А–∞–±–Њ—В—Л –Љ–Є–Ї—А–Њ—Б—Е–µ–Љ—Л –Ъ–†580–Ш–†82.

–Ъ–†580–Ш–†82 –њ—А–µ–і—Б—В–∞–≤–ї—П–µ—В —Б–Њ–±–Њ–є 8-—А–∞–Ј—А—П–і–љ—Л–є –±—Г—Д–µ—А–љ—Л–є —А–µ–≥–Є—Б—В—А, –њ—А–µ–і–љ–∞–Ј–љ–∞—З–µ–љ–љ—Л–є –і–ї—П –≤–≤–Њ–і–∞ –Є –≤—Л–≤–Њ–і–∞ –Є–љ—Д–Њ—А–Љ–∞—Ж–Є–Є —Б–Њ —Б—В—А–Њ–±–Є—А–Њ–≤–∞–љ–Є–µ–Љ.

–Ь–Є–Ї—А–Њ—Б—Е–µ–Љ–∞ –Є–Љ–µ–µ—В –≤–Њ—Б–µ–Љ—М —В—А–Є–≥–≥–µ—А–Њ–≤ D-—В–Є–њ–∞ –Є –≤–Њ—Б–µ–Љ—М –≤—Л—Е–Њ–і–љ—Л—Е –±—Г—Д–µ—А–Њ–≤, –Є–Љ–µ—О—Й–Є—Е –љ–∞ –≤—Л—Е–Њ–і–µ —Б–Њ—Б—В–Њ—П–љ–Є–µ вАЬ–≤—Л–Ї–ї—О—З–µ–љ–ЊвАЭ. –£–њ—А–∞–≤–ї–µ–љ–Є–µ –њ–µ—А–µ–і–∞—З–µ–є –Є–љ—Д–Њ—А–Љ–∞—Ж–Є–Є –Њ—Б—Г—Й–µ—Б—В–≤–ї—П–µ—В—Б—П —Б –њ–Њ–Љ–Њ—Й—М—О —Б–Є–≥–љ–∞–ї–∞ STB вАЬ—Б—В—А–Њ–±вАЭ.

–Я—А–Є –њ–Њ—Б—В—Г–њ–ї–µ–љ–Є–Є –љ–∞ –≤—Е–Њ–і STB —Б–Є–≥–љ–∞–ї–∞ –≤—Л—Б–Њ–Ї–Њ–≥–Њ —Г—А–Њ–≤–љ—П –Њ—Б—Г—Й–µ—Б—В–≤–ї—П–µ—В—Б—П –љ–µ—В–∞–Ї—В–Є—А—Г–µ–Љ–∞—П –њ–µ—А–µ–і–∞—З–∞ –Є–љ—Д–Њ—А–Љ–∞—Ж–Є–Є –Њ—В –≤—Е–Њ–і–∞ DI –і–Њ –≤—Л—Е–Њ–і–∞ DO. –Я—А–Є –њ–Њ–і–∞—З–µ –љ–∞ –≤—Е–Њ–і STB —Б–Є–≥–љ–∞–ї–∞ –љ–Є–Ј–Ї–Њ–≥–Њ —Г—А–Њ–≤–љ—П –Љ–Є–Ї—А–Њ—Б—Е–µ–Љ–∞ —Е—А–∞–љ–Є—В –Є–љ—Д–Њ—А–Љ–∞—Ж–Є—О –њ—А–µ–і—Л–і—Г—Й–µ–≥–Њ —В–∞–Ї—В–∞; –њ—А–Є –њ–Њ–і–∞—З–µ –љ–∞ –≤—Е–Њ–і STB –њ–Њ–ї–Њ–ґ–Є—В–µ–ї—М–љ–Њ–≥–Њ –њ–µ—А–µ–њ–∞–і–∞ –Є–Љ–њ—Г–ї—М—Б–∞ –њ—А–Њ–Є—Б—Е–Њ–і–Є—В вАЬ–Ј–∞—Й–µ–ї–Ї–Є–≤–∞–љ–Є–µвАЭ –≤—Е–Њ–і–љ–Њ–є –Є–љ—Д–Њ—А–Љ–∞—Ж–Є–Є. –Т—Л—Е–Њ–і–љ—Л–µ –±—Г—Д–µ—А—Л —Г–њ—А–∞–≤–ї—П—О—В—Б—П —Б–Є–≥–љ–∞–ї–Њ–Љ –Ю–Х вАЬ—А–∞–Ј—А–µ—И–µ–љ–Є–µ –≤—Л—Е–Њ–і–∞вАЭ. –Я—А–Є –њ–Њ—Б—В—Г–њ–ї–µ–љ–Є–Є –љ–∞ –≤—Е–Њ–і –Ю–Х —Б–Є–≥–љ–∞–ї–∞ –≤—Л—Б–Њ–Ї–Њ–≥–Њ —Г—А–Њ–≤–љ—П –≤—Л—Е–Њ–і–љ—Л–µ –±—Г—Д–µ—А—Л –њ–µ—А–µ–≤–Њ–і—П—В—Б—П –≤ —Б–Њ—Б—В–Њ—П–љ–Є–µ вАЬ–≤—Л–Ї–ї—О—З–µ–љ–ЊвАЭ.

–§—Г–љ–Ї—Ж–Є–Њ–љ–∞–ї—М–љ–∞—П —Б—Е–µ–Љ–∞ –Љ–Є–Ї—А–Њ—Б—Е–µ–Љ—Л –Ъ–†580–Ш–†82.

–Э–∞–Ј–љ–∞—З–µ–љ–Є–µ –≤—Л–≤–Њ–і–Њ–≤ –Ш–° –Ъ–†580–Ш–†82.

-

–Э–Њ–Љ–µ—А –≤—Л–≤–Њ–і–∞

–Ю–±–Њ–Ј–љ–∞—З–µ–љ–Є–µ

–Э–∞–Ј–љ–∞—З–µ–љ–Є–µ

1-8

DI0-DI7

–Т—Е–Њ–і—Л —А–µ–≥–Є—Б—В—А–∞

9

OE

–†–∞–Ј—А–µ—И–µ–љ–Є–µ –≤—Л—Е–Њ–і–∞

10

GND

–Ю–±—Й–Є–є

11

STB

–°—В—А–Њ–±

19-12

D00-D07

–Т—Л—Е–Њ–і—Л —А–µ–≥–Є—Б—В—А–∞

20

UCC

–Я–Є—В–∞–љ–Є–µ

–Ґ–∞–±–ї–Є—Ж–∞ –Є—Б—В–Є–љ–љ–Њ—Б—В–Є.

-

–Т—Е–Њ–і –Ю–Х

–Т—Е–Њ–і STB

–Т—Е–Њ–і—Л DI

–Т—Л—Е–Њ–і—Л DO

0

1

1

1

0

1

0

0

0

0

–•

D00

1

–•

–•

Z

DOO-—Б–Њ—Б—В–Њ—П–љ–Є–µ –≤—Л—Е–Њ–і–∞ –≤ –њ—А–µ–і—Л–і—Г—Й–µ–Љ —В–∞–Ї—В–µ.

–•-–ї–Њ–≥–Є—З–µ—Б–Ї–Є–є —Г—А–Њ–≤–µ–љ—М –љ–∞ –≤—Е–Њ–і–µ –љ–µ –≤–ї–Є—П–µ—В –љ–∞ —Б–Њ—Б—В–Њ—П–љ–Є–µ –≤—Е–Њ–і–∞.

Z-—Б–Њ—Б—В–Њ—П–љ–Є–µ вАЬ–≤—Л–Ї–ї—О—З–µ–љ–ЊвАЭ.

4.2.–•–∞—А–∞–Ї—В–µ—А–Є—Б—В–Є–Ї–Є –Љ–Є–Ї—А–Њ—Б—Е–µ–Љ—Л –Ъ–†580–Ш–†82.

–І–Є—Б–ї–Њ —А–∞–Ј—А—П–і–Њ–≤ —А–µ–≥–Є—Б—В—А–∞ 8

–Ґ–Њ–Ї –њ–Њ—В—А–µ–±–ї–µ–љ–Є—П 160–Љ–Р.

–Т—Е–Њ–і–љ–Њ–є —В–Њ–Ї –љ–Є–Ј–Ї–Њ–≥–Њ —Г—А–Њ–≤–љ—П вЙ§ -0.2–Љ–Р.

–Т—Е–Њ–і–љ–Њ–є —В–Њ–Ї –≤—Л—Б–Њ–Ї–Њ–≥–Њ —Г—А–Њ–≤–љ—П вЙ§50–Љ–Ї–Р.

–Т—Л—Е–Њ–і–љ–Њ–µ –љ–∞–њ—А—П–ґ–µ–љ–Є–µ –љ–Є–Ј–Ї–Њ–≥–Њ —Г—А–Њ–≤–љ—П вЙ§0.45–Т.

–Т—Л—Е–Њ–і–љ–Њ–µ –љ–∞–њ—А—П–ґ–µ–љ–Є–µ –≤—Л—Б–Њ–Ї–Њ–≥–Њ —Г—А–Њ–≤–љ—П вЙ•2.4–Т.

–Т—Л—Е–Њ–і–љ–Њ–є —В–Њ–Ї –љ–Є–Ј–Ї–Њ–≥–Њ —Г—А–Њ–≤–љ—П –≤ —Б–Њ—Б—В–Њ—П–љ–Є–Є вАЬ–≤—Л–Ї–ї—О—З–µ–љ–ЊвАЭ вЙ§-50–Љ–Р.

–Т—Л—Е–Њ–і–љ–Њ–є —В–Њ–Ї –≤—Л—Б–Њ–Ї–Њ–≥–Њ —Г—А–Њ–≤–љ—П –≤ —Б–Њ—Б—В–Њ—П–љ–Є–Є вАЬ–≤—Л–Ї–ї—О—З–µ–љ–ЊвАЭ вЙ§50–Љ–Р.

–Т—А–µ–Љ—П –њ–µ—А–µ–і–∞—З–Є –Є–љ—Д–Њ—А–Љ–∞—Ж–Є–Є –Њ—В –≤—Е–Њ–і–∞ –і–Њ –≤—Л—Е–Њ–і–∞ вЙ§ 30–љ—Б.

–Т—А–µ–Љ—П —Ж–Є–Ї–ї–∞ вАЬ–Ј–∞–њ–Є—Б—М-—Б—З–Є—В—Л–≤–∞–љ–Є–µвАЭ 100–љ—Б.

–Т—А–µ–Љ—П –Ј–∞–і–µ—А–ґ–Ї–Є —А–∞—Б–њ—А–Њ—Б—В—А–∞–љ–µ–љ–Є—П –Є–љ—Д–Њ—А–Љ–∞—Ж–Є–Њ–љ–љ–Њ–≥–Њ —Б–Є–≥–љ–∞–ї–∞ –љ–∞ –≤—Л—Е–Њ–і–µ –Њ—В–љ–Њ—Б–Є—В–µ–ї—М–љ–Њ —Б–Є–≥–љ–∞–ї–∞ —Б—В—А–Њ–±–∞ вЙ§45–љ—Б.

–Т—А–µ–Љ—П –Ј–∞–і–µ—А–ґ–Ї–Є —А–∞—Б–њ—А–Њ—Б—В—А–∞–љ–µ–љ–Є—П –Є–љ—Д–Њ—А–Љ–∞—Ж–Є–Њ–љ–љ–Њ–≥–Њ —Б–Є–≥–љ–∞–ї–∞ –љ–∞ –≤—Л—Е–Њ–і–µ –Њ—В–љ–Њ—Б–Є—В–µ–ї—М–љ–Њ —Б–Є–≥–љ–∞–ї–∞ вАЬ—А–∞–Ј—А–µ—И–µ–љ–Є—П –≤—Л—Е–Њ–і–∞вАЭ –Њ—В10 –і–Њ 30–љ—Б.

–Т—А–µ–Љ—П —Б–Њ—Е—А–∞–љ–µ–љ–Є—П –Є–љ—Д–Њ—А–Љ–∞—Ж–Є–Њ–љ–љ–Њ–≥–Њ —Б–Є–≥–љ–∞–ї–∞ –љ–∞ –≤—Е–Њ–і–µ –Њ—В–љ–Њ—Б–Є—В–µ–ї—М–љ–Њ —Б–Є–≥–љ–∞–ї–∞ —Б—В—А–Њ–±–∞ вЙ•25–љ—Б.

–Ф–ї–Є—В–µ–ї—М–љ–Њ—Б—В—М –Є–Љ–њ—Г–ї—М—Б–∞ —Б–Є–≥–љ–∞–ї–∞ —Б—В—А–Њ–±–∞ вЙ•15–љ—Б.

–Ь–Є–љ–Є–Љ–∞–ї—М–љ–∞—П –і–ї–Є—В–µ–ї—М–љ–Њ—Б—В—М —В–∞–Ї—В–Њ–≤—Л—Е –Є–Љ–њ—Г–ї—М—Б–Њ–≤ 15–љ—Б.

–Т—Е–Њ–і–љ–∞—П –µ–Љ–Ї–Њ—Б—В—М 12–њ–§.

–Я–Њ—В—А–µ–±–ї—П–µ–Љ–∞—П –Љ–Њ—Й–љ–Њ—Б—В—М вЙ§ 800–Љ–Т—В.

–Э–∞–њ—А—П–ґ–µ–љ–Є–µ –њ–Є—В–∞–љ–Є—П +5–Т.

–Ь–Є–љ–Є–Љ–∞–ї—М–љ–∞—П –љ–∞—А–∞–±–Њ—В–Ї–∞ 50000—З.

–°—А–Њ–Ї —Б–Њ—Е—А–∞–љ—П–µ–Љ–Њ—Б—В–Є 12 –ї–µ—В.

5.–†–∞—Б—З–µ—В –љ–∞–і–µ–ґ–љ–Њ—Б—В–Є –±–ї–Њ–Ї–∞ –і–Є–љ–∞–Љ–Є—З–µ—Б–Ї–Њ–≥–Њ –Ю–Ч–£.

–Ф–ї—П –њ–Њ–≤—Л—И–µ–љ–Є—П –љ–∞–і–µ–ґ–љ–Њ—Б—В–Є –Ч–£ –њ—А–Є–Љ–µ–љ—П–µ—В—Б—П –Ї–Њ–і –•–µ–Љ–Љ–Є–љ–≥–∞, –Є—Б–њ—А–∞–≤–ї—П—О—Й–Є–є –Њ–і–љ–Њ—А–∞–Ј—А—П–і–љ—Г—О –Њ—И–Є–±–Ї—Г –≤ —Б–ї–Њ–≤–µ –Ч–£.

–Т –Ї–∞—З–µ—Б—В–≤–µ –њ–Њ–Ї–∞–Ј–∞—В–µ–ї–µ–є –љ–∞–і–µ–ґ–љ–Њ—Б—В–Є —И–Є—А–Њ–Ї–Њ –њ—А–Є–Љ–µ–љ—П—О—В –≤–µ—А–Њ—П—В–љ–Њ—Б—В—М –±–µ–Ј–Њ—В–Ї–∞–Ј–љ–Њ–є —А–∞–±–Њ—В—Л –†(t) –Ј–∞ –≤—А–µ–Љ—П t –Є —Б—А–µ–і–љ—О—О –љ–∞—А–∞–±–Њ—В–Ї—Г –і–Њ –Њ—В–Ї–∞–Ј–∞ –Ґ—Б—А.

–Т—Л—З–Є—Б–ї—П–µ—В—Б—П –Ї–Њ—Н—Д—Д–Є—Ж–Є–µ–љ—В –ЪDL, —Г—З–Є—В—Л–≤–∞—О—Й–Є–є —Н–Ї–≤–Є–≤–∞–ї–µ–љ—В–љ—Г—О –і–Њ–Ј—Г –Њ—В–Ї–∞–Ј–Њ–≤ —А–∞–Ј–ї–Є—З–љ—Л—Е —В–Є–њ–Њ–≤ –≤ –Ј–∞–≤–Є—Б–Є–Љ–Њ—Б—В–Є –Њ—В —А–∞–Ј—А—П–і–љ–Њ—Б—В–Є –Є—Б–њ—А–∞–≤–ї—П–µ–Љ–Њ–є –Њ—И–Є–±–Ї–Є L. –Я—А–Є –Њ—В–Ї–∞–Ј–∞—Е –С–Ш–° –Ч–£ –Љ–Њ–ґ–љ–Њ –≤—Л–і–µ–ї–Є—В—М —Б–ї–µ–і—Г—О—Й–Є–µ –Њ—Б–љ–Њ–≤–љ—Л–µ —В–Є–њ—Л –Њ—В–Ї–∞–Ј–Њ–≤: –Њ—В–Ї–∞–Ј –≤—Б–µ–є –Љ–Є–Ї—А–Њ—Б—Е–µ–Љ—Л (–і–Њ–ї—П —В–∞–Ї–Є—Е –Њ—В–Ї–∞–Ј–Њ–≤ –∞1), –Њ—В–Ї–∞–Ј —Б—В—А–Њ–Ї–Є (–і–Њ–ї—П —В–∞–Ї–Є—Е –Њ—В–Ї–∞–Ј–Њ–≤ –∞2), –Њ—В–Ї–∞–Ј —Б—В–Њ–ї–±—Ж–∞ (–і–Њ–ї—П —В–∞–Ї–Є—Е –Њ—В–Ї–∞–Ј–Њ–≤ –∞3), –Њ—В–Ї–∞–Ј –≠–Я (–і–Њ–ї—П —В–∞–Ї–Є—Е –Њ—В–Ї–∞–Ј–Њ–≤ –∞4)

–∞1=2 –∞2=14

–∞3=17 –∞4=42

–µ—Б–ї–Є –Ї–Њ–і –Є—Б–њ—А–∞–≤–ї—П–µ—В –Њ–і–љ–Њ—А–∞–Ј—А—П–і–љ—Г—О –Њ—И–Є–±–Ї—Г (L=1):

–≥–і–µ: –ЪM- –Ї–Њ—Н—Д—Д–Є—Ж–Є–µ–љ—В, —Г—З–Є—В—Л–≤–∞—О—Й–Є–є —З–Є—Б–ї–Њ —А–∞–Ј—А—П–і–Њ–≤ –С–Ш–° –Ч–£ (–µ—Б–ї–Є —З–Є—Б–ї–Њ —А–∞–Ј—А—П–і–Њ–≤ nM =1, —В–Њ –Ъ–Ь=0, –Є–љ–∞—З–µ –Ъ–Ь=1); KZ- –Ї–Њ—Н—Д—Д–Є—Ж–Є–µ–љ—В, —Г—З–Є—В—Л–≤–∞—О—Й–Є–є —В–Є–њ –Ч–£ (–і–ї—П –Я–Ч–£ –ЪZ=0.5, –∞ –і–ї—П –Ю–Ч–£ –ЪZ=1); E- –Є–љ—Д–Њ—А–Љ–∞—Ж–Є–Њ–љ–љ–∞—П –µ–Љ–Ї–Њ—Б—В—М –С–Ш–° –Ч–£ (–≤ –±–Є—В–∞—Е).

–Ю–њ—А–µ–і–µ–ї–µ–љ–Є–µ –≤–µ—А–Њ—П—В–љ–Њ—Б—В–Є –±–µ–Ј–Њ—В–Ї–∞–Ј–љ–Њ–є —А–∞–±–Њ—В—Л –Ч–£ –†(t).

–Т–µ—А–Њ—П—В–љ–Њ—Б—В—М –±–µ–Ј–Њ—В–Ї–∞–Ј–љ–Њ–є —А–∞–±–Њ—В—Л вАУ —Н—В–Њ –≤–µ—А–Њ—П—В–љ–Њ—Б—В—М —В–Њ–≥–Њ, —З—В–Њ –≤ –њ—А–µ–і–µ–ї–∞—Е –Ј–∞–і–∞–љ–љ–Њ–є –љ–∞—А–∞–±–Њ—В–Ї–Є, —В.–µ. –Ј–∞–і–∞–љ–љ–Њ–≥–Њ –Є–љ—В–µ—А–≤–∞–ї–∞ –≤—А–µ–Љ–µ–љ–Є , –Њ—В–Ї–∞–Ј –Њ–±—К–µ–Ї—В–∞ –љ–µ –≤–Њ–Ј–љ–Є–Ї–љ–µ—В.

–≥–і–µ: nO- —А–∞–Ј—А—П–і–љ–Њ—Б—В—М —Б–ї–Њ–≤–∞ –Ч–£; ќї–Ь- –Є–љ—В–µ–љ—Б–Є–≤–љ–Њ—Б—В—М –Њ—В–Ї–∞–Ј–Њ–≤ –С–Ш–° –Ч–£;

NR- —З–Є—Б–ї–Њ —Б—В—А–Њ–Ї –≤ –С–Ш–° –Ч–£ –≤ –Ч–£; ќїZ- –Є–љ—В–µ–љ—Б–Є–≤–љ–Њ—Б—В—М –Њ—В–Ї–∞–Ј–Њ–≤ —Б—Е–µ–Љ –Њ–±—А–∞–Љ–ї–µ–љ–Є—П –Є —Н–ї–µ–Љ–µ–љ—В–Њ–≤ –Ї–Њ–љ—Б—В—А—Г–Ї—Ж–Є–Є –Ч–£ (–љ–∞–њ—А–Є–Љ–µ—А, –њ–∞–µ–Ї, –Ї–Њ–љ—В–∞–Ї—В–Њ–≤ —Б–Њ–µ–і–Є–љ–Є—В–µ–ї–µ–є, –ї–Є–љ–Є–є —Б–≤—П–Ј–Є, –њ–µ—З–∞—В–љ–Њ–≥–Њ –Љ–Њ–љ—В–∞–ґ–∞ –Є —В.–њ.)

–Ъ–†1, –Ъ–†2- –њ–Њ–њ—А–∞–≤–Њ—З–љ—Л–µ –Ї–Њ—Н—Д—Д–Є—Ж–Є–µ–љ—В—Л, –Є—Б–њ–Њ–ї—М–Ј—Г–µ–Љ—Л–µ –і–ї—П –Ї–Њ–Љ–њ–µ–љ—Б–∞—Ж–Є–Є –њ–Њ–≥—А–µ—И–љ–Њ—Б—В–µ–є –≤ –Ч–£ —Б –±–Њ–ї—М—И–Є–Љ –Є —Б—А–µ–і–љ–Є–Љ —З–Є—Б–ї–Њ–Љ –С–Ш–° –Ч–£. –Ъ–†2- –Ј–љ–∞—З–µ–љ–Є–µ –Ї–Њ—Н—Д—Д–Є—Ж–Є–µ–љ—В–∞ –Њ–њ—А–µ–і–µ–ї—П–µ—В—Б—П –≤ –Ј–∞–≤–Є—Б–Є–Љ–Њ—Б—В–Є –Њ—В —В–Є–њ–∞ –Ч–£ –Є —А–∞–Ј—А—П–і–љ–Њ—Б—В–Є –Є—Б–њ—А–∞–≤–ї—П–µ–Љ–Њ–є –Њ—И–Є–±–Ї–Є

( –і–ї—П –Ю–Ч–£ —Б L=1 –µ—Б–ї–Є nM=1 —В–Њ –Ъ–†2=1); –Ъ–†1- –Ј–љ–∞—З–µ–љ–Є–µ –Ї–Њ—Н—Д—Д–Є—Ж–Є–µ–љ—В–∞ –≤ –Ј–∞–≤–Є—Б–Є–Љ–Њ—Б—В–Є –Њ—В nM (–њ—А–Є nM=1 —В–Њ –Ъ–†1=1).

–Т—Л—З–Є—Б–ї–µ–љ–Є–µ –Ј–љ–∞—З–µ–љ–Є—П –њ–∞—А–∞–Љ–µ—В—А–∞ –•L, –Њ–њ—А–µ–і–µ–ї—П—О—Й–µ–≥–Њ

—Б–Њ–Њ—В–љ–Њ—И–µ–љ–Є–µ –Љ–µ–ґ–і—Г –Є–љ—В–µ–љ—Б–Є–≤–љ–Њ—Б—В—М—О –Њ—В–Ї–∞–Ј–Њ–≤ —Н–ї–µ–Љ–µ–љ—В–Њ–≤ –Ч–£, –Њ—Е–≤–∞—З–µ–љ–љ—Л—Е –Є –љ–µ–Њ—Е–≤–∞—З–µ–љ—Л—Е –Ї–Њ—А—А–µ–Ї—В–Є—А—Г—О—Й–Є–Љ –Ї–Њ–і–Њ–Љ:

–Ю–њ—А–µ–і–µ–ї–µ–љ–Є–µ —Б—А–µ–і–љ–µ–є –љ–∞—А–∞–±–Њ—В–Ї–Є –і–Њ –Њ—В–Ї–∞–Ј–∞ –Ґ—Б—А.

–°—А–µ–і–љ—П—П –љ–∞—А–∞–±–Њ—В–Ї–∞ –і–Њ –Њ—В–Ї–∞–Ј–∞, –Є–ї–Є —Б—А–µ–і–љ—П—П –≤—А–µ–Љ—П –±–µ–Ј–Њ—В–Ї–∞–Ј–љ–Њ–є —А–∞–±–Њ—В—Л- —Н—В–Њ –Њ–ґ–Є–і–∞–µ–Љ–∞—П –љ–∞—А–∞–±–Њ—В–Ї–∞ –Њ–±—К–µ–Ї—В–∞ –і–Њ –њ–µ—А–≤–Њ–≥–Њ –Њ—В–Ї–∞–Ј–∞.

–≥–і–µ: bLi- –Ї–Њ—Н—Д—Д–Є—Ж–Є–µ–љ—В—Л —А–∞–Ј–ї–Њ–ґ–µ–љ–Є—П –њ–Њ–ї–Є–љ–Њ–Љ–Њ–≤

–і–ї—П L=1 bL1=1,2533 bL2= -1,0006 bL3=0,6308

6.–†–∞—Б—З–µ—В –њ–Њ—В—А–µ–±–ї—П–µ–Љ–Њ–є –Љ–Њ—Й–љ–Њ—Б—В–Є –±–ї–Њ–Ї–Њ–Љ –Ю–Ч–£.

–Ь—Й–љ–Њ—Б—В—М –њ–Њ—В—А–µ–±–ї—П–µ–Љ–∞—П –Љ–Є–Ї—А–Њ—Б—Е–µ–Љ–Њ–є –Ю–Ч–£ –Ъ565–†–£3–У –≤ —А–µ–ґ–Є–Љ–µ —Е—А–∞–љ–µ–љ–Є—П –Є–љ—Д–Њ—А–Љ–∞—Ж–Є–Є, –Њ—Ж–µ–љ–Є–≤–∞–µ—В—Б—П –њ—А–Є —Б–ї–µ–і—Г—О—Й–Є—Е –Є—Б—Е–Њ–і–љ—Л—Е –і–∞–љ–љ—Л—Е: –†–∞=0.46–Т—В, –†–Њ=0.04–Т—В, m—А=128, –Ґ—Ж –Љ–Є–љ=0.37–Љ–Ї—Б, –Ґ—А–µ–≥=2000–Љ–Ї—Б -–њ–Њ —Д–Њ—А–Љ—Г–ї–µ:

–†—Е—А.—А–µ–≥.пВї–†–Њ+(–†–∞-–†–Њ)(–Ґ—Ж.–Љ–Є–љ m—А/–Ґ—А–µ–≥)=0.04+(0.46-0.04)(128пГЧ0.37/2000)=0.049 –Т—В

–≥–і–µ: –†–∞- –Љ–Њ—Й–љ–Њ—Б—В—М –њ–Њ—В—А–µ–±–ї—П–µ–Љ–∞—П –Ю–Ч–£ –≤ —А–µ–ґ–Є–Љ–µ —Б—З–Є—В—Л–≤–∞–љ–Є—П, –Ј–∞–њ–Є—Б–Є; –†–Њ-–Љ–Њ—Й–љ–Њ—Б—В—М –њ–Њ—В—А–µ–±–ї—П–µ–Љ–∞—П –Ю–Ч–£ –≤ —А–µ–ґ–Є–Љ–µ —Е—А–∞–љ–µ–љ–Є—П; m—А-–Ї–Њ–ї–Є—З–µ—Б—В–≤–Њ —Б—В—А–Њ–Ї –≤ –Љ–∞—В—А–Є—Ж–µ –Ю–Ч–£; –Ґ—Ж.–Љ–Є–љ-–Љ–Є–љ–Є–Љ–∞–ї—М–љ–Њ–µ –≤—А–µ–Љ—П —Ж–Є–Ї–ї–∞ –Њ–±—А–∞—Й–µ–љ–Є—П –Ї –Љ–Њ–і—Г–ї—О –Ю–Ч–£; –Ґ—А–µ–≥-–њ–µ—А–Є–Њ–і —А–µ–≥–µ–љ–µ—А–∞—Ж–Є–Є, –Њ–њ—А–µ–і–µ–ї—П—О—Й–Є–є –Љ–∞–Ї—Б–Є–Љ–∞–ї—М–љ—Л–є –Є–љ—В–µ—А–≤–∞–ї –≤—А–µ–Љ–µ–љ–Є –Љ–µ–ґ–і—Г –і–≤—Г–Љ—П –Њ–±—А–∞—Й–µ–љ–Є—П–Љ–Є –њ–Њ –Ї–∞–ґ–і–Њ–Љ—Г –∞–і—А–µ—Б—Г –і–ї—П –≤–Њ—Б—В–∞–љ–Њ–≤–ї–µ–љ–Є—П —Е—А–∞–љ–Є–Љ–Њ–є –Є–љ—Д–Њ—А–Љ–∞—Ж–Є–Є.

–Ь–Њ—Й–љ–Њ—Б—В—М –њ–Њ—В—А–µ–±–ї—П–µ–Љ–∞—П –Љ–Є–Ї—А–Њ—Б—Е–µ–Љ–∞–Љ–Є –Ю–Ч–£ –≤ –±–ї–Њ–Ї–µ –≤ —А–µ–ґ–Є–Љ–µ —Б—З–Є—В—Л–≤–∞–љ–Є—П –Є–ї–Є –Ј–∞–њ–Є—Б–Є –Є–љ—Д–Њ—А–Љ–∞—Ж–Є–Є –Њ—Ж–µ–љ–Є–≤–∞–µ—В—Б—П –њ—А–Є –Я–Њ=8 –Є –Я–∞=8 –њ–Њ —Д–Њ—А–Љ—Г–ї–µ:

–†–Љ–њ=–†–∞пГЧ–Я–∞+–†—Е—А.—А–µ–≥(–Я–Њ-–Я–∞)=0.46пГЧ8+0.049(8-8)=1.84 –Т—В

–≥–і–µ: –Я–Њ- –Њ–±—Й–µ–µ —З–Є—Б–ї–Њ –Љ–Є–Ї—А–Њ—Б—Е–µ–Љ –Ю–Ч–£ –≤ –±–ї–Њ–Ї–µ; –Я–∞- —З–Є—Б–ї–Њ –Љ–Є–Ї—А–Њ—Б—Е–µ–Љ –Ю–Ч–£, –љ–∞—Е–Њ–і—П—Й–Є—Е—Б—П –≤ –∞–Ї—В–Є–≤–љ–Њ–Љ —А–µ–ґ–Є–Љ–µ.

–Ь–Њ—Й–љ–Њ—Б—В—М –њ–Њ—В—А–µ–±–ї—П–µ–Љ–∞—П –Љ–Є–Ї—А–Њ—Б—Е–µ–Љ–∞–Љ–Є –Ю–Ч–£ –≤ –±–ї–Њ–Ї–µ –≤ —А–µ–ґ–Є–Љ–µ —Е—А–∞–љ–µ–љ–Є—П –Є–љ—Д–Њ—А–Љ–∞—Ж–Є–Є –Њ–њ—А–µ–і–µ–ї—П–µ—В—Б—П –Ї–∞–Ї:

–†–Љ–њ.—А–µ–≥=–†—Е—А.—А–µ–≥пГЧ–Я–Њ=0.049пГЧ8=0.39 –Т—В.

–Ь–Њ—Й–љ–Њ—Б—В—М –њ–Њ—В—А–µ–±–ї—П–µ–Љ–∞—П –±–ї–Њ–Ї–Њ–Љ –Ю–Ч–£ –≤ —А–µ–ґ–Є–Љ–µ —Е—А–∞–љ–µ–љ–Є—П –Є–љ—Д–Њ—А–Љ–∞—Ж–Є–Є:

–†–±.—А–µ–≥=–†–Љ–њ.—А–µ–≥+пГ•–†—Г=0.39+0.0165пГЧ4+0.8=1.26 –Т—В.

–≥–і–µ: –†—Г- –Љ–Њ—Й–љ–Њ—Б—В—М –њ–Њ—В—А–µ–±–ї—П–µ–Љ–∞—П —Б—Е–µ–Љ–∞–Љ–Є —Г–њ—А–∞–≤–ї–µ–љ–Є—П.

–Ь–Њ—Й–љ–Њ—Б—В—М –њ–Њ—В—А–µ–±–ї—П–µ–Љ–∞—П –±–ї–Њ–Ї–Њ–Љ –Ю–Ч–£ –≤ —А–µ–ґ–Є–Љ–µ –Ј–∞–њ–Є—Б–Є, —Б—З–Є—В—Л–≤–∞–љ–Є—П –Є–љ—Д–Њ—А–Љ–∞—Ж–Є–Є:

–†–±=–†–Љ–њ+пГ•–†—Г=1.84+0.0165пГЧ4+0.8=2.7 –Т—В.

–І—В–Њ–±—Л –њ–Њ–ї—Г—З–Є—В—М —Н–ї–µ–Ї—В—А–Є—З–µ—Б–Ї—Г—О , –њ—А–Є–љ—Ж–Є–њ–Є–∞–ї—М–љ—Г—О –Є –≤—А–µ–Љ–µ–љ–љ—Л–µ –і–Є–∞–≥—А–∞–Љ–Љ—Л –њ—А–Њ—Ж–µ—Б—Б–Њ–≤ –Њ–±—А–∞—В–Є—В–µ—Б—М –њ–Њ –∞–і—А–µ—Б—Г tipa-iorsh@mtu-net.ru

пїњ