Компьютерная схемотехника

Компьютерная схемотехника

Содержание

1. ВВЕДЕНИЕ

2. ДИСКРЕТИЗАЦИЯ АНАЛОГОВЫХ СИГНАЛОВ

2.1 Квантование по уровню

2.2 Квантование по времени

2.3 Квантование по уровню и по времени

2.3.1 Расчет погрешности АЦП

2.3.2 Выбор величины шага квантования по времени

3. ПРИМЕНЕНИЕ АЛГЕБРЫ ЛОГИКИ (БУЛЕВОЙ АЛГЕБРЫ) ПРИ АНАЛИЗЕ И СИНТЕЗЕ ЦИФРОВЫХ ЭЛЕКТРОННЫХ УСТРОЙСТВ

3.1 Определение и способы задания переключательных функций

3.2 Переключательные функции одной переменной (n=1)

3.3 Переключательные функции двух переменных (n=2)

3.4 Базисные логические функции

3.5 Принцип двойственности булевой алгебры

3.6 Основные тождества булевой алгебры

3.7 Основные законы и теоремы булевой алгебры

3.7.1 Законы

3.7.2 Теоремы

3.8 Совершенная дизъюнктивная нормальная форма (СДНФ) записи булевых выражений

3.9 Дизъюнктивная нормальная форма (ДНФ)

3.10 Совершенная конъюнктивная нормальная форма (СКНФ) записи булевых выражений

3.11 Конъюнктивная нормальная форма (КНФ)

3.12 Минимизация логических функций

3.12.1 Алгебраический способ минимизации ПФ

3.12.2 Минимизация ПФ с использованием диаграмм Вейча (карт Карно)

3.12.2.1 Минимизация ПФ с помощью диаграмм Вейча

3.12.2.1.1 Общие правила минимизации

3.12.2.1.2 Примеры минимизации ПФ с помощью диаграмм Вейча

3.12.2.2 Минимизация ПФ с помощью карт Карно

4. ЛОГИЧЕСКИЕ ЭЛЕМЕНТЫ

4.1 Инвертор (логический элемент НЕ)

4.2 Конъюнктор (логический элемент И)

4.3 Дизъюнктор (логический элемент ИЛИ)

4.4 Повторитель

4.5 И–НЕ

4.6 ИЛИ–НЕ

4.7 Исключающее ИЛИ

4.8 Сложение по модулю два (нечетность)

4.9 Сложение по модулю два с отрицанием (четность)

4.10 Эквивалентность

4.11 Неэквивалентность

4.12 И–ИЛИ–НЕ

4.13 Запрет

4.14 Логические элементы с открытым коллектором

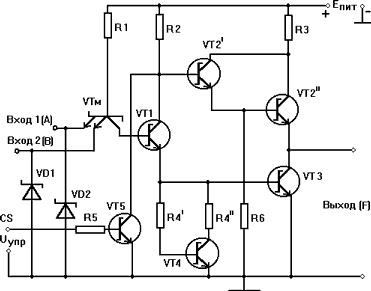

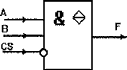

4.15 Логические элементы с третьим состоянием

5. РЕАЛИЗАЦИЯ ЛОГИЧЕСКИХ ФУНКЦИЙ в разных базисах

5.1 Базисные наборы ЛЭ и их взаимосвязь

5.2 Реализация логических функций в различных базисах

5.2.1 Реализация элемента “Равнозначность” (исключающее ИЛИ - НЕ)

5.2.2 Реализация элемента “Неравнозначность” (исключающее ИЛИ, сумма по модулю два)

5.2.3 Реализация элемента “Запрет”

5.2.4 Реализация многобуквенных логических функций на элементах с небольшим количеством входов

6. ПАРАМЕТРЫ И ХАРАКТЕРИСТИКИ ЦИФРОВЫХ ИНТЕГРАЛЬНЫХ МИКРОСХЕМ (ИМС)

6.1 Коэффициент объединения по входу (Коб)

6.2 Коэффициент разветвления по выходу (Краз)

6.3 Статические характеристики

6.4 Помехоустойчивость

6.5 Динамические характеристики и параметры

6.6 Вид реализуемой логической функции

6.7 Потребляемые токи и мощность

6.8 Входные и выходные токи, напряжения

6.9 Пороговые напряжения

6.10 Допустимые значения основных параметров

7. БАЗОВЫЕ ЛОГИЧЕСКИЕ ЭЛЕМЕНТЫ

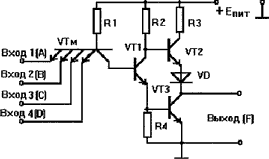

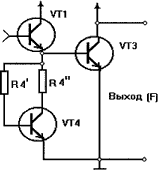

7.1 Базовый ТТЛ (ТТЛШ) - элемент И-НЕ

7.2 Базовый ЭСЛ - элемент ИЛИ/ИЛИ-НЕ

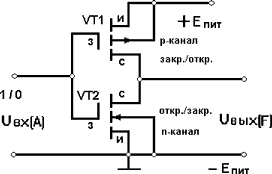

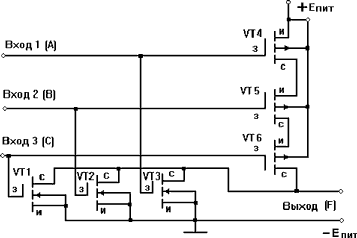

7.3 Базовый КМОП-элемент ИЛИ-НЕ

8. ГЕНЕРАТОРЫ ТАКТОВЫХ ИМПУЛЬСОВ (ГТИ) на логических элементах

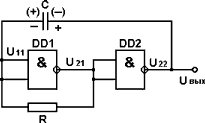

8.1 ГТИ на двух инверторах

8.2 ГТИ на 3-х инверторах

9. ФУНКЦИОНАЛЬНЫЕ УСТРОЙСТВА КОМПЬЮТЕРНОЙ (ЦИФРОВОЙ) ЭЛЕКТРОНИКИ

9.1 Комбинационные цифровые устройства (КЦУ)

9.1.1 Анализ и синтез КЦУ

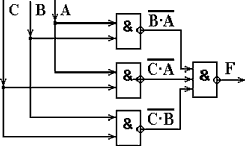

9.1.1.1 Анализ КЦУ

9.1.1.2 Синтез КЦУ

9.1.2 Типовые КЦУ

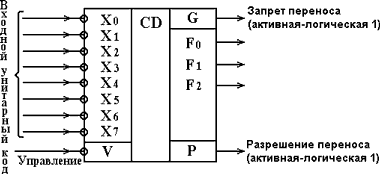

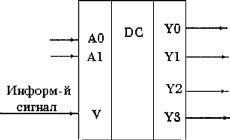

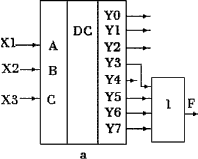

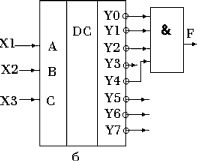

9.1.2.1 Шифраторы и дешифраторы

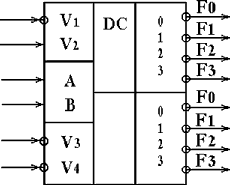

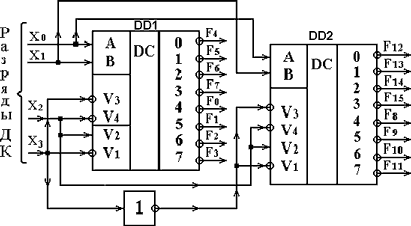

9.1.2.1.1 Шифраторы двоичного кода

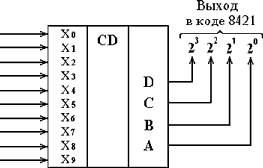

9.1.2.1.2 Шифраторы двоично-десятичного кода

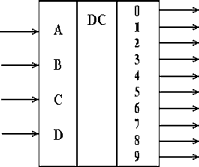

9.1.2.1.3 Дешифраторы двоичного кода

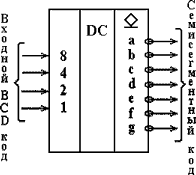

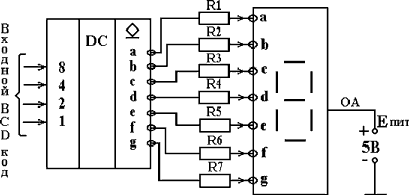

9.1.2.1.4 Дешифратор BCD-кода в семисегментный код

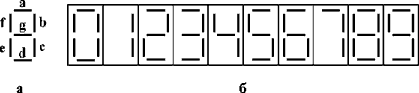

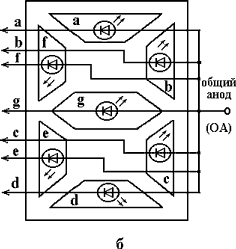

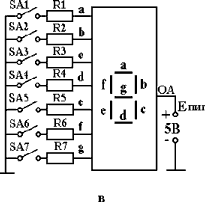

9.1.2.1.4.1 Семисегментные индикаторы на светодиодах

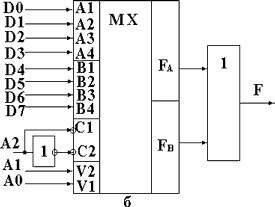

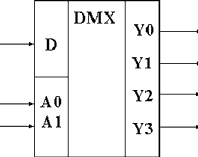

9.1.2.2 Мультиплексоры и демультиплексоры

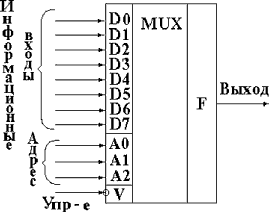

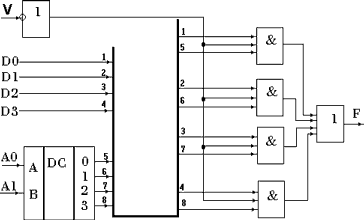

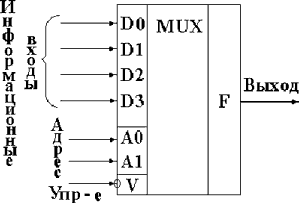

9.1.2.2.1 Мультиплексоры

9.1.2.2.2 Демультиплексоры

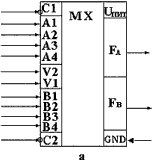

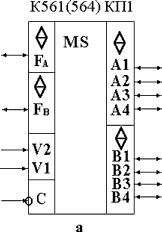

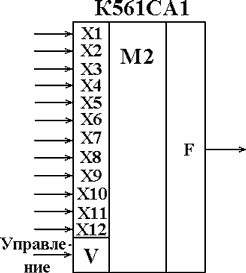

9.1.2.2.3 Мультиплексоры–селекторы (мультиплексоры-демультиплексоры)

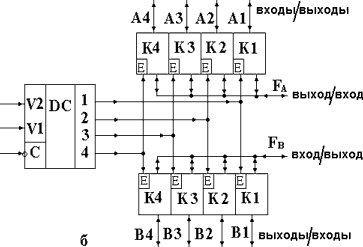

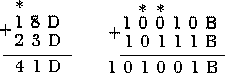

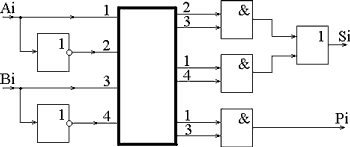

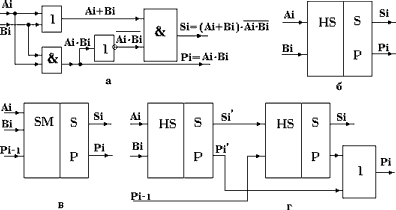

9.1.2.3 Сумматоры и полусумматоры

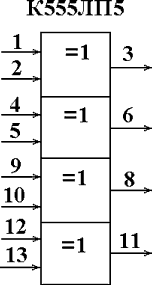

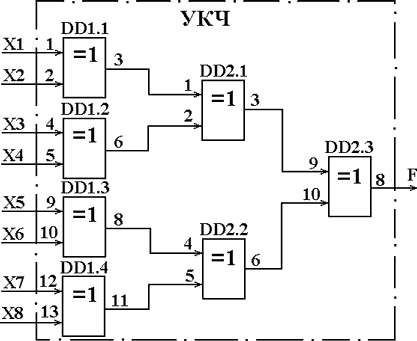

9.1.2.4 Устройства контроля четности (УКЧ)

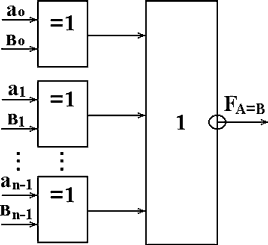

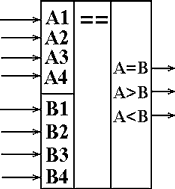

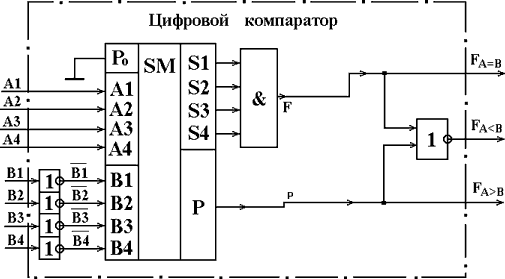

9.1.2.5 Цифровые компараторы

9.1.3 Использование для проектирования КЦУ мультиплексоров, дешифраторов и постоянных запоминающих устройств

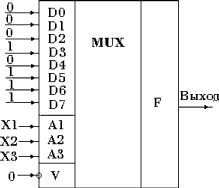

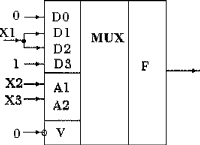

9.1.3.1 Построение КЦУ на мультиплексорах

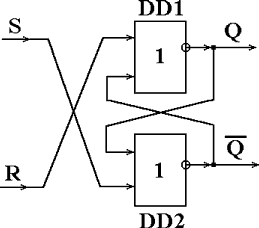

9.1.3.2 Построение КЦУ на дешифраторах

9.1.3.3 Построение КЦУ на постоянном запоминающем устройстве (ПЗУ)

9.2 Последовательностные цифровые устройства

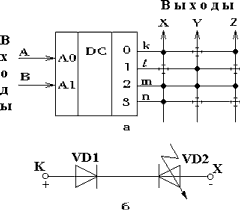

9.2.1 Триггеры

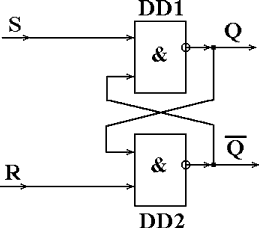

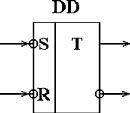

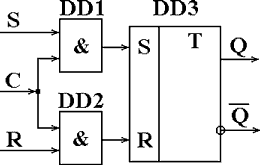

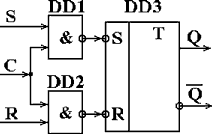

9.2.1.1 Триггеры на логических элементах

9.2.1.1.1 RS - триггеры

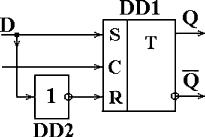

9.2.1.1.1.1 Асинхронные RS - триггеры

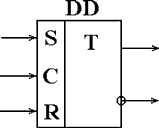

9.2.1.1.1.2 Синхронные RS - триггеры

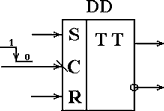

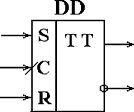

9.2.1.1.2 Т-триггеры (триггеры со счетным входом)

9.2.1.1.3 D-триггеры (триггеры задержки)

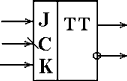

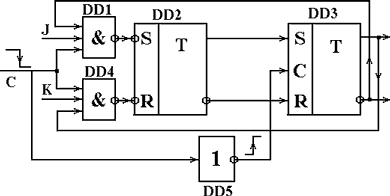

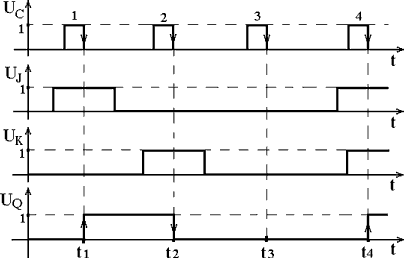

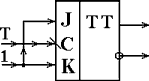

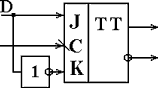

9.2.1.1.4 JK-триггеры

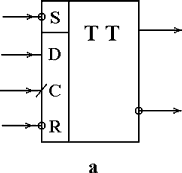

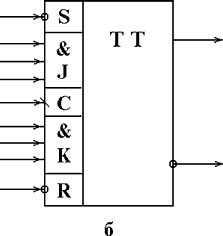

9.2.1.2 Триггеры в интегральном исполнении

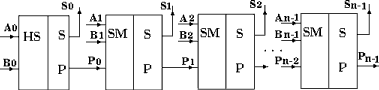

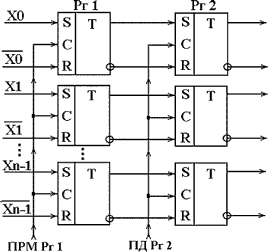

9.2.2 Регистры

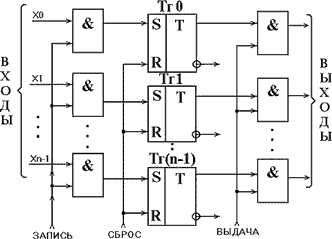

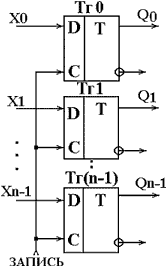

9.2.2.1 Параллельные регистры

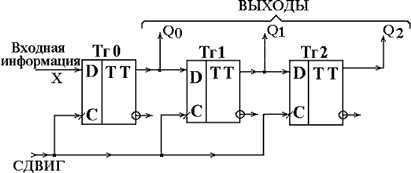

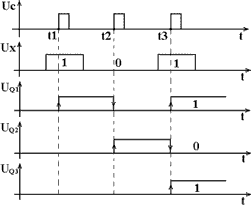

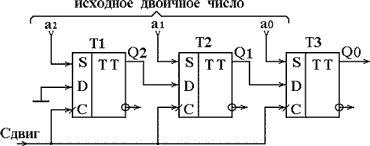

9.2.2.2 Последовательные (сдвигающие) регистры

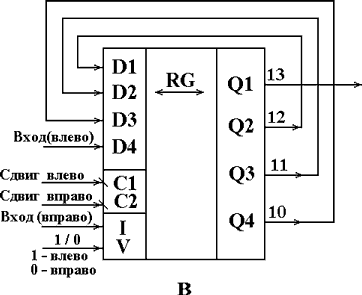

9.2.2.3 Регистры сдвига

9.2.2.4 Последовательно-параллельные и параллельно-последовательные регистры

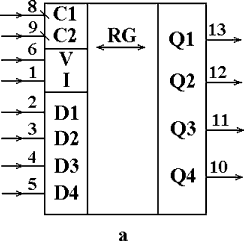

9.2.2.5 Регистры в интегральном исполнении

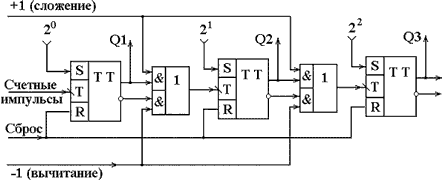

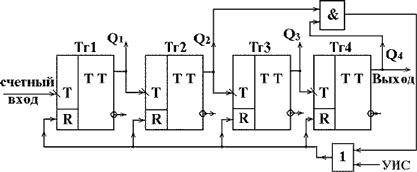

9.2.3.1 Асинхронный суммирующий двоичный счетчик с последовательным переносом

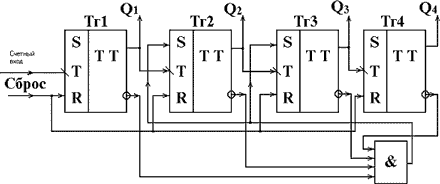

9.2.3.2 Асинхронный вычитающий двоичный счетчик с последовательным переносом

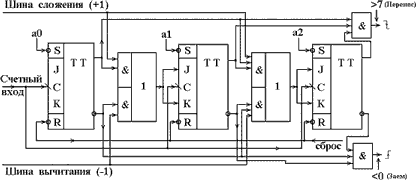

9.2.3.3 Асинхронные реверсивные двоичные счетчики с последовательным переносом

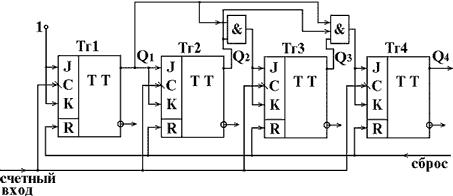

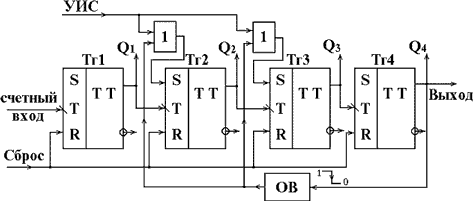

9.2.3.4 Синхронный счетчик со сквозным переносом

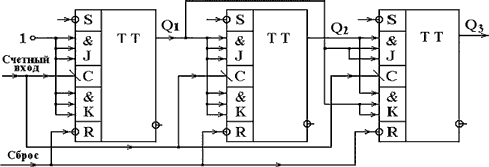

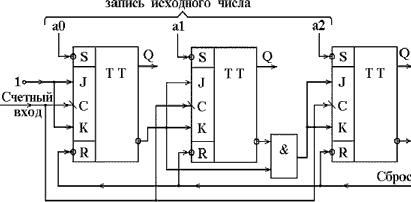

9.2.3.5 Десятичные счетчики

9.2.3.6 Счетчики в интегральном исполнении

9.2.4 Делители частоты

9.2.5 Распределители

10. СВЯЗЬ МП-РА И ОМЭВМ С АНАЛОГОВЫМ ОБЪЕКТОМ УПРАВЛЕНИЯ И С ПК

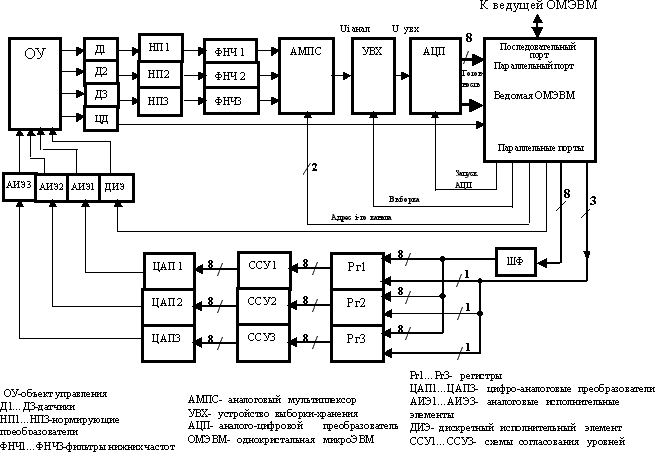

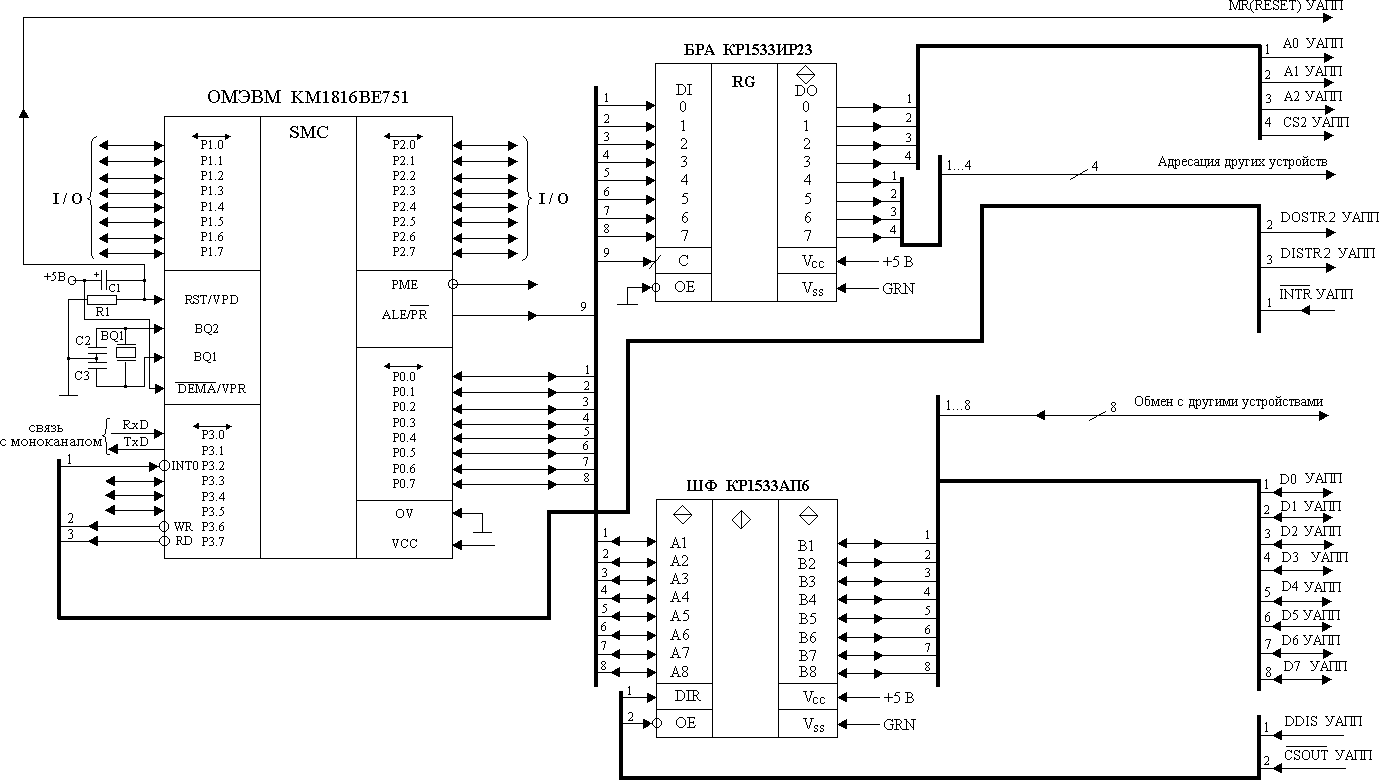

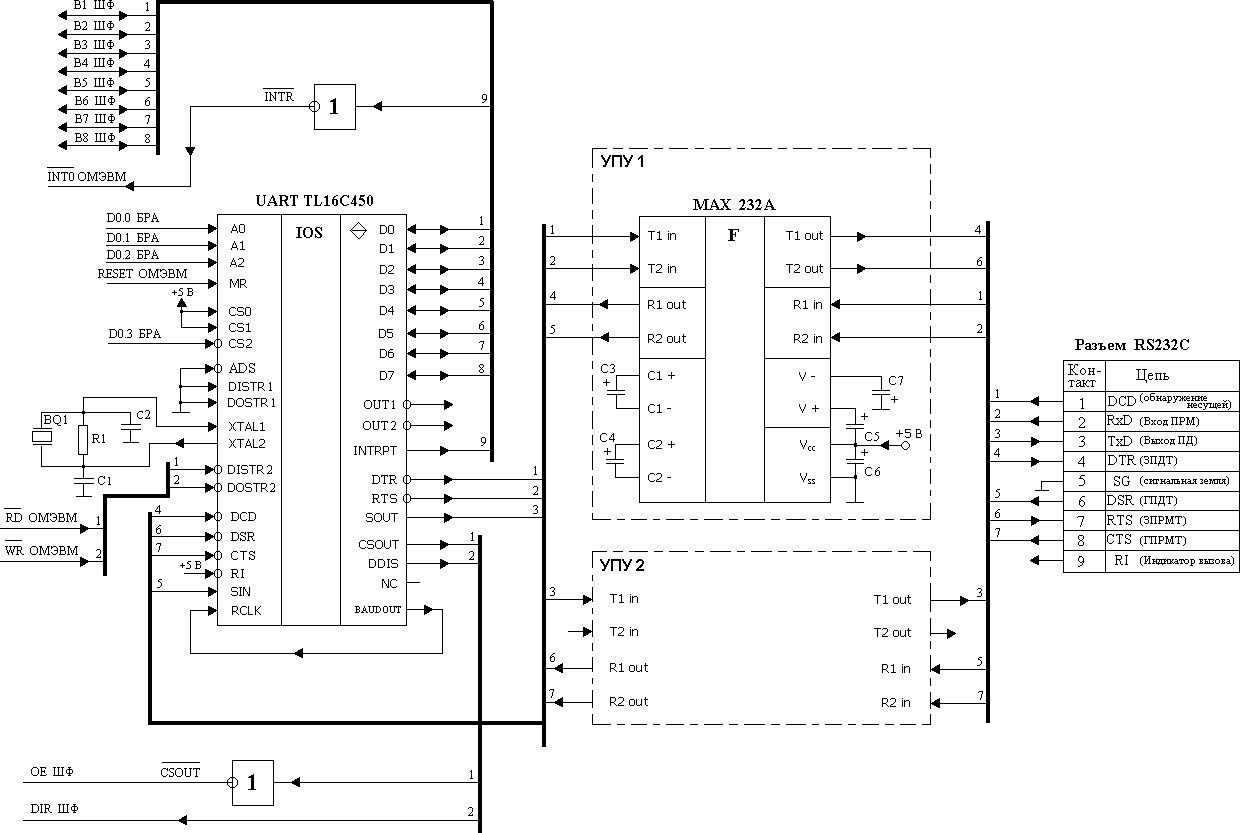

10.1 Структура типичной локальной микропроцессорной системы управления (ЛМПСУ)

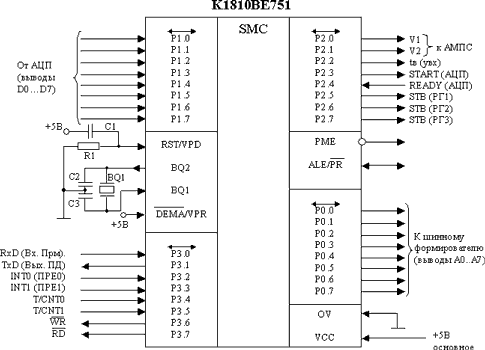

10.1.1 Назначение и схемная реализация отдельных узлов ЛМПСУ

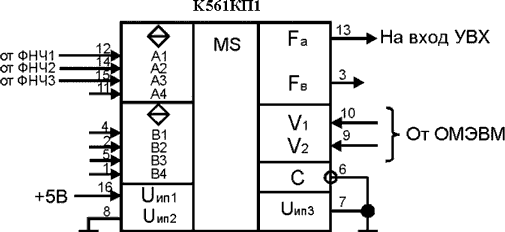

10.1.1.1 Аналоговый мультиплексор (АМПС)

10.1.1.2 Устройство выборки-хранения (УВХ)

10.1.1.3 Аналого-цифровой преобразователь (АЦП)

10.1.1.4 Ведомая однокристальная микроЭВМ (ОМЭВМ)

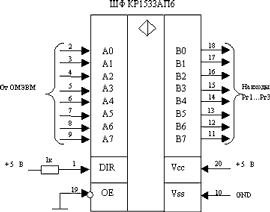

10.1.1.5 Шинный формирователь (ШФ)

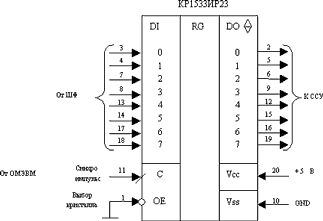

10.1.1.6 Регистры (Рг1...Рг3)

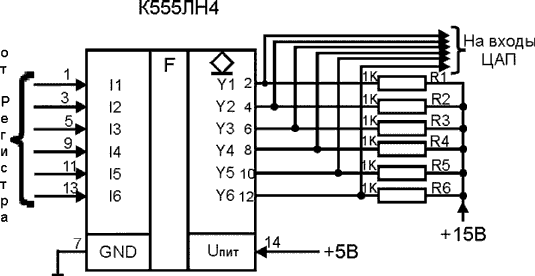

10.1.1.7 Схемы согласования уровней (ССУ1...ССУ3)

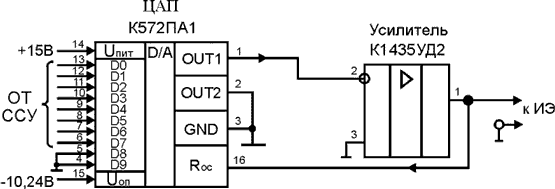

10.1.1.8 Цифро-аналоговые преобразователи (ЦАП1...ЦАП3)

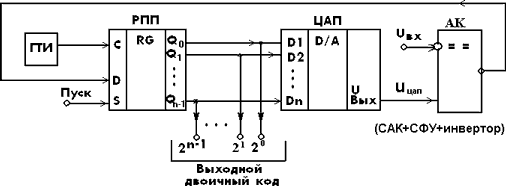

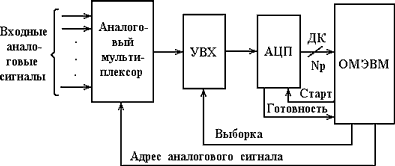

10.2 Применение АЦП и УВХ при вводе аналоговой информации в МПС

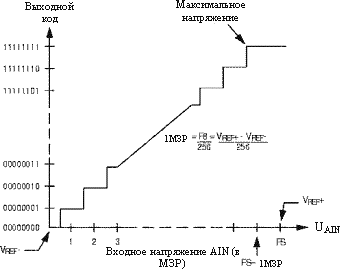

10.2.1 Расчет АЦП

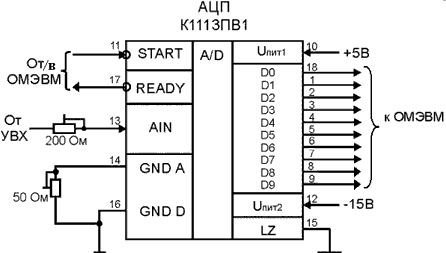

10.2.2 АЦП К1113 ПВ1

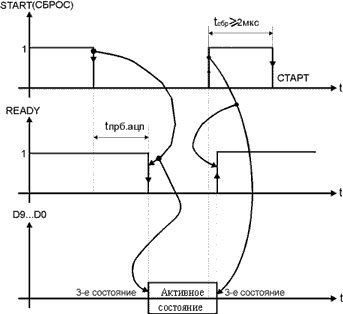

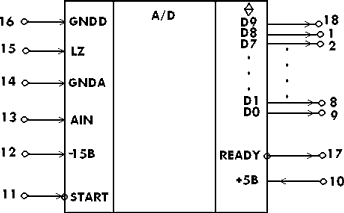

10.2.2.1 Описание микросхемы К1113 ПВ1

10.2.2.2 Расчет микросхемы К1113 ПВ1

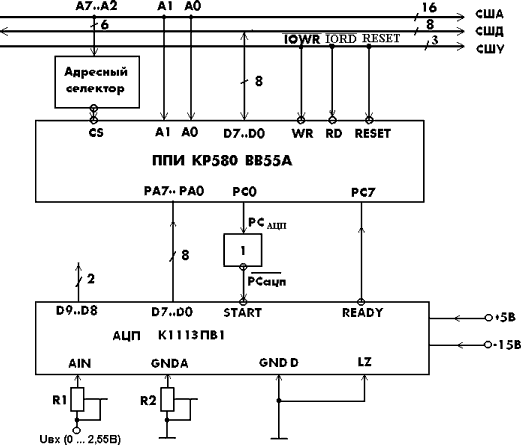

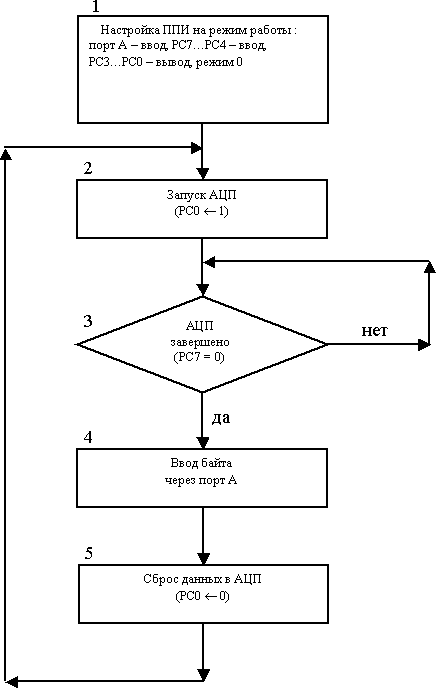

10.2.2.3 Ввод данных от АЦП в МПС через ППИ в режиме 0

10.2.3 Устройство выборки и хранения (УВХ)

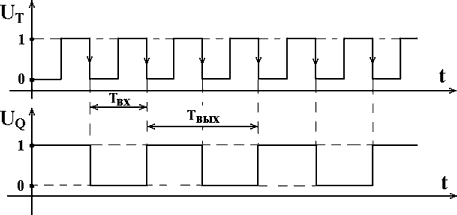

10.2.3.1 Обоснование применения УВХ

10.2.3.2 Принцип действия, схема и основные параметры УВХ

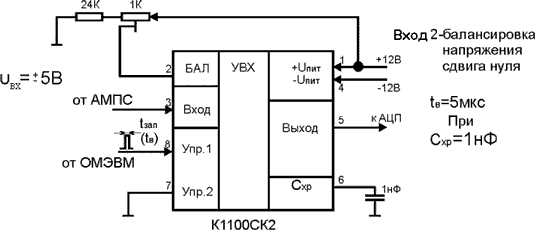

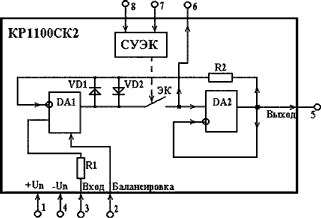

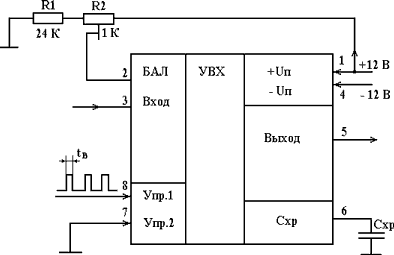

10.2.3.3 Функциональные возможности и схема включения микросхемы УВХ К1100СК2 (КР1100СК2)

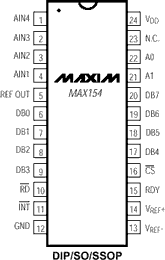

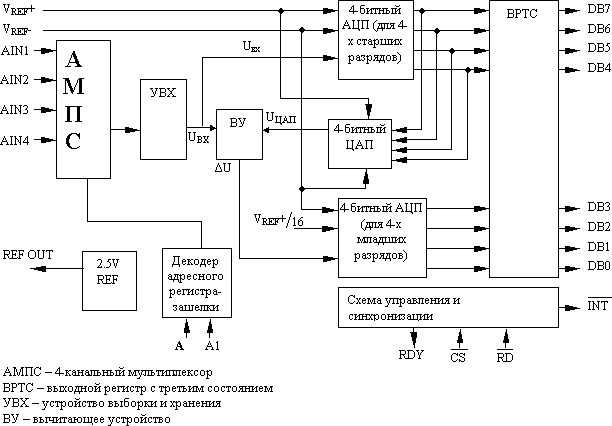

10.2.4 АЦП MAX154

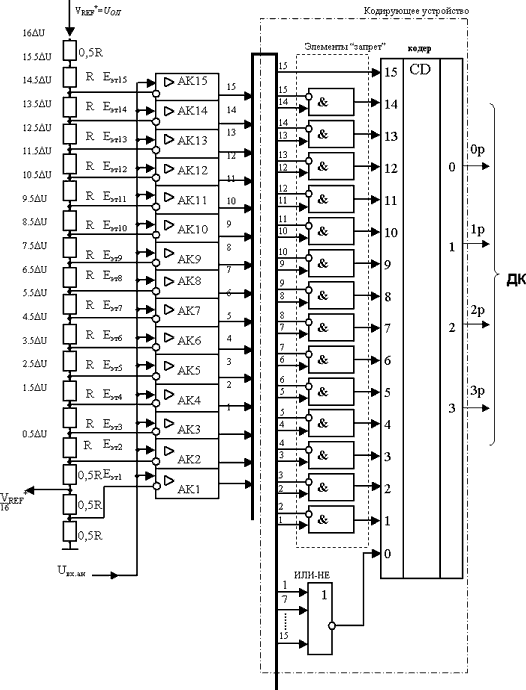

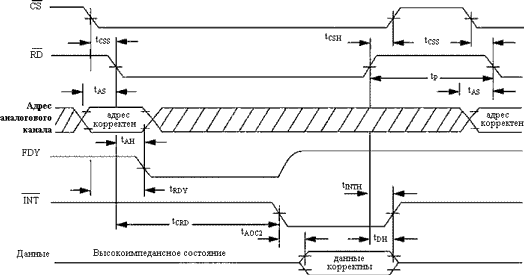

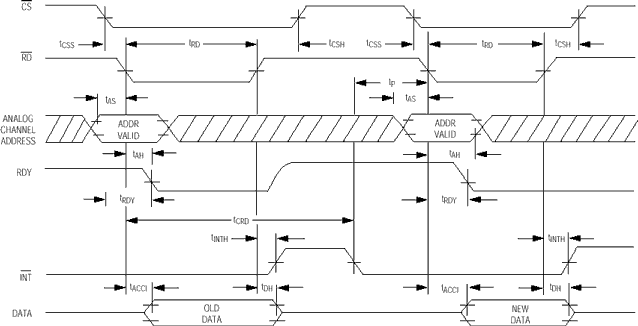

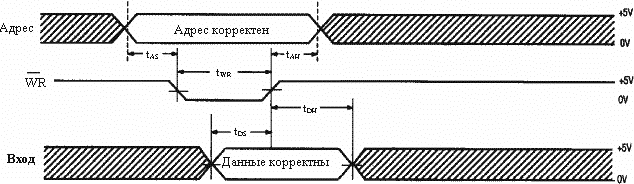

10.2.4.1 Описание микросхемы MAX154. Временные диаграммы и режимы работы

10.2.4.2 Расчет АЦП MAX154

10.3 Применение ЦАП при выводе цифровой информации из МПС

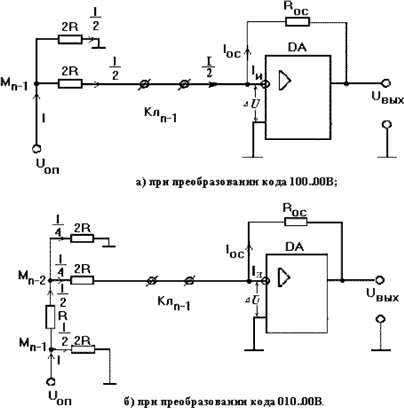

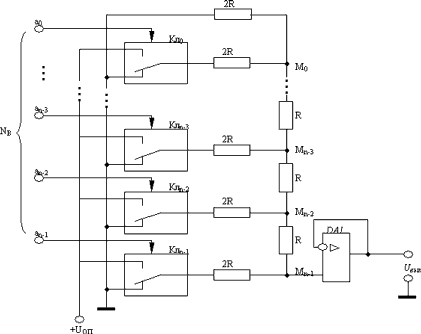

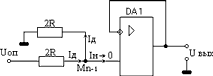

10.3.1 Расчет ЦАП на матрице R-2R c суммированием токов

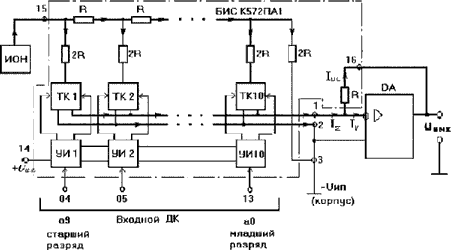

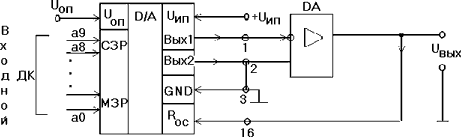

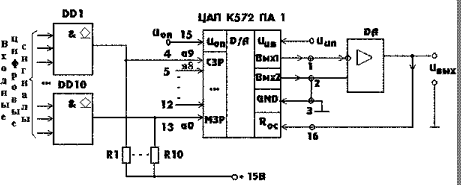

10.3.2 ЦАП К572 ПА1

10.3.2.1 Описание микросхемы К572 ПА1

10.3.2.2 Расчет ЦАП К572 ПА1

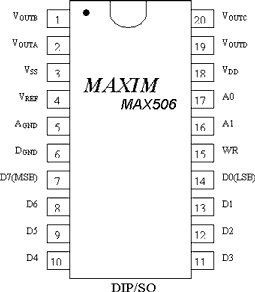

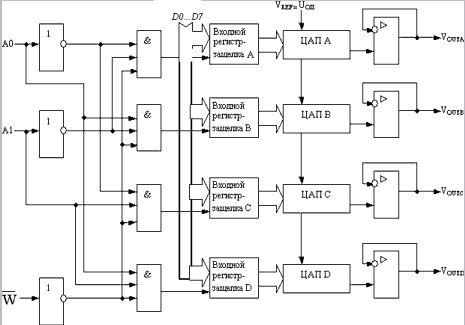

10.3.3 ЦАП MAX506

10.3.3.1 Описание микросхемы MAX506

10.3.3.2 Расчет ЦАП MAX506

10.4 Особенности аппаратной и программной реализации модуля АЦП-ЦАП МПС

10.4.1 Аппаратный уровень

10.4.2 Программный уровень

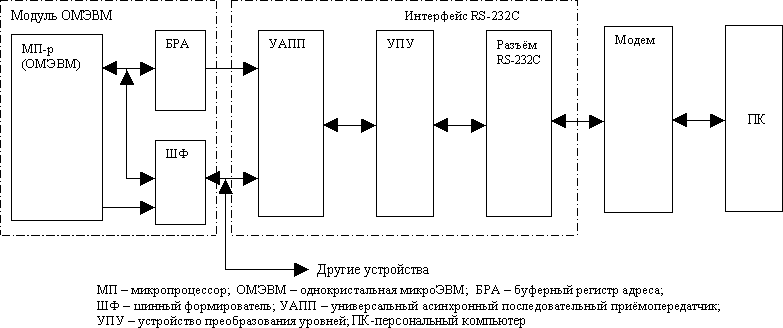

10.5 Обмен между МП-м (ОМЭВМ) и ПК по последовательному каналу связи с помощью интерфейса RS-232С

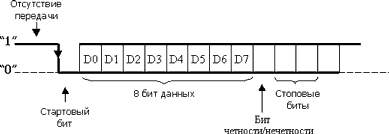

10.5.1 Устройство асинхронное программируемое приёмопередающее (УАПП)

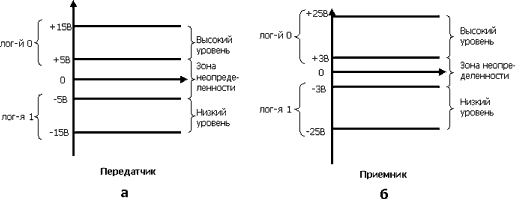

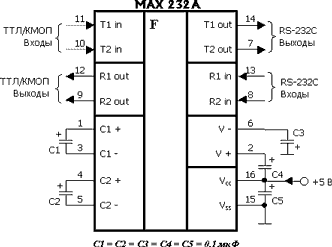

10.5.2 Устройство преобразования уровней (УПУ)

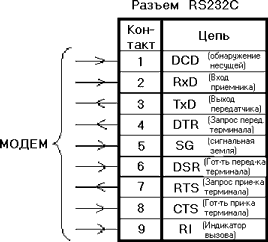

10.5.3 Разъём RS-232С

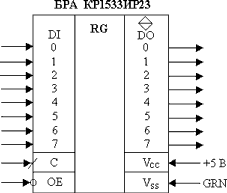

10.5.4 Буферный регистр адреса RS-232C

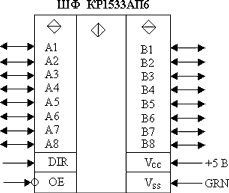

10.5.5 Шинный формирователь

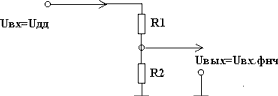

10.6 Выбор и расчет датчиков, нормирующих преобразователей и фильтров нижних частот (ФНЧ)

10.6.1 Выбор и расчет датчиков и нормирующих преобразователей

10.6.1.1 Выбор датчиков

10.6.1.2 Выбор нормирующих преобразователей

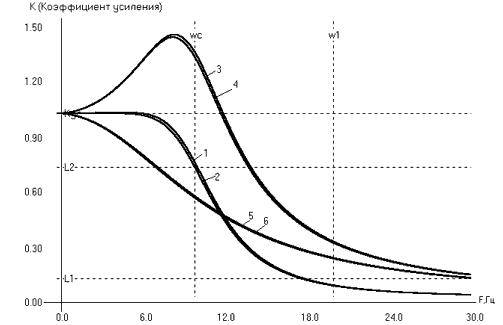

10.6.2 Выбор ФНЧ

10.6.3 Расчет ФНЧ

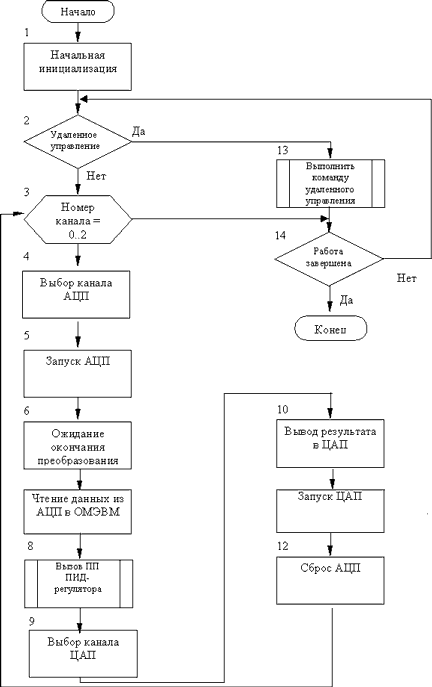

10.7 Разработка схемы алгоритма и управляющей программы

СПИСОК ЛИТЕРАТУРЫ

1. ВВЕДЕНИЕ

Одной из основных задач компьютеризированных систем управления и автоматики (информационно-управляющих систем) является передача, преобразование и обработка информации. Главное звено подобных систем – источник информации, от которого поступают сведения о контролируемом объекте (информация). Последняя передается в виде сообщений, которые представляются последовательностью чисел в той или иной системе счисления. Такой процесс отображения информации называется кодированием, а сообщения, представленные тем или иным кодом, называются дискретными сообщениями.

Поскольку основным элементом современных информационно-управляющих систем является компьютер (микропроцессор, однокристальная микроЭВМ, персональная ЭВМ), то обработка информации ведется в цифровом виде, и дискретные сообщения обычно представляются двоичным кодом (ДК). Код – это правило, в соответствии с которым дискретное сообщение представляется в виде чисел в определенной системе счисления. В цифровой электронике помимо ДК используются десятичные, восьмеричные и шестнадцатеричные коды.

Название кода определяется системой счисления, используемой для представления сообщений. Подробно основные системы счисления, применяемые в цифровой электронике и микропроцессорной технике, рассматриваются в [3, 5, 19].

Ниже остановимся на нескольких основных терминах, которые будут использоваться нами в дальнейшем.

Система счисления (СС) - способ записи чисел при помощи определенных знаков, чаще всего арабских цифр, но иногда и латинских букв, например, шестнадцатеричная система счисления.

Основание СС - определяется числом символов, используемых в системе счисления. Например, двоичная система счисления имеет основание два, десятичная - десять и т. д.

Разрядность чисел. Каждое число характеризуется количеством разрядов. Разряд - это место, которое занимает цифра (буква) в числе. Крайний правый разряд в числе называют нулевым (начальным, младшим или младшим значащим разрядом (МЗР)). Если количество разрядов равно n, то крайний левый разряд называют (n-1)-м (старшим или старшим значащим разрядом (СЗР)).

Вес разряда. Равен основанию СС, возведенном в степень, равную номерам разрядов, которые нумеруются от 0 до (n-1). Например, если рассмотреть 3-х разрядное десятичное число, то веса его разрядов равны:

нулевого - 100 = 1;

первого - 101 = 10;

второго - 102 = 100;

Аналогично веса трехразрядного двоичного числа равны:

нулевого - 20 = 1;

первого - 21=2;

второго - 22=4.

Веса используются для определения десятичного эквивалента чисел. Например, десятичный эквивалент двоичного числа 10110 равен:

124 + 023 + 122 + 121 + 020 = 22

Числа, представленные в двоичной системе счисления (двоичным кодом), должны содержать справа от МЗР латинскую букву В, в десятичной системе - D, шестнадцатеричной - H. Если буква отсутствует, то по умолчанию компьютер (микропроцессор) считает число, представленным в десятичной системе счисления.

Для передачи сообщений используются определенные физические процессы (сигналы), однозначно отображающие передаваемое сообщение с заданной точностью. В цифровой (компьютерной) электронике используются цифровые сигналы, которые принимают один из двух уровней (значений): низкий и высокий. Низкий уровень сигнала называют нулевым (нулем), а высокий - единичным (единицей). Такое представление сигналов имеет место в так называемой “положительной логике”. Иногда используется “отрицательная логика”, в которой низкий уровень сигнала называют единицей, а высокий - нулем.

2. ДИСКРЕТИЗАЦИЯ АНАЛОГОВЫХ СИГНАЛОВ

В информационно-управляющих системах часто возникает задача обработки аналоговых сообщений, снимаемых с аналоговых датчиков. Для ввода такой информации в компьютер, ведущий обработку в цифровом виде, осуществляется дискретизация (квантование) аналоговых сигналов.

Различают 3-и вида дискретизации:

по уровню;

по времени;

по уровню и времени (комбинированная).

Рассмотрим каждый из названных видов квантования более подробно.

2.1 Квантование по уровню

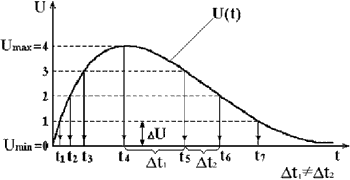

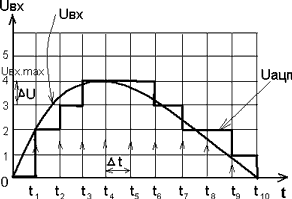

Предположим, что информация отображается аналоговым (непрерывным) напряжением U(t), которое медленно изменяется по закону, представленному на рисунке 2.1.

Мгновенные значения этого напряжения лежат в диапазоне ((Umin=0)…Umax). При выполнении операции квантования по уровню диапазон изменения значений непрерывной величины разбивается на ряд уровней Nу, включая нулевой. Число Nу определяется из выражения

,(2.1)

,(2.1)

где ∆U – величина шага квантования по уровню. Последняя является постоянной величиной (∆U=const) и определяется требуемой погрешностью дискретизации. В нашем примере Nу = 5. Каждый уровень пронумерован в десятичной системе счисления. Работа квантователя сводится к следующему: он определяет моменты времени, когда входной аналоговый сигнал достигает очередного дискретного уровня.

Рисунок 2.1

Эти моменты обозначены t0, t1, t2, t3... Очевидно, что при нелинейном входном сигнале интервал между соседними временными отсчетами является переменной величиной (∆t = var). Примером устройств, в которых осуществляется квантование по уровню, является релейные (пороговые) устройства.

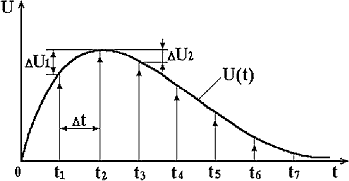

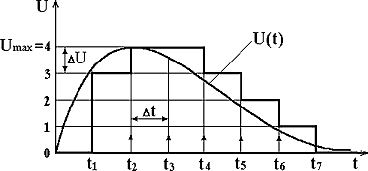

2.2 Квантование по времени

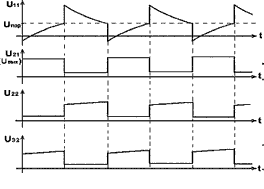

Рисунок 2.2

При выполнении операции квантования по времени (рисунок 2.2) непрерывный входной сигнал заменяется решетчатым (дискретным), снимаемым с выхода квантователя в дискретные моменты времени t1, t2, t3,... Интервал между соседними моментами времени ∆t = t1-t0 = t2-t1= =... = const. Очевидно, что разность соседних значений входного сигнала при нелинейном законе изменения входного напряжения является переменной величиной (∆U=var). Примером устройств, в которых осуществляется квантование по времени, являются импульсные системы автоматического управления [20].

2.3 Квантование по уровню и по времени

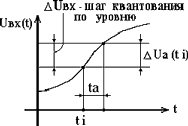

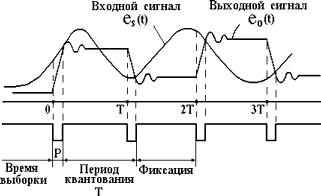

Рисунок 2.3

Работа такого преобразователя (рисунок 2.3) сводится к тому, что из непрерывного сигнала периодически производятся выборки мгновенных значений. Временной интервал между соседними выборками ∆t=const. Каждая выборка округляется преобразователем до ближайшего уровня квантования, полученного от дискретизации по уровню. Интервал между соседними уровнями ∆U=const. Значение уровня представляется в десятичной или двоичной системе счисления (десятичным или двоичным кодом). Код уровня в свою очередь представляется цифровым сигналом. Выходной сигнал имеет ступенчатую форму и с определенной степенью точности соответствует преобразуемому аналоговому напряжению. По такому принципу работают электронные аналогово-цифровые преобразователи (АЦП) [10, 13].

цифровой электронный логический микросхема

2.3.1 Расчет погрешности АЦП

На выходе АЦП каждому дискретному значению соответствует комбинация двоичного кода, число разрядов которого (включая нулевое) обозначим буквой Np. Выбор Np производится в соответствии с соотношением:

.(2.2)

.(2.2)

Число дискретных значений Nд (уровень квантования) зависит от погрешности квантования по уровню.

Абсолютная погрешность, появляющаяся при квантовании по уровню:

,(2.3)

,(2.3)

где ∆U величина шага квантования по уровню, равная

.(2.4)

.(2.4)

Из приведенного соотношения следует, что максимальная абсолютная погрешность равна половине шага квантования по уровню. Относительная погрешность квантования по уровню:

,(2.5)

,(2.5)

где Nд – число дискретных значений выходной величины (уровней квантования). В формуле (2.5) из Nд вычитается единица, т.к. одним из дискретных значений (уровней) является нулевое (рисунок 2.3). Отсюда требуемое число уровней дискретных значений, которое отражает нашу непрерывную функцию с заданной точностью, определяется из выражения:

(2.6)

(2.6)

Пример расчета АЦП

Задано значение относительной погрешности δотн 2%.

Требуется определить разрядность АЦП, удовлетворяющего заданному значению δотн.

Определяем число уровней квантования (число дискретных значений):

Ny

(50/2)+1=26.

(50/2)+1=26.

Выбираем число разрядов АЦП Np ДК=5, что удовлетворяет выражению (2.5):

25=32>26.

2.3.2 Выбор величины шага квантования по времени

Величина шага квантования по времени ∆t, определяющая требуемое быстродействие АЦП, рассчитывается в соответствии с теоремой взятия отсчетов (теоремой Котельникова)

,(2.7)

,(2.7)

где Fmax – частота высшей гармоники частотного спектра входного аналогового сигнала. Иными словами при переходе к дискретной величине для гармонической составляющей входного сигнала, имеющей минимальный период (максимальную частоту), необходимо взять не менее двух отсчетов.

Любой АЦП является инерционным устройством, имеющим конечное время преобразования tпрб, которое должно удовлетворять требуемому значению ∆t.

Если входной аналоговый сигнал меняется достаточно быстро, а АЦП имеет низкое быстродействие, то может появиться апертурная погрешность, выражающаяся в том, что за время преобразования АЦП изменение входного сигнала эквивалентно изменению выходного ДК больше, чем на единицу МЗР. Для борьбы с этим явлением применяют устройства выборки-хранения (УВХ), которые запоминают мгновенное значение входного аналогового сигнала в момент временной выборки и поддерживают это значение постоянным до следующей выборки.

При проектировании компьютеризированных систем часто возникает обратная задача: преобразование цифрового сигнала в аналоговый (непрерывный). Для этого применяют цифро-аналоговые преобразователи (ЦАП).

3. ПРИМЕНЕНИЕ АЛГЕБРЫ ЛОГИКИ (БУЛЕВОЙ АЛГЕБРЫ) ПРИ АНАЛИЗЕ И СИНТЕЗЕ ЦИФРОВЫХ ЭЛЕКТРОННЫХ УСТРОЙСТВ

3.1 Определение и способы задания переключательных функций

В цифровой электронике существуют логические задачи, особенностью которых является то, что их условия и решения могут принимать одно из двух возможных значений. Одно выражает наступление того или иного события, а другое – не наступление его. Наступление события обозначают единицей (логической единицей), а ненаступление - нулем (логическим нулем). Устройства, предназначенные для решения логических задач, называют логическими электронными устройствами (ЛЭУ).

Математическим аппаратом, применяемым при анализе и синтезе ЛЭУ, является алгебра логики, разработанная в середине Х1Х века английским математиком Дж. Булем, и поэтому часто называемая Булевой алгеброй (БА).

БА оперирует с двоичными (логическими) переменными, принимающими одно из двух значений: логический нуль или логическая единица.

Функция двоичных переменных также равная одному из двух значений (нулю или единице) - называется переключательной (логической) функцией (ПФ).

Логические функции обозначаются прописными буквами F или Y, а двоичные переменные - А, В, С, D, E, ... или строчной буквой икс с индексом, например, x1, х2, х3 ... .

ПФ может быть выражена (задана):

словесно;

алгебраическим (булевым) выражением;

таблицей истинности;

диаграммой Вейча (картой Карно).

Примеры задания переключательной функции (ПФ):

1) словесно: функция двух переменных принимает значение логической единицы, если обе переменные также равны единице, в противном случае, она равна нулю;

2) выражением:

3) таблицей истинности (таблица 3.1)

Таблица включает наборы (комбинации) логических переменных, которые должны быть упорядочены по возрастанию или убыванию их десятичных эквивалентов, а также значения функции на каждом наборе. Каждый набор имеет номер, равный десятичному эквиваленту двоичного числа, если наборы упорядочены по возрастанию. Если число переменных равно n, то количество наборов N = 2n. Номера наборов изменяются от 0 до (2n-1). Общее число переключательных функций n – переменных

.(3.1)

.(3.1)

Таблица 3.1

|

№ набора |

В |

А |

F |

|

0 |

0 |

0 |

0 |

|

1 |

0 |

1 |

0 |

|

2 |

1 |

0 |

0 |

|

3 |

1 |

1 |

1 |

Представление переключательной функции диаграммой Вейча (картой Карно) будет рассмотрено позднее при изучении вопроса минимизации ПФ.

3.2 Переключательные функции одной переменной (n=1)

Если n=1,

то число наборов N=21=2,

а количество ПФ

(таблица 3.2)

(таблица 3.2)

Таблица 3.2

|

N набора |

A |

F0 |

F1 |

F2 |

F3 |

|

0 |

0 |

0 |

1 |

0 |

1 |

|

1 |

1 |

0 |

0 |

1 |

1 |

Функция F0

называется константой нуля, так как на

всех наборах принимает нулевое значение

(F0=0).

Функция F3

- константа единицы, так как всегда равна

единице (F3=1).

Функция F2=A

называется повторением, а

–

инверсией (отрицанием – не А).

–

инверсией (отрицанием – не А).

3.3 Переключательные функции двух переменных (n=2)

Если n=2,

то число наборов N=22

=4, а количество ПФ

(таблица 3.3)

(таблица 3.3)

Отметим из этих шестнадцати функций 2-х переменных наиболее часто использующиеся:

F0 – константа нуля;

F15 – константа единицы;

F8=А В=А*В

– конъюнкция (логическое умножение

(логическое “И”));

В=А*В

– конъюнкция (логическое умножение

(логическое “И”));

F14=А В=А+В

– дизъюнкция (логическое сложение

(логическое “ИЛИ”));

В=А+В

– дизъюнкция (логическое сложение

(логическое “ИЛИ”));

F6= – исключающее

ИЛИ (сумма по модулю два, неравнозначность,

неэквивалентность);

– исключающее

ИЛИ (сумма по модулю два, неравнозначность,

неэквивалентность);

– равнозначность

(эквивалентность);

– равнозначность

(эквивалентность);

– ИЛИ-НЕ;

– ИЛИ-НЕ;

– И - НЕ.

– И - НЕ.

Таблица 3.3

|

№ набора |

В |

А |

F0 |

F1 |

F2 |

F3 |

F4 |

F5 |

F6 |

F7 |

F8 |

F9 |

F10 |

F11 |

F12 |

F13 |

F14 |

F15 |

|

0 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

|

1 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

|

2 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

|

3 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

3.4 Базисные логические функции

Любую логическую функцию можно представить совокупностью элементарных логических функций: дизъюнкцией, конъюнкцией, инверсией или их суперпозицией. Набор элементарных функций ИЛИ, И, НЕ называют функционально полным или базисным (базисом). Кроме того существуют еще два базиса: И-НЕ; ИЛИ-НЕ.

3.5 Принцип двойственности булевой алгебры

Если в выражении

F8=А В

конъюнкцию заменить на дизъюнкцию и

проинвертировать обе переменные, то

результат окажется инверсией прежнего

значения функции

В

конъюнкцию заменить на дизъюнкцию и

проинвертировать обе переменные, то

результат окажется инверсией прежнего

значения функции

.

Аналогично, если в выражении F14=А

.

Аналогично, если в выражении F14=А В

дизъюнкцию заменить на конъюнкцию и

проинвертировать обе переменные, то

результат окажется инверсией прежнего

значения функции

В

дизъюнкцию заменить на конъюнкцию и

проинвертировать обе переменные, то

результат окажется инверсией прежнего

значения функции

.

.

Указанные свойства логических функций отражают принцип двойственности булевой алгебры.

3.6 Основные тождества булевой алгебры

А+0=А;А+1=1;

А+А=А;А+ =1;

=1;

А*0=0;А*1=А;

А*А=А;А* =0;

=0; =А.

=А.

3.7 Основные законы и теоремы булевой алгебры

3.7.1 Законы

Переместительный (свойство коммутативности): А+В=В+А; А*В=В*А.

Сочетательный (свойство ассоциативности): (А+В)+С=А+(В+С); (А*В)*С=А*(В*С).

Распределительный (свойство дистрибутивности): А*(В+С)=А*В+А*С; А+В*С=(А+В)*(А+С).

3.7.2 Теоремы

Поглощения: А+А*В=А; А*(А+В)=А.

Склеивания:

Де Моргана. Существует две формы записи теоремы де Моргана:

Форма

1: (3.1.1)

(3.1.1)

Форма

2: (3.1.2)

(3.1.2)

Последние два выражения вытекают из принципа двойственности булевой алгебры (раздел 3.5).

Теорема без названия. Существует еще одна теорема без названия, которую представим следующим образом:

(3.1.3)

(3.1.3)

Два полезных соотношения:

(3.1.4)

(3.1.4)

3.8 Совершенная дизъюнктивная нормальная форма (СДНФ) записи булевых выражений

СДНФ является одной из аналитических форм представления переключательных функций. Булевы выражения простых логических функций можно записать по их словесному описанию. В общем случае для получения аналитической формы (булевого выражения) используют таблицы истинности.

Предположим, логическая функция трех переменных задана таблицей истинности (таблица 3.4).

Таблица 3.4

|

№набора |

С |

В |

А |

F |

|

0 |

0 |

0 |

0 |

0 |

|

1 |

0 |

0 |

1 |

1 |

|

2 |

0 |

1 |

0 |

0 |

|

3 |

0 |

1 |

1 |

0 |

|

4 |

1 |

0 |

0 |

1 |

|

5 |

1 |

0 |

1 |

1 |

|

6 |

1 |

1 |

0 |

1 |

|

7 |

1 |

1 |

1 |

0 |

Эта функция

имеет четыре конституенты единицы К1,

К4, К5 и К6

(коституента единицы – это единичное

значение ПФ на одном конкретном наборе.

Всего для ПФ трех переменных может быть

восемь конституент единицы, если функция

принимает единичное значение на всех

наборах). Конституента единицы записывается

в виде конъюнкции. Для нашего примера

;

;

.

.

Булево выражение ПФ в СДНФ представляет сумму конституент единицы:

.(3.2)

.(3.2)

Поскольку конституенты единицы записываются в виде конъюнкций, то СДНФ представляет сумму конъюнкций, каждая из которых содержит все переменные в прямом или инверсном виде не более одного раза. Очевидно, что логическая функция имеет единственное булево выражение в СДНФ, что следует из методики его получения.

СДНФ называется дизъюнктивной (состоит из суммы конъюнкций), совершенной (все конъюнкции содержат по одному разу каждую переменную в прямом или инверсном виде) и нормальной (двухуровневой) – для ее реализации требуются логические элементы двух видов: конъюнкторы и дизъюнкторы, при этом предполагается, что исходные переменные поступают в прямом и инверсном виде.

3.9 Дизъюнктивная нормальная форма (ДНФ)

Если в выражении (3.2) во всех или некоторых конъюнкциях отсутствуют отдельные переменные (в прямой или инверсной форме) или ряд конъюнкций, отображающих конституенты единицы, отсутствуют вообще, то такая форма представления булевого выражения называется дизъюнктивной нормальной формой (ДНФ).

Переключательная функция может описываться несколькими булевыми выражениями в ДНФ, одно из которых является минимальным (содержит минимум конъюнкций и минимум входящих в них переменных).

3.10 Совершенная конъюнктивная нормальная форма (СКНФ) записи булевых выражений

Описанная таблицей 3.4 переключательная функция помимо конституент единицы содержит конституенты нуля К0, К2, К3 и К7 (конституента нуля – это нулевое значение ПФ на одном конкретном наборе). Всего для ПФ 3-х переменных может быть восемь конституент нуля, если функция принимает нулевое значение на всех наборах. Конституента нуля записывается в виде дизъюнкции. Для нашего примера (таблица 3.4) это

Булево выражение в СКНФ представляет собой произведение конституент нуля:

.(3.3)

.(3.3)

СКНФ называется конъюнктивной (состоит из произведения дизъюнкций), совершенной (все дизъюнкции включают по одному разу каждую переменную в прямом или инверсном виде) и нормальной (двухуровневой) – для ее реализации требуются логические элементы двух видов: конъюнкторы и дизъюнкторы, при этом предполагается, что исходные переменные поступают в прямом или инверсном виде.

Логическая функция имеет единственное булево выражение в СКНФ.

3.11 Конъюнктивная нормальная форма (КНФ)

Если в выражении (3.3) все дизъюнкции или отдельные из них не содержат всех переменных в прямом или инверсном виде, а также некоторые дизъюнкции вообще отсутствуют, то такая форма представления булевого выражения называется конъюнктивной нормальной формой (КНФ).

Переключательная функция может описываться несколькими булевыми выражениями в КНФ, одно из которых является минимальным (содержит минимум дизъюнкций и минимум входящих в них переменных).

3.12 Минимизация логических функций

Минимизацией называют процедуру упрощения аналитического выражения, представляющего переключательную (логическую) функцию, направленную на то, чтобы булево выражение ПФ содержало минимальное количество членов с минимальным числом переменных.

Способы минимизации:

– алгебраический;

– с помощью диаграмм Вейча (карт Карно).

3.12.1 Алгебраический способ минимизации ПФ

В некоторых простых случаях можно осуществить минимизацию булевого выражения ПФ, используя тождества и теоремы булевой алгебры.

Пример 1. Исходное булево выражение:

.(3.4)

.(3.4)

Применяя теорему склеивания, получим булево выражение

,(3.5)

,(3.5)

которое равносильно (эквивалентно) исходному, но значительно проще его.

Пример 2. Исходное булево выражение:

.(3.6)

.(3.6)

Используя тождество А=А+А и теорему склеивания получим более простое выражение

.(3.7)

.(3.7)

Такие элементарные приемы минимизации удается использовать, если исходное булево выражение содержит малое количество членов с небольшим числом переменных.

Более наглядным и удобным является минимизация с применением диаграмм Вейча (карт Карно).

3.12.2 Минимизация ПФ с использованием диаграмм Вейча (карт Карно)

Диаграммы Вейча (карты Карно) [3, 11, 18] построены так, что их соседние клетки содержат члены исходной ПФ, отличающиеся значением одной переменной: один член содержит эту переменную в прямой форме, а другой – в инверсной. Благодаря этому возникает наглядное представление о различных вариантах склеивания смежных членов.

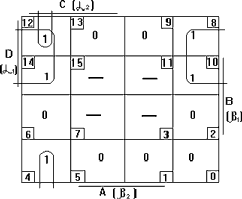

3.12.2.1 Минимизация ПФ с помощью диаграмм Вейча

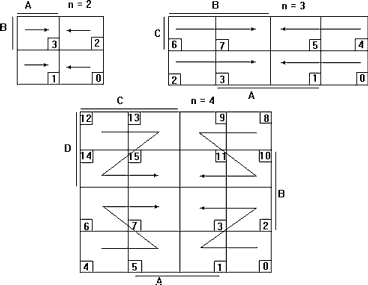

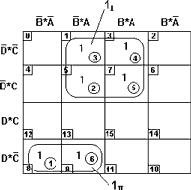

Исходным продуктом для применения диаграмм Вейча является представление ПФ таблицей истинности, в которой возможные наборы переменных упорядочены по возрастанию или по убыванию их десятичных эквивалентов (таблица 3.1). Вид диаграмм Вейча зависит от числа переменных минимизируемой ПФ - n и от того, как упорядочены наборы переменных в таблице. Если наборы упорядочены по возрастанию их десятичных эквивалентов, то диаграммы Вейча для n=2,3,4 имеют вид, приведенный на рисунке 3.1.

Рисунок 3.1

Число клеток диаграммы равно количеству наборов переменных

Nкл=Nнаб=2n.(3.8)

Если n=2, то Nкл=22=4; n=3 – Nкл=8, n=4 – Nкл=16.

Каждая клетка соответствует определенному набору переменных и имеет номер, одинаковый с номером набора.

Строки и столбцы диаграммы, помеченные чертой, определяют наборы, в которых переменные принимают единичные значения (входят в прямой форме). Строки и столбцы, не помеченные чертой, соответствуют наборам, в которых те же переменные принимают нулевые значения (входят в инверсной форме). Например, для n=3 (рисунок 3.1) двум левым столбцам соответствует единичное значение переменной В (в входит в прямой форме), а двум правым – нулевое значение (в входит в инверсной форме).

В клетки записываются значения ПФ на соответствующем наборе (нулевое или единичное). Если на каком-то наборе функция не определена, то в клетке диаграммы ставится прочерк.

ПФ считается неопределенной, если:

1) данный набор переменных в реальном логическом устройстве невозможен;

2) значение функции на данном наборе безразлично.

После заполнения диаграммы можно приступить непосредственно к минимизации, которую производят по единицам или нулям.

В первом случае результатом минимизации будет булево выражение в ДНФ, а во втором – в КНФ.

3.12.2.1.1 Общие правила минимизации

Минимизацию можно проводить по единицам (нулям). При этом:

1) Смежные единицы (нули) диаграммы условно охватывают (накрывают) прямоугольными контурами. Каждый контур может содержать 2,4,8,16, ... единиц (нулей).

2) Одним контуром (накрытием) необходимо объединить максимальное количество смежных клеток, содержащих единицы (нули).

3) Необходимо, чтобы каждая единица (нуль) накрывалась хотя бы один раз.

4) Одна и та же единица (нуль) может охватываться несколько раз разными контурами.

5) Верхняя и нижняя строки диаграммы считаются смежными - их можно представить таковыми, если мысленно свернуть диаграмму в горизонтальный цилиндр.

6) Левый и правый столбцы также считаются смежными - диаграмму можно мысленно свернуть в вертикальный цилиндр.

7) Угловые клетки также считаются смежными - диаграмму можно мысленно свернуть в тор.

8) Перед выполнением минимизации в клетки, содержащие прочерки (на данных наборах ПФ неопределена), можно записать дополнительные единицы (нули), что способствует получению более простого конечного булевого выражения. При этом следует помнить, что хотя бы один раз необходимо накрыть лишь основные единицы (нули). Дополнительные единицы (нули) могут увеличивать суммарное число единиц (нулей), входящих в накрытие, а, следовательно, уменьшать число переменных в результирующих конъюнкциях (дизъюнкциях).

9) Результатом минимизации является булево выражение в ДНФ (КНФ). Количество конъюнкций в ДНФ (дизъюнкций в КНФ) соответствует числу контуров (накрытий).

10) В каждую конъюнкцию (дизъюнкцию) войдут только те переменные, значение которых в пределах контура не меняется (переменная принимает в накрытии только единичное или нулевое значение (входит только в прямой или инверсной форме)).

При минимизации по единицам в результирующие конъюнкции переменные входят в прямой форме, если соответствующие им строки и столбцы диаграммы помечены чертой. Переменные, связанные со строками и столбцами, не помеченными чертой, входят в конъюнкции в инверсной форме.

При минимизации по нулям в результирующие дизъюнкции переменные входят в прямой форме, если соответствующие им строки и столбцы не помечены чертой, в противном случае дизъюнкции содержат переменные в инверсном виде.

Целью минимизации является получение минимальной ДНФ или КНФ, содержащей минимум членов с минимальным количеством входящих в них переменных. Для этого необходимо минимальным числом контуров охватить хотя бы один раз каждую единицу (нуль). При этом необходимо стремиться, чтобы в каждое накрытие входило как можно больше смежных единиц (нулей).

На рисунке 3.1 показаны диаграммы Вейча при числе логических переменных n=2,3,4. Для n>4 диаграммы содержатся в [18]. Если наборы переменных исходной таблицы истинности упорядочены по убыванию их десятичных эквивалентов, то следует воспользоваться диаграммами Вейча, приведенными в [5, 6]

3.12.2.1.2 Примеры минимизации ПФ с помощью диаграмм Вейча

Пример 1. Для контроля за возможной деформацией металлической конструкции из-за перегрева в ее различных критических точках установлены четыре термодатчика, обозначенные ТД1, ТД2, ТД3, ТД4. Экспериментальные исследования конструкции показали, что в процессе ее эксплуатации возможны шесть сочетаний сработавших и не сработавших датчиков. При этом деформация конструкции возникала в следующих случаях:

1) сработали ТД4, ТД3 и не сработали ТД2 и ТД1;

2) сработали ТД4, ТД3, ТД2 и ТД1;

3) сработали ТД2 и не сработали ТД4, ТД3 и ТД1;

4) сработали ТД3, ТД2 и ТД1 и не сработал ТД4;

В случаях, когда:

5) сработали ТД4, ТД3, ТД2 и не сработал ТД1;

6) сработали ТД2, ТД1 и не сработали ТД4, ТД3

деформация конструкции не возникала.

Таблица 3.5

|

№ |

Состояние датчиков |

Деформация конструкции |

|

|

Сработали |

Не сработали |

||

|

1 |

ТД4, ТД3 |

ТД2, ТД1 |

Возникала |

|

2 |

ТД4 ... ТД1 |

― |

|

|

3 |

ТД2 |

ТД4, ТД3, ТД1 |

|

|

4 |

ТД3, ТД2, ТД1 |

ТД4 |

|

|

5 |

ТД4, ТД3, ТД2 |

ТД1 |

Не возникала |

|

6 |

ТД2, ТД1 |

ТД4, ТД3 |

По условию эксплуатации конструкции другие сочетания сработавших и не сработавших датчиков невозможны.

Необходимо спроектировать цифровое логическое устройство, включающее сигнал тревоги, если происходит срабатывание термодатчиков в опасном сочетании.

Обозначим цифровые сигналы на выходе термодатчиков логическими переменными: ТД4→D; ТД3→С; ТД2→В; ТД1→А, а логическую функцию, которую должно реализовать устройство контроля – F.

Составим таблицу истинности, отражающую требуемую логическую функцию (таблица 3.6).

Таблица 3.6

|

(ТД4) |

(ТД3) |

(ТД2) |

(ТД1) |

|||

|

№ набора |

D |

C |

B |

A |

F |

|

|

0 |

0 |

0 |

0 |

0 |

- |

|

|

1 |

0 |

0 |

0 |

1 |

- |

|

|

2 |

0 |

0 |

1 |

0 |

1 |

3) |

|

3 |

0 |

0 |

1 |

1 |

0 |

6) |

|

4 |

0 |

1 |

0 |

0 |

- |

|

|

5 |

0 |

1 |

0 |

1 |

- |

|

|

6 |

0 |

1 |

1 |

0 |

- |

|

|

7 |

0 |

1 |

1 |

1 |

1 |

4) |

|

8 |

1 |

0 |

0 |

0 |

- |

|

|

9 |

1 |

0 |

0 |

1 |

- |

|

|

10 |

1 |

0 |

1 |

0 |

- |

|

|

11 |

1 |

0 |

1 |

1 |

- |

|

|

12 |

1 |

1 |

0 |

0 |

1 |

1) |

|

13 |

1 |

1 |

0 |

1 |

- |

|

|

14 |

1 |

1 |

1 |

0 |

0 |

5) |

|

15 |

1 |

1 |

1 |

1 |

1 |

2) |

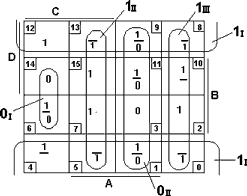

Диаграмма Вейча, отражающая данную таблицу, показана на рисунке 3.2.

Рисунок 3.2

Если будем производить минимизацию по единицам, то в клетки, содержащие прочерки проставим дополнительные единицы.

Основные единицы накрываем тремя контурами: 1-й контур (1I) образуют клетки первой и последней строки, 2-й (1II) - клетки 2-го столбца и 3-й (1III) - 4-го столбца.

Итоговое булево выражение минимизированной ПФ имеет вид

.(3.9)

.(3.9)

Это выражение должно быть реализовано цифровым логическим устройством, включающим сигнал тревоги.

Рассматриваемую функцию можно минимизировать и по нулевым значениям (нулям). Для этого доопределяем клетки с номерами 1,6,9 и 11 нулями и накрываем два основных нуля двумя прямоугольниками, включающими два и четыре элемента (нуля). Первый прямоугольник (0I) охватывает клетки с номерами 6,14, второй (0II) – 1,3,11 и 9.

Итоговое булево выражение минимизированной ПФ имеет вид

.(3.10)

.(3.10)

Оба выражения (3.9) и (3.10) эквивалентны, и применять следует то из них, которое проще реализуется на конкретном наборе логических элементов (базисе). Этот вопрос будет рассмотрен в следующих лекциях.

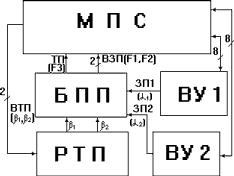

Пример 2. Необходимо разработать блок приоритетных прерываний от 2-х внешних устройств: ВУ1 и ВУ2. ВУ с меньшим номером соответствует более высокий приоритет. Упрощенная структура проектируемой системы показана на рисунке 3.3.

Рисунок 3.3

На схеме приняты следующие сокращения: МПС – микропроцессорная система; ВУ – внешнее устройство; БПП – блок приоритетных прерываний; ВТП – вектор текущего прерывания, который с помощью логических переменных β1, β2 описывает возможные состояния МП-системы при обслуживании запросов прерываний от ВУ (таблица 3.7); РТП – регистр текущего прерывания (запоминает значения переменных β1, β2); ЗП1, ЗП2 – запросы прерываний от ВУ1, ВУ2 (описываются переменными α1, α2); ТП – требование прерывания (логическая функция F3); ВЗП – вектор запроса прерывания (отображается комбинацией значений логических функций F1 и F2 (таблица 3.8)).

Таблица 3.7

|

№ набора |

β1 |

β2 |

ВТП |

|

0 |

0 |

0 |

ожидание |

|

1 |

0 |

1 |

обслуживается ВУ1 |

|

2 |

1 |

0 |

обслуживается ВУ2 |

|

3 |

1 |

1 |

– |

Таблица 3.8

|

ВЗП |

F1 |

F2 |

|

F3 =0 или неопределено |

– |

– |

|

Запрос от ВУ2 |

1 |

0 |

|

Запрос от ВУ1 |

0 |

1 |

МП-система периодически проверяет значение сигнала ТП (функция F3). Если ТП=0 (запрос на прерывание отсутствует), то значения функций F1, F2 безразличны и МПС продолжает свою работу. Если ТП=1, то МП-система анализирует значение вектора ВЗП (комбинацию функций F1, F2) и определяет номер запроса прерывания. Так как набор переменных β1=β2=1 невозможен (таблица 3.6), то функции F1, F2, F3 в таких случаях неопределены. Таким образом, задача БПП является реализация трех логических функций F1, F2, F3, каждая из которых определяется значениями четырех логических переменных: α1, α2, β1и β2.

Составим таблицу истинности (таблица 3.9) для названных функций.

Таблица 3.9

|

D |

C |

B |

A |

||||

|

№ набора |

α1 |

α2 |

β1 |

β2 |

F3 |

F1 |

F2 |

|

0 |

0 |

0 |

0 |

0 |

0 |

- |

- |

|

1 |

0 |

0 |

0 |

1 |

0 |

- |

- |

|

2 |

0 |

0 |

1 |

0 |

0 |

- |

- |

|

3 |

0 |

0 |

1 |

1 |

- |

- |

- |

|

4 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

|

5 |

0 |

1 |

0 |

1 |

0 |

- |

- |

|

6 |

0 |

1 |

1 |

0 |

0 |

- |

- |

|

7 |

0 |

1 |

1 |

1 |

- |

- |

- |

|

8 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

|

9 |

1 |

0 |

0 |

1 |

0 |

- |

- |

|

10 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

|

11 |

1 |

0 |

1 |

1 |

- |

- |

- |

|

12 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

|

13 |

1 |

1 |

0 |

1 |

0 |

- |

- |

|

14 |

1 |

1 |

1 |

0 |

1 |

0 |

1 |

|

15 |

1 |

1 |

1 |

1 |

- |

- |

- |

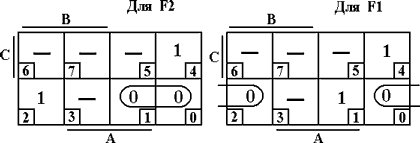

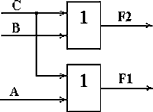

Представляем функции F1, F2, F3 диаграммами Вейча (рисунок 3.4)

Для F3 Для F1

Для F2

Рисунок 3.4

Булевы выражения минимизированных ПФ имеют вид:

F3= .(3.11)

.(3.11)

F1= .(3.12)

.(3.12)

F2= .(3.13)

.(3.13)

Полученные выражения (3.11-3.13) имеют вполне конкретное логическое толкование и при наличии определенных навыков могли быть получены без составления таблицы истинности и минимизации ПФ.

Так, если F3=1, а в противном случае F1 и F2 безразличны, то запрос от ВУ1 в виде комбинации F1=0, F2=1 поступит лишь тогда, когда α1=1. Значение α2 безразлично, так как даже при α1=α2=1 все равно α1 имеет более высокий приоритет. Если α1=0, а F3=1, то это значит, что требование прерывания вызвано запросом от ВУ2 (α2=1). При записи выражения (3.11) можно было руководствоваться следующими соображениями. F3=1 в двух случаях. Во-первых, если поступил запрос от ВУ1 (α1=1) и при этом МП-система ожидает запроса либо обслуживает прерывание от ВУ2 (в обоих случаях β2=0, см. таблицу 3.8). Во вторых, если поступил запрос от ВУ2 (α2=1) и при этом МП-сиcтема находится в состоянии ожидания (β1=β2=0). Сказанное соответствует двум составляющим выражения (3.11).

На втором примере мы прошли 2 этапа синтеза комбинационных цифровых электронных устройств:

1. Представление переключательных функций в форме, которая является исходной для выбранного метода минимизации - в нашем случае в виде таблицы истинности и диаграммы Вейча.

2. Получение минимальной ДНФ для каждого выхода комбинационной схемы.

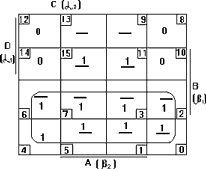

3.12.2.2 Минимизация ПФ с помощью карт Карно

На рисунке 3.5 показан пример карты Карно для ПФ четырех переменных (n=4).

Рисунок 3.5

Каждая клетка в картах Карно так же, как и в диаграммах Вейча соответствует определенному набору переменных. Соседние клетки соответствуют наборам, отличающимся значением одной из переменных. Каждая строка и столбец обозначаются значением конкретной переменной или комбинацией (произведением) переменных в прямой или инверсной форме.

Клетки, помеченные переменными в прямой форме, соответствуют наборам, где эти переменные принимают единичные значения, а клетки, обозначенные переменными в инверсной форме – наборам, где эти переменные равны нулям.

Карты Карно удобно использовать, если ПФ задана в виде булевого выражения в СДНФ.

Например,

(3.14)

(3.14)

Правила минимизации с помощью карт Карно в основном аналогичны правилам, изложенным при рассмотрении диаграмм Вейча. Отличие состоит в заполнении карты Карно единицами. Если диаграмма Вейча заполняется единицами в соответствии с номерами наборов, на которых исходная ПФ принимает единичное значение, то в карте Карно единицы ставят в клетки, лежащие на пересечении строк и столбцов карты, помеченных комбинациями переменных, которые при их перемножении дают запись соответствующей конституенты единицы (конъюнкции) в булевом выражении минимизируемой функции (3.14). На рисунке 3.5 показан пример заполнения карты Карно по выражению (3.14), содержащему шесть конституент единиц.

Булево выражение минимизированной ПФ имеет вид

.(3.15)

.(3.15)

Другие примеры использования диаграмм Вейча и карт Карно показаны в [3, 18].

4. ЛОГИЧЕСКИЕ ЭЛЕМЕНТЫ

Для аппаратной реализации булевых выражений используется некоторый набор логических элементов, выпускаемых в виде интегральных микросхем (ИМС). Существуют специализированные ИМС, разработанные методами интегральной технологии специально для получения требуемой логической зависимости. Специализированные ИМС не требуют никаких паяных межсоединений и обладают высокой надежностью. Однако разработка подобных микросхем экономически оправдана лишь при большом объеме выпуска. Примером может служить массовый выпуск специализированных БИС для электронных часов, микрокалькуляторов и т.д.

Помимо специализированных ИМС имеется универсальный набор логических элементов в виде ИМС, обеспечивающий реализацию любых логических функций. К этому набору можно отнести: инвертор; конъюнктор; дизъюнктор; повторитель; И-НЕ; ИЛИ-НЕ; исключающее ИЛИ; сложение по модулю два (нечетность); сложение по модулю два с отрицанием (четность); эквивалентность; неэквивалентность; И-ИЛИ-НЕ; запрет и др.

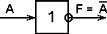

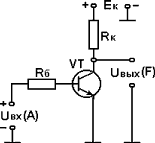

4.1 Инвертор (логический элемент НЕ)

Инвертор реализует логическую функцию

.(4.1)

.(4.1)

Ниже показаны его обозначение на электрических схемах (рисунок 4.1,а) и принципиальная схема (рисунок 4.1,б).

А Б

Рис. 4.1

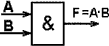

4.2 Конъюнктор (логический элемент И)

Конъюнктор реализует логическую функцию

.(4.2)

.(4.2)

Ниже показаны его обозначение на электрических схемах (рисунок 4.2,а), принципиальная схема (рисунок 4.2,б) и таблица истинности (таблица 4.1).

А Б

Рисунок 4.2

Таблица 4.1

|

№ набора |

B |

A |

F |

|

0 |

0 |

0 |

0 |

|

1 |

0 |

1 |

0 |

|

2 |

1 |

0 |

0 |

|

3 |

1 |

1 |

1 |

Термин “логический” обычно применяют по отношению к процедуре принятия решения. В таком случае можно сказать, что логический элемент – это такая схема, которая “основываясь” на входных сигналах, “может решать”, что ей ответить на выходе - “да” или “нет”. Схема конъюнктора на рисунке 4.2,б отвечает “да” (на выходе появляется высокий уровень напряжения) только в том случае, когда на оба её входа поданы сигналы “да” (оба входных напряжения имеют высокий уровень).

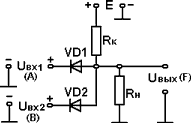

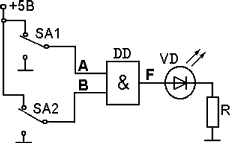

Рисунок 4.3

На рисунке 4.3 показана схема исследования логического элемента И в лабораторных условиях.

Входы логического элемента подключены к ключам SA1 и SA2. Индикатором выхода служит светодиод. Если на входах А и В возникают сигналы НИЗКОГО логического уровня (земля), то светодиод не излучает. Эту ситуацию отражает первая строка таблицы 4.2.

Таблица 4.2

|

Входы |

Выход |

|||||

|

B |

A |

F |

||||

|

Уровень напряжения |

Двоичный Сигнал |

Уровень напряжения |

Двоичный сигнал |

Излучение |

Двоичный сигнал |

|

|

Строка 1 |

Низкий |

0 |

Низкий |

0 |

Нет |

0 |

|

Строка 2 |

Низкий |

0 |

Высокий |

1 |

Нет |

0 |

|

Строка 3 |

Низкий |

1 |

Низкий |

0 |

Нет |

0 |

|

Строка 4 |

Высокий |

1 |

Высокий |

1 |

Есть |

1 |

Помимо значений уровней напряжений и отметки наличия излучения входные и выходные сигналы в таблице 4.2 обозначены двоичными цифрами: 0 и 1. Согласно строке 1, если на оба входа поданы двоичные нули, то на выходе логического элемента также возникает двоичный нуль. Двоичная единица на выходе элемента И появляется только в том случае, когда на оба входа А и В поданы двоичные единицы.

Двоичной единице, или напряжению ВЫСОКОГО уровня, в точках А, В или F соответствует потенциал +5В относительно земли. Двоичный нуль, или напряжение НИЗКОГО уровня, в точках А, В или F соответствует потенциалу земли (точнее, близко к потенциалу земли, т.е. к нулю). Мы применяем здесь так называемую “положительную логику”, поскольку для получения двоичной единицы используется положительное напряжение +5В. При работе с цифровыми электронными устройствами мы чаще всего будем иметь дело с “положительной логикой”.

4.3 Дизъюнктор (логический элемент ИЛИ)

Дизъюнктор реализует логическую функцию

.(4.3)

.(4.3)

Ниже показаны его обозначение на электрических схемах (рисунок 4.4,а), принципиальная схема (рисунок 4.4, б) и таблица истинности (таблица 4.3).

А Б

Рисунок 4.4

Таблица 4.3

|

№ набора |

B |

A |

F |

|

0 |

0 |

0 |

0 |

|

1 |

0 |

1 |

1 |

|

2 |

1 |

0 |

1 |

|

3 |

1 |

1 |

1 |

Отличительное свойство логического элемента ИЛИ состоит в том, что на его выходе появляется сигнал низкого уровня только тогда, когда на все его входы подаются также сигналы низкого логического уровня.

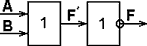

4.4 Повторитель

Реализует логическую функцию

.(4.4)

.(4.4)

Его обозначение на электрических схемах показано на рисунке 4.5

Рисунок 4.5

Повторитель не выполняет никаких логических преобразований и используется для повышения нагрузочной способности отдельных выходов ИМС или как элемент задержки, равной времени распространения сигнала через него.

4.5 И–НЕ

Элемент И - НЕ реализует логическую функцию

.(4.5)

.(4.5)

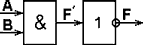

Ниже показаны его обозначение на электрических схемах (рисунок 4.6,а), функциональная схема (рисунок 4.6, б) и таблица истинности (таблица 4.4).

Таблица 4.4

|

№ набора |

B |

A |

F |

|

0 |

0 |

0 |

1 |

|

1 |

0 |

1 |

1 |

|

2 |

1 |

0 |

1 |

|

3 |

1 |

1 |

0 |

А Б

Рисунок 4.6

4.6 ИЛИ–НЕ

Элемент ИЛИ- НЕ реализует логическую функцию

.(4.6)

.(4.6)

Ниже показаны его обозначение на электрических схемах (рисунок 4.7,а), функциональная схема (рисунок 4.7, б) и таблица истинности (таблица 4.5).

Таблица 4.5

|

№ набора |

B |

A |

F |

|

0 |

0 |

0 |

1 |

|

1 |

0 |

1 |

0 |

|

2 |

1 |

0 |

0 |

|

3 |

1 |

1 |

0 |

Рисунок 4.7

4.7 Исключающее ИЛИ

Реализует логическую функцию

.(4.7)

.(4.7)

Ниже показаны его обозначение на электрических схемах (рисунок 4.8) и таблица истинности (таблица 4.6).

Рисунок 4.8

Таблица 4.6

|

№ набора |

B |

A |

F |

|

0 |

0 |

0 |

0 |

|

1 |

0 |

1 |

1 |

|

2 |

1 |

0 |

1 |

|

3 |

1 |

1 |

0 |

Элемент называется исключающее ИЛИ, т.к. его таблица истинности совпадает с таблицей истинности элемента ИЛИ первыми тремя строчками. В четвертой строке элемента ИЛИ, F=1 , а элемента исключающее ИЛИ – нуль.

Ниже приведена таблица истинности ПФ “исключающее ИЛИ” для 3-х логических переменных (таблица 4.6.1).

Таблица 4.6.1

|

№ набора |

С |

В |

А |

F |

|

0 |

0 |

0 |

0 |

0 |

|

1 |

0 |

0 |

1 |

1 |

|

2 |

0 |

1 |

0 |

1 |

|

3 |

0 |

1 |

1 |

1 |

|

4 |

1 |

0 |

0 |

1 |

|

5 |

1 |

0 |

1 |

1 |

|

6 |

1 |

1 |

0 |

1 |

|

7 |

1 |

1 |

1 |

0 |

4.8 Сложение по модулю два (нечетность)

Элемент реализует логическую функцию

.(4.8)

.(4.8)

Ниже показаны его обозначение на электрических схемах (рисунок 4.9) и таблица истинности (таблица 4.7).

Таблица 4.7

|

№ набора |

С |

В |

А |

F |

|

0 |

0 |

0 |

0 |

0 |

|

1 |

0 |

0 |

1 |

1 |

|

2 |

0 |

1 |

0 |

1 |

|

3 |

0 |

1 |

1 |

0 |

|

4 |

1 |

0 |

0 |

1 |

|

5 |

1 |

0 |

1 |

0 |

|

6 |

1 |

1 |

0 |

0 |

|

7 |

1 |

1 |

1 |

1 |

Рисунок 4.9

Элемент суммирует значения переменных по модулю два (символ (псевдоплюс) означает mod2: 0 + 0 = 0; 1 + 1 = 0; 1 + 0 = 1; 0 + 1 = 1).

Если при суммировании число единиц нечетно, то функция равна 1, в противном случае – F=0.

4.9 Сложение по модулю два с отрицанием (четность)

Элемент реализует логическую функцию

.(4.9)

.(4.9)

Ниже показаны его обозначение на электрических схемах (рисунок 4.10) и таблица истинности (таблица 4.8).

Рисунок 4.10

Элемент формирует сумму по модулю два, которая затем инвертируется на выходе. Если при суммировании число единиц четно, то функция равна 1, в противном случае – F = 0.

Таблица 4.8

|

№ набора |

С |

В |

А |

F |

|

0 |

0 |

0 |

0 |

1 |

|

1 |

0 |

0 |

1 |

0 |

|

2 |

0 |

1 |

0 |

0 |

|

3 |

0 |

1 |

1 |

1 |

|

4 |

1 |

0 |

0 |

0 |

|

5 |

1 |

0 |

1 |

1 |

|

6 |

1 |

1 |

0 |

1 |

|

7 |

1 |

1 |

1 |

0 |

4.10 Эквивалентность

Элемент реализует логическую функцию

.(4.10)

.(4.10)

Ниже показаны его обозначение на электрических схемах (рисунок 4.11) и таблица истинности (таблица 4.9).

Рисунок 4.11

Таблица 4.9

|

№ набора |

С |

В |

А |

F |

|

0 |

0 |

0 |

0 |

1 |

|

1 |

0 |

0 |

1 |

0 |

|

2 |

0 |

1 |

0 |

0 |

|

3 |

0 |

1 |

1 |

0 |

|

4 |

1 |

0 |

0 |

0 |

|

5 |

1 |

0 |

1 |

0 |

|

6 |

1 |

1 |

0 |

0 |

|

7 |

1 |

1 |

1 |

1 |

Функция равна единице, когда все переменные одинаковы (равны единице или нулю). В противном случае – F = 0.

4.11 Неэквивалентность

Элемент реализует логическую функцию

.(4.11)

.(4.11)

Ниже показаны его обозначение на электрических схемах (рисунок 4.12) и таблица истинности (таблица 4.10).

Рисунок 4.12

Таблица 4.10

|

№ набора |

С |

В |

А |

F |

|

0 |

0 |

0 |

0 |

0 |

|

1 |

0 |

0 |

1 |

1 |

|

2 |

0 |

1 |

0 |

1 |

|

3 |

0 |

1 |

1 |

1 |

|

4 |

1 |

0 |

0 |

1 |

|

5 |

1 |

0 |

1 |

1 |

|

6 |

1 |

1 |

0 |

1 |

|

7 |

1 |

1 |

1 |

0 |

Функция равна единице, когда переменные неодинаковы. В противном случае – F=0.

Если число логических переменных равно двум, то логическая функция и элемент “неэквивалентность ”совпадают с элементами “сумма по модулю два” и “исключающее ИЛИ” (таблицы 4.6, 4.7). Т. е., если Nпер=2, то

(4.11.1)

(4.11.1)

4.12 И–ИЛИ–НЕ

Элемент реализует более сложную логическую функцию, булево выражение которой имеет вид

.(4.12)

.(4.12)

Ниже показаны его обозначение на электрических схемах (рисунок 4.13) и таблица истинности (таблица 4.11).

Рисунок 4.13

Таблица 4.11

|

№ набора |

D |

С |

В |

А |

F |

|

0 |

0 |

0 |

0 |

0 |

1 |

|

1 |

0 |

0 |

0 |

1 |

1 |

|

2 |

0 |

0 |

1 |

0 |

1 |

|

3 |

0 |

0 |

1 |

1 |

0 |

|

4 |

0 |

1 |

0 |

0 |

1 |

|

5 |

0 |

1 |

0 |

1 |

1 |

|

6 |

0 |

1 |

1 |

0 |

1 |

|

7 |

0 |

1 |

1 |

1 |

0 |

|

8 |

1 |

0 |

0 |

0 |

1 |

|

9 |

1 |

0 |

0 |

1 |

1 |

|

10 |

1 |

0 |

1 |

0 |

1 |

|

11 |

1 |

0 |

1 |

1 |

0 |

|

12 |

1 |

1 |

0 |

0 |

0 |

|

13 |

1 |

1 |

0 |

1 |

0 |

|

14 |

1 |

1 |

1 |

0 |

0 |

|

15 |

1 |

1 |

1 |

1 |

0 |

4.13 Запрет

Элемент реализует логическую функцию

.(4.13)

.(4.13)

Ниже показаны его обозначение на электрических схемах (рисунок 4.14) и таблица истинности (таблица 4.12).

Рисунок 4.14

Таблица 4.12

|

№ набора |

B |

A |

F |

|

0 |

0 |

0 |

0 |

|

1 |

0 |

1 |

1 |

|

2 |

1 |

0 |

0 |

|

3 |

1 |

1 |

0 |

На выходе такого элемента логическая единица будет лишь в том случае, если на основном входе присутствует логическая единица (А=1), а на запрещающем входе– нуль (В=0)

В обозначении элемента на электрических схемах запрещающий вход отмечен как инверсный – кружком. Запрещающим сигналом на этом входе будет логическая единица.

4.14 Логические элементы с открытым коллектором

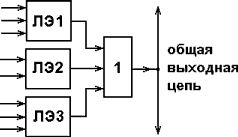

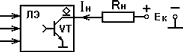

При построении цифровых устройств часто возникает необходимость объединения выходов нескольких логических элементов с целью перехода на общую выходную цепь. Эту задачу можно решить с помощью элемента ИЛИ (рисунок 4.15).

Рисунок 4.15

При этом приходится мириться с дополнительными схемными затратами и увеличением суммарной задержки прохождения цифровых сигналов через устройство.

Другой способ

основан на применении логических

элементов с открытым коллектором, в

поле функционального обозначения

которых имеется специальный символ

,

указывающий, что коллектор выходного

транзистора открыт (оборван, “висит в

воздухе”).

,

указывающий, что коллектор выходного

транзистора открыт (оборван, “висит в

воздухе”).

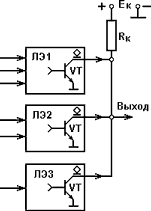

На рисунке 4.16 показано объединение нескольких логических элементов с открытым коллектором на общий выход.

Рисунок 4.16

Для нулевых сигналов на выходах логических элементов ЛЭ1...ЛЭ3 (соответствующий выходной транзистор открыт) данная схема выполняет функцию “монтажное ИЛИ”: при появлении логического нуля хотя бы на одном из выходов логических элементов выходной сигнал также будет равен нулю.

Для единичных сигналов на выходах логических элементов ЛЭ1...ЛЭ3 (соответствующий выходной транзистор закрыт) схема выполняет функцию “монтажное И”: выходной сигнал равен единице лишь при одновременном появлении логических единиц на выходах всех логических элементов.

За счет технологии изготовления выходного транзистора и получения от него заданных характеристик элементы с открытым коллектором обладают более высокой нагрузочной способностью, чем обычные ЛЭ, поэтому могут использоваться для подключения нагрузок типа тиристоров, реле, индикаторов (светодиодов) и т.п. (рисунок 4.17).

Рисунок 4.17

При этом необходимо обеспечить выполнение условия

,(4.14)

,(4.14)

где Iн

– ток нагрузки;

–

значение допустимого тока, который

может протекать через открытый выходной

транзистор логического элемента (рисунок

4.17).

–

значение допустимого тока, который

может протекать через открытый выходной

транзистор логического элемента (рисунок

4.17).

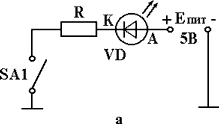

На рисунке 4.17.1 показан пример подключения на выход ЛЭ с открытым коллектором светодиода VD.

Рисунок 4.17.1

Когда с выхода ЛЭ снимается логический 0, выходной транзистор VT открыт, и светодиод VD оказывается включенным в прямом направлении. При протекании через VD прямого тока последний зажигается. Ток Iн равен току зажигания светодиода Iзаж.VD, который составляет 20 mA. Падение напряжения на открытом диоде UVD.пр составляет (1,7…2) В. Резистор R ограничивает величину прямого тока и рассчитывается по формуле:

(4.14.1)

(4.14.1)

Например, если Ek=5 B; UVD.пр=2 В; Iзаж.VD=20 mA, то R=(5-2)/(20*10-3)=150 Ом.

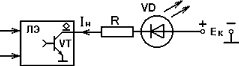

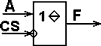

4.15 Логические элементы с третьим состоянием

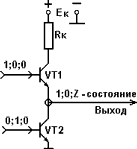

Один из наиболее широко используемых способов подключения логических элементов на общий выход основан на применении в их выходных цепях электронных буферных схем, способных под действием управляющих сигналов либо подключать к нагрузке выходной логический сигнал, принимающий значения (состояния) 0 или 1, либо отключать выход от нагрузки (переводить его в так называемое 3-е (высокоимпедансное, Z-состояние)).

Ниже показаны: обозначение логического элемента (повторителя) с тремя состояниями на электрических схемах (рисунок 4.18,а) и принципиальная схема его выходного каскада, обеспечивающего 3 состояния выходного сигнала: логический 0; логическую 1 и 3-е (Z) состояние (рисунок 4.18,б).

Рисунок 4.18

В поле

функционального обозначения логических

элементов с тремя состояниями имеется

специальный символ

.

.

Помимо основных входов, на которые подаются входные логические переменные, подобные элементы содержат управляющий вход “Выбор кристалла” - CS, активным сигналом на котором, как правило, является логический 0 (рисунок 4.18,а).

Три состояния выходных сигналов обеспечиваются управляющими сигналами на базах транзисторов VT1 и VT2 (рисунок 4.18,б):

Единичное состояние – на базе VT1 - единица (транзистор - открыт); на базе VT2 - нуль (транзистор - закрыт) и с выхода снимается логическая 1;

Нулевое состояние – на базе VT1 - нуль (транзистор закрыт); на базе VT2 - единица (транзистор - открыт) и с выхода снимается логический 0;

Z - состояние – на базах VT1 и VT2 - логические нули (оба транзистора закрыты) и выход оборван от общей шины (находится в высокоимпедансном (Z) состоянии).

Элементы с тремя состояниями широко используются в микропроцессорной технике для подключения выходов различных устройств микропроцессорной системы к общей шине.

5. РЕАЛИЗАЦИЯ ЛОГИЧЕСКИХ ФУНКЦИЙ в разных базисах

5.1 Базисные наборы ЛЭ и их взаимосвязь

Существует несколько базисных (функционально полных) наборов логических элементов, на которых можно реализовывать любую переключательную функцию:

1) И, ИЛИ, НЕ;

2) И – НЕ;

3) ИЛИ - НЕ.

Для реализации ПФ, представленной булевым выражением в ДНФ или КНФ, достаточно трех ЛЭ: И, ИЛИ, НЕ, поэтому этот набор считается функционально полным или базисным (базисом).

На практике более широко используются базисы И-НЕ или ИЛИ-НЕ. Это связано с тем, что уменьшение номенклатуры элементов до одного типа упрощает проектирование устройства и его ремонт. Кроме того, наличие в этих элементах инвертора (усилителя) повышает нагрузочную способность элемента (усиливает сигнал).

Используя тождества и теоремы булевой алгебры, можно преобразовать выражения ПФ, записанные в виде комбинации функций И, ИЛИ, НЕ, к виду, который может быть реализован элементами базиса И-НЕ, ИЛИ-НЕ. Сказанное отражает таблица 5.1.

Таблица 5.1

|

Элемент |

Логические операции |

||

|

НЕ |

И |

ИЛИ |

|

|

И-НЕ |

|

|

|

|

ИЛИ-НЕ |

|

|

|

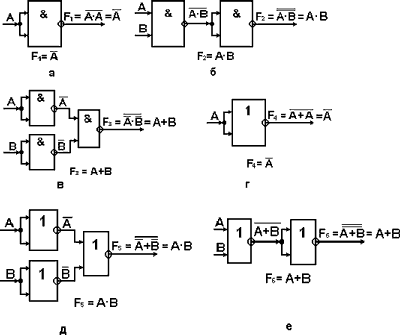

Ниже показана схемная реализация функций НЕ, И, ИЛИ в базисах И-НЕ (рисунок 5.1, а, б, в) и ИЛИ-НЕ ( рисунок 5.1 ,г, д, е).

Рисунок 5.1

Функцию И-НЕ называют функцией Шеффера (штрихом Шеффера), обозначая её в виде F = A B, а функцию ИЛИ-НЕ - функцией Пирса (стрелкой Пирса), обозначая её в виде АВ. Базис И-НЕ называют базисом Шеффера, а базис ИЛИ-НЕ - базисом Пирса.

5.2 Реализация логических функций в различных базисах

5.2.1 Реализация элемента “Равнозначность” (исключающее ИЛИ - НЕ)

На выходе такого элемента должна быть логическая 1, если на входах одновременно присутствуют одинаковые логические переменные (единицы или нули).

Булево выражение логической функции, соответствующей рассматриваемому элементу имеет вид

.(5.1)

.(5.1)

Очевидно, что данное выражение легко реализуется элементами базиса И, ИЛИ, НЕ.

Используя теорему де Моргана и тождества булевой алгебры, преобразуем выражение (5.1) к виду, позволяющему реализовать функцию “равнозначность” в базисе И-НЕ (5.2) и ИЛИ-НЕ (5.3)

,(5.2)

,(5.2)

.(5.3)

.(5.3)

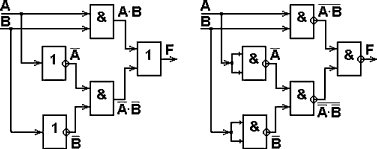

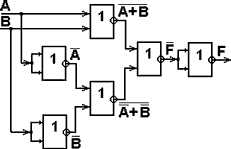

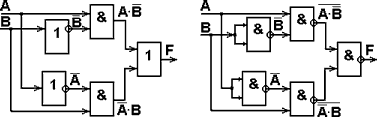

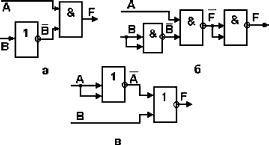

Ниже показаны функциональные схемы элемента “равнозначность” на ЛЭ базисов И, ИЛИ, НЕ (рисунок 5.2,а); И-НЕ (рисунок 5.2,б) и ИЛИ-НЕ (рисунок 5.2,в).

А Б

В

Рисунок 5.2

5.2.2 Реализация элемента “Неравнозначность” (исключающее ИЛИ, сумма по модулю два)

На выходе такого элемента должна быть логическая 1, если на входах присутствуют неравнозначные логические переменные:

F = 1, если А = 1, В = 0 или А = 0, В = 1.

Булево выражение логической функции рассматриваемого элемента имеет вид

.(5.4)

.(5.4)

Это выражение может быть легко реализовано элементами базиса И, ИЛИ, НЕ. Применяя теорему де Моргана и тождества булевой алгебры, преобразуем выражение (5.4) к виду, позволяющему реализовать функцию “неравнозначность” в базисе И-НЕ (5.5) и ИЛИ-НЕ (5.6).

,(5.5)

,(5.5)

.(5.6)

.(5.6)

Ниже показаны функциональные схемы элемента “неравнозначность” на ЛЭ базисов И, ИЛИ, НЕ (рисунок 5.3, а); И-НЕ (рисунок 5.3, б) и ИЛИ-НЕ (рисунок 5.3, в).

А Б

В

Рисунок 5.3

Элемент “неравнозначность” иначе называют сумматором по модулю два: сумма двоичных цифр дает единицу, если одна из них единица, а другая – нуль; в противном случае, если обе цифры 0 или 1, то сумма равна нулю.

5.2.3 Реализация элемента “Запрет”

На выходе такого элемента должна быть логическая 1, если на основном входе присутствует логическая единица, а на запрещающем входе – логический нуль.

Булево выражение логической функции рассматриваемого элемента имеет вид

.(5.7)

.(5.7)

Выражение (5.7) может быть легко реализовано в базисе И, ИЛИ, НЕ.

Применяя теорему де Моргана и тождества булевой алгебры, преобразуем выражение (5.7) к виду, позволяющему реализовать функцию “запрет” в базисе И-НЕ (5.8) и ИЛИ-НЕ (5.9).

,(5.8)

,(5.8)

.(5.9)

.(5.9)

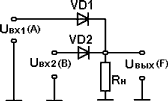

Ниже показаны функциональные схемы элемента “запрет” на ЛЭ базисов И, ИЛИ, НЕ (рисунок 5.4, а); И-НЕ (рисунок 5.4, б) и ИЛИ-НЕ (рисунок 5.4, в).

Рисунок 5.4

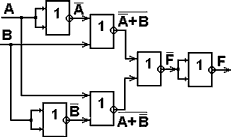

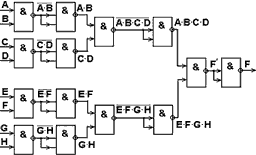

5.2.4 Реализация многобуквенных логических функций на элементах с небольшим количеством входов

Иногда на практике возникает задача реализовать логическую функцию большого числа логических переменных (многобуквенную функцию) на элементах с небольшим количеством входов. В качестве примера на рисунке 5.5 показана функциональная схема, реализующая логическую функцию

(5.10)

(5.10)

на двухвходовых элементах И-НЕ.

Рисунок 5.5

6. ПАРАМЕТРЫ И ХАРАКТЕРИСТИКИ ЦИФРОВЫХ ИНТЕГРАЛЬНЫХ МИКРОСХЕМ (ИМС)

Цифровая микросхема как функциональный узел характеризуется набором сигналов, которые можно разделить на информационные (Х1, Х2, ..., Хn – входные, Y1, Y1, ..., Ym – выходные) и управляющие (V1, V2, ..., Vk). Каждая конкретная ИМС в соответствии со своим функциональным назначением выполняет определенные операции над входными сигналами (переменными), а выходные сигналы представляют собой результат этих операций Yj = F(Х1,Х2, ... ,Хn). Операторами F могут быть как простейшие логические преобразования, например, И, ИЛИ, НЕ, и т. д., так и сложные многофункциональные преобразования, имеющие место, например, в микропроцессорах, БИС памяти и др.

Сигналы управления определяют вид операции, режим работы ИМС, обеспечивают синхронизацию, установку начального состояния, стробируют входные и выходные сигналы, задают адрес, и т. д.

От функциональной сложности ИМС зависит и система ее электрических параметров, которые в общем случае могут иметь десятки наименований, причем многие из параметров характерны только для ИМС какого-либо одного класса. Поэтому ниже рассмотрим те параметры и характеристики, которые характеризуют большинство микросхем. В дальнейшем при изучении отдельных устройств этот перечень по мере необходимости будет расширен.

6.1 Коэффициент объединения по входу (Коб)

Равен числу входов логического элемента. На них поступают логические переменные, над которыми данный элемент выполняет логическую операцию. Коб ограничивает наибольшее число переменных функции, которую реализует данный ЛЭ. При недостаточном количестве входов вместо одного приходится использовать несколько элементов, соединяя их определенным образом (5.2.4).

6.2 Коэффициент разветвления по выходу (Краз)

Численно равен количеству входов аналогичных элементов, которыми можно одновременно нагрузить выход данного элемента без искажения передачи информации. Этот коэффициент характеризует нагрузочную способность элемента и определяется выполнением его выходного каскада. Для различных элементов составляет от нескольких единиц до нескольких десятков.

6.3 Статические характеристики

К статическим характеристикам относятся: входная ВАХ, определяющая зависимость входного тока от входного напряжения; выходная ВАХ, показывающая связь между выходным напряжением и током; передаточная, которая определяет зависимость выходного напряжения от входного [3].

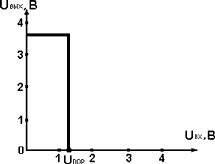

На рисунке 6.1 приведена типовая передаточная характеристика инвертора ТТЛ - типа. С ее помощью можно определить ряд параметров ЛЭ, например, уровни напряжений логической единицы (U1), логического нуля (U0), значения пороговых напряжений, при которых выходной сигнал переключается из 1 в 0 (U0пор) и наоборот из 0 в 1 (U1пор), оценить помехоустойчивость элемента.

Рисунок 6.1

6.4 Помехоустойчивость

Оценивается наибольшим напряжением статической помехи Uпом, действующей на входе, которое не вызывает ложного переключения элемента из 1 в 0, или наоборот.

Статическими принято называть помехи, величина которых остается постоянной в течение времени, значительно превышающего длительность переходных процессов в схеме. Причиной появления таких помех в большинстве случаев является падение напряжения на проводниках, соединяющих микросхемы в устройстве. Наиболее опасные помехи возникают в шинах питания. Падения напряжения на “земляной” шине, разные для различных ИМС, будут суммироваться с входными сигналами и могут приводить к сбоям. Для исключения подобных ситуаций необходимо внимательно относиться к расположению проводников, подводящих напряжение питания, и увеличивать по возможности их сечение.

Помехоустойчивость можно оценить по передаточной характеристике элемента (рисунок 6.1), определив значения U0пом и U1пом.

6.5 Динамические характеристики и параметры

Характеризуют быстродействие логических элементов.

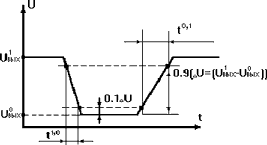

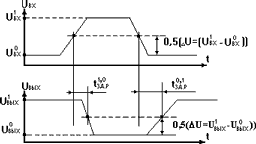

На рисунке 6.2 изображено изменение выходного напряжения во времени при переключении из 1 в 0 и наоборот.

Рисунок 6.2

По этой характеристике определяется время перехода элемента из состояния единицы в нуль t1,0 и перехода в обратное состояние t0,1. Эти временные интервалы измеряются на уровнях 0,1 и 0,9 от перепада выходного напряжения при переключении элемента (ΔU = (U1вых – U0вых)) (при этом емкость нагрузки должна соответствовать заданной).

Часто быстродействие оценивается временами задержки распространения сигнала при включении t0,1зд.р. и выключении t1,0зд.р. ,а также средним временем задержки распространения tзд.р.ср (определяется как полусумма задержек при включении и выключении). Эти параметры измеряются на уровнях 0,5 от перепадов входного и выходного сигналов (рисунок 6.3).

Рисунок 6.3

6.6 Вид реализуемой логической функции

Выше, при изложении курса, были рассмотрены основные логические элементы, выполняющие различные функции: И, ИЛИ, НЕ, И-НЕ, ИЛИ-НЕ; ИСКЛЮЧАЮЩЕЕ ИЛИ, ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ; И-ИЛИ-НЕ; ПОВТОРЕНИЕ (усиление цифрового сигнала) и др.

6.7 Потребляемые токи и мощность

К основным параметрам часто также относят токи, потребляемые цифровой ИМС для двух её состояний: I1пот, I0пот, и потребляемую мощность Рпот.

Рпот представляет собой мощность, потребляемую микросхемой от источника питания в заданном режиме. Различают Р1пот и Р0пот, потребляемые ИМС в состояниях логических 1 и 0, а также среднюю потребляемую мощность

Рпот.ср = 0,5*( Р1пот + Р0пот).(6.1)

6.8 Входные и выходные токи, напряжения

I0вх – предельный входной ток при сигнале 0 на входе;

I1вх – предельный входной ток при сигнале 1 на входе;

U1вых – минимальное выходное напряжение при логической 1 на выходе при заданном токе нагрузки;

U0вых – максимальное выходное напряжение при сигнале 0 на выходе при заданном токе нагрузки;

I0вых max – максимальный выходной ток при логическом нуле на выходе;

I1вых max – максимальный выходной ток при логической единице на выходе.

6.9 Пороговые напряжения

Входное напряжение, при котором происходит резкое изменение выходного напряжения, называется порогом переключения Uпор. Амплитудная передаточная характеристика реального логического элемента в переходной области (штриховая линия) не имеет явно выраженного порога переключения (рисунок 6.1). Изменение выходного напряжения начинается при одном значении входного напряжения U0пор, а заканчивается при другом U1пор. Характеристика имеет зону неопределенности ΔUпор=U1пор-U0пор, что вызвано, в частности, переходом транзистора из режима отсечки в режим насыщения и наоборот.

Пороговое напряжение логического нуля U0пор – наибольшее значение низкого уровня входного напряжения, при котором происходит переход из единичного состояния в нулевое (рисунок 6.1);

Пороговое напряжение логической единицы U1пор – наименьшее значение высокого уровня входного напряжения, при котором происходит переход из нулевого состояния в единичное (рисунок 6.1).

Значение U0пор и U1пор отличаются на несколько десятых долей вольта, поэтому часто передаточная характеристика аппроксимируется, как показано на рисунке 6.4.

Рисунок 6.4

Теперь Uпор= U1пор= U0пор.

6.10 Допустимые значения основных параметров

Emin, Emax – допустимые значения напряжения питания;

U1min, U0max – допустимые значения уровней логических сигналов единицы и нуля;

Iвх.max, I0вых.max, I1вых.min – допустимый входной и выходной токи в состоянии 0 и 1.

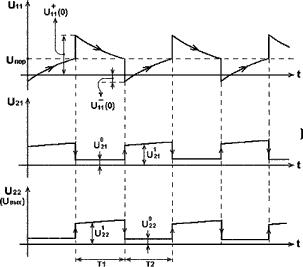

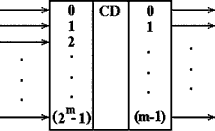

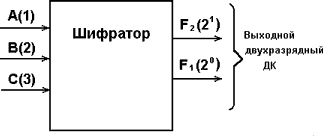

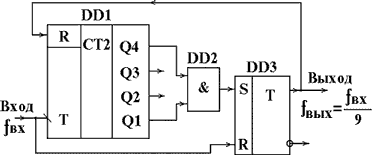

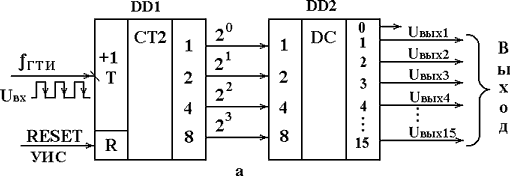

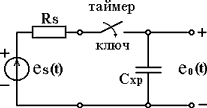

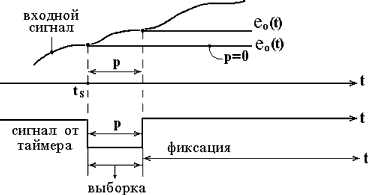

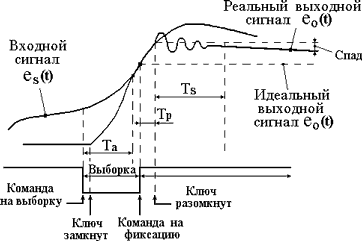

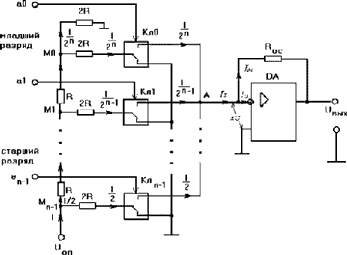

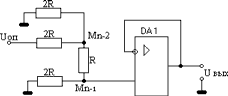

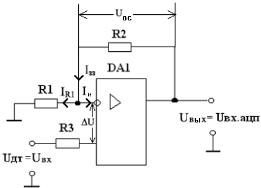

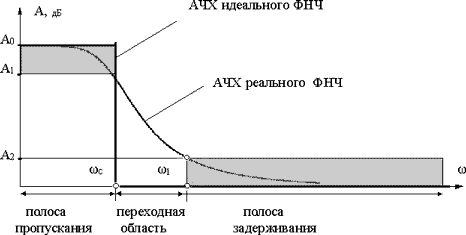

Существует еще ряд параметров, например, технико-экономических, которые приводятся в технической документации, прилагаемой к ИМС, и в справочниках.