Проектирование цифровых устройств в САПР ISE

Кафедра

"Вычислительная техника"

Курсовая работа

На тему: Проектирование цифровых устройств в САПР ISE

Москва, 2009

Содержание

Введение

1. Ввод проекта

2. Моделирование

3. Синтез и реализация проекта на ПЛИС типа CPLD

4. Синтез и реализация проекта на ПЛИС типа FPGA

5. Разработка регистровой схемы

6. Разработка умножителя

7. Использование структурного описания

Литература

Введение

Для проектирования цифровых устройств на ПЛИС фирмы Xilinx с применением языка VHDL могут использоваться различные системы, в том числе широко известная система Leonardo Spectrum, Foundation Express и Integrated Synthesis Environment (ISE). В настоящей главе рассматривается работа системы ISE. Характерной особенностью САПР фирмы Xilinx является привлечение для синтеза на языке VHDL синтезаторов третьих фирм. Исключением из этого правила является технология XST, используемая в САПР ISE. Использование этой технологии и рассматривается в данной главе.

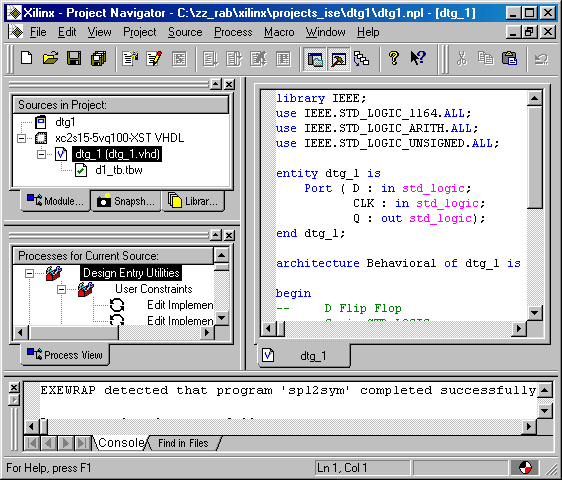

Работой САПР управляет Навигатор проекта (Project Navigator), который предоставляет пользователю удобный интерфейс для работы с проектом. Основное окно Навигатора проекта (см. рис. 2.1) содержит четыре встроенных окна: окно исходных модулей (файлов) проекта (Sources in Project), окно процессов для выбранного исходного модуля проекта (Processes for Current Source), окно консольных сообщений программных модулей (Console) и окно текстового редактора HDL-описаний.

В окне исходных модулей отображается иерархическая структура проекта, содержащая описание проектируемого устройства, а также описание тестовых воздействий, используемых в процессе моделирования. Каждый тип модуля имеет соответствующее графическое обозначение (пиктограмму). Окно процессов отображает этапы разработки и программирования ПЛИС, последовательность и содержание этапов определяется типом исходного модуля и семейством ПЛИС. В этом же окне указывается информация о дополнительных инструментах, которые могут быть использованы на каждом этапе. Окно консольных сообщений предназначено для вывода информации программных модулей, которые не создают собственных окон.

Рис. 2.1. Основное окно Навигатора проекта

В процессе создания цифровых устройств с использованием САПР ISE можно выделить следующие этапы: создание нового проекта, ввод описания проектируемого устройства, этап синтеза схемы, моделирование устройства, реализация проекта в ПЛИС и ее программирование.

При создании проекта задается тип проекта, его местоположение на диске, тип ПЛИС и другая информация. Ввод схемы или описания проектируемого устройства может осуществляться различными методами, в том числе схемотехническими; в настоящей главе рассматривается только проектирование с использованием языка VHDL. Процесс синтеза осуществляется автоматически средствами САПР. На этапе реализации проекта в ПЛИС выполняется размещение элементов в программируемые логические блоки ПЛБ и трассировка связей с учетом типа используемой ПЛИС. В процессе трассировки также определяются реальные значения задержек распространения сигналов, которые могут использоваться для временного моделирования схемы. Завершающим этапом является загрузка конфигурационных данных в ПЛИС с помощью соответствующих программ и загрузочного кабеля.

Важным моментом при разработке схем на ПЛИС является моделирование разработанных устройств. Обычно средства моделирования органично вписываются в систему проектирования, и пользователю предоставляются самые разнообразные, достаточно мощные и в то же время удобные средства. Однако в системе ISE для моделирования используется дополнительная программа ModelSim. В современных системах проектирования имеется несколько вариантов моделирования. Функциональное моделирование без учета задержек является наиболее простым и быстрым и позволяет провести предварительную проверку проекта с целью выявления грубых ошибок. Для более детального исследования схемы проводится функциональное моделирование с учетом задержек, которые обычно считаются равными для всех элементов схемы. Окончательная проверка производится с использованием схемного (временного) моделирования реализованного проекта после размещения элементов на кристалле и трассировки связей.

1. Ввод проекта

Основные методы и приемы работы с САПР ISE рассмотрим на примере простейшей схемы D –триггера. Использование простейшей схемы позволяет отвлечься от особенностей самой схемы и сосредоточиться только на самом процессе проектирования.

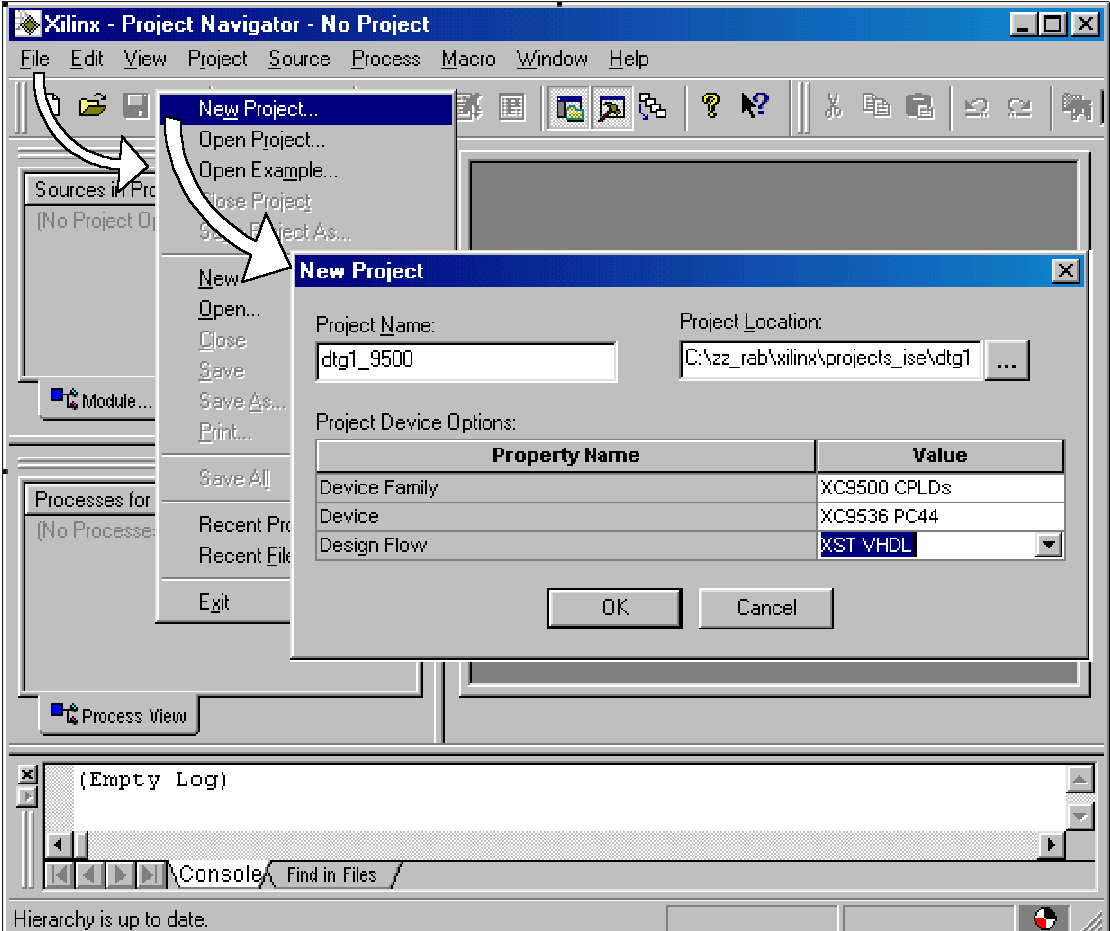

Создание нового проекта инициируется последовательным выбором пунктов меню File New Project (эта последовательность показана на рис. 2.2). При этом открывается диалоговая панель, в которой разработчик должен указать имя и расположение проекта на жестком диске, а также выбрать семейство ПЛИС, тип кристалла и средства синтеза устройства. На рис. 2.2 выбрана ПЛИС XC9536-PC44, метод проектирования – использование языка VHDL с использованием технологии XST.

Рис. 2.2. Создание нового проекта

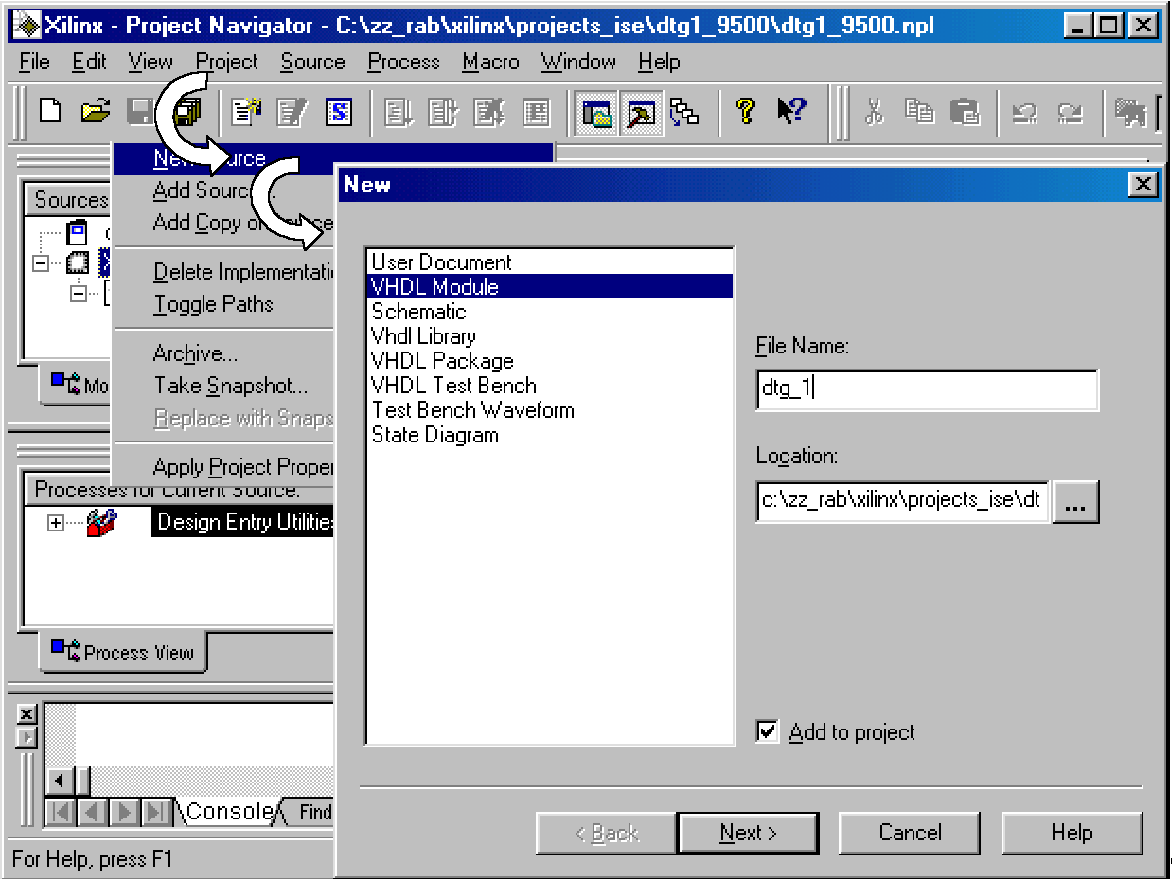

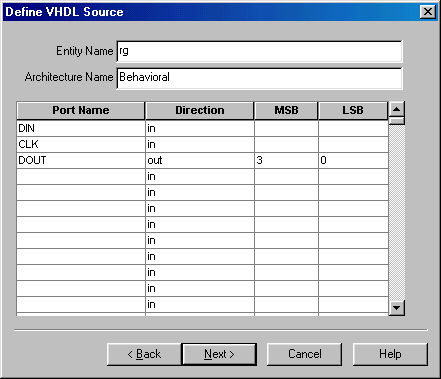

После ввода указанных данных в окне исходных модулей проекта появится пиктограмма основного модуля с указанием типа кристалла и инструментов синтеза. Для ввода описания следует выбрать пункты меню Project New Source, после чего открывается список возможных типов исходных модулей (см. рис. 2.3): схемотехническое представление, описание модулей, библиотек и тестовых воздействий на языке HDL, диаграмма состояний, модули документации. В этом списке следует выбрать тип нового исходного модуля (в данном случае - пункт VHDL module) и указать имя файла.

Рис. 2.3. Список типов исходных модулей

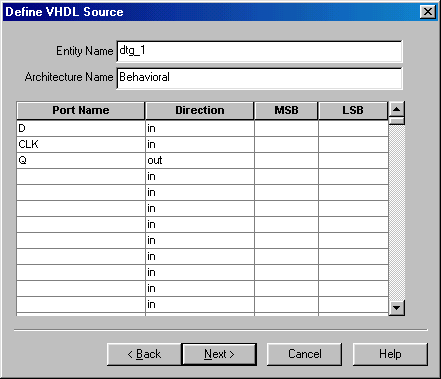

Если нажать клавишу Next, то активизируется окно задания внешних сигналов (Define VHDL Source). Для D –триггера надо задать входные сигналы информационного входа D, синхросигнала CLK и выходной сигнал Q (см. рис. 2.4). После этого по нажатию клавиши Next открывается окно New Source Information, в котором приводится информация о новом модуле. В случае успешного завершения создания исходного модуля он автоматически добавляется к проекту и отображается в окне исходных модулей в виде соответствующей пиктограммы.

Рис. 2.4. Задание внешних сигналов

В окне текстового редактора будут введены следующие строки

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity dtg_1 is

Port ( D : in std_logic;

CLK : in std_logic;

Q : out std_logic);

end dtg_1;

architecture Behavioral of dtg_1 is

begin

end Behavioral;

Для разработки описания разрабатываемой схемы на языке VHDL целесообразно использовать шаблоны языка («Language Template»). В списке шаблонов имеются описания счетчиков, мультиплексоров, дешифраторов и других узлов. Шаблоны языка могут быть скопированы и вставлены в проект, а затем изменены так, как удобно разработчику. Список шаблонов открывается при выборе пунктов меню Edit Language Template. В открывшемся окне Templates необходимо выбрать пункт VHDL, а затем - Synthesis Templates. В списке шаблонов выбирается Flip Flop, а затем шаблон D –триггера, который содержит следующие строки:

-- D Flip Flop

-- CLK: in STD_LOGIC;

-- DIN: in STD_LOGIC;

-- DOUT: out STD_LOGIC;

process (CLK)

begin

if CLK'event and CLK='1' then --CLK rising edge

DOUT <= DIN;

end if;

end process;

end Behavioral;

Эти строки надо вставить между строками begin и end Behavioral, окончательный вид исходного модуля будет иметь следующий вид:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity dtg_1 is

Port ( D : in std_logic;

CLK : in std_logic;

Q : out std_logic);

end dtg_1;

architecture Behavioral of dtg_1 is

begin

-- D Flip Flop

-- CLK: in STD_LOGIC;

-- DIN: in STD_LOGIC;

-- DOUT: out STD_LOGIC;

process (CLK)

begin

if CLK'event and CLK='1' then --CLK rising edge

DOUT <= DIN;

end if;

end process;

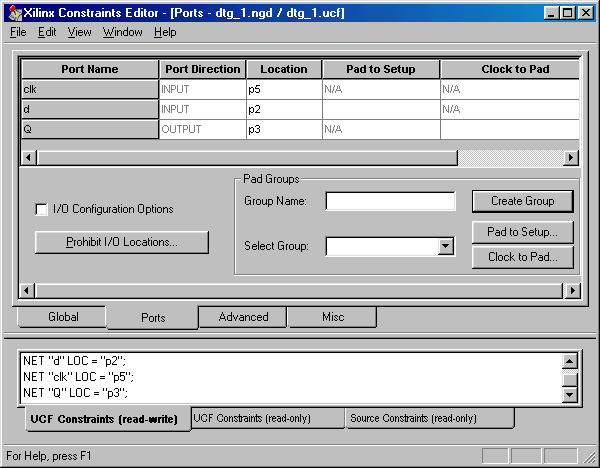

Для задания номеров контактов ПЛИС, на которые выводятся выходные сигналы, можно использовать редактор ограничений (Constraints Edior). Для его запуска в окне процессов для выбранного исходного модуля проекта (Processes for Current Source) надо последовательно раскрыть пиктограммы утилит ввода проекта (Design Entry Utilities) и ограничений пользователя (User Constraints). После этого надо запустить программу редактора ограничений (строка Edit Implementation Constraints - Constraints Edior), окно которой приведено на рис. 2.5, и заполнить столбец Location.

Рис. 2.5. Установка номеров контактов

В этом же редакторе вводятся и временные ограничения, такие, как, максимальное значение периода, время распространения сигналов в логических схемах от контакта к контакту, предельное время между синхросигналом и связанными с ним управляющими сигналами и другие ограничения.

2. Моделирование

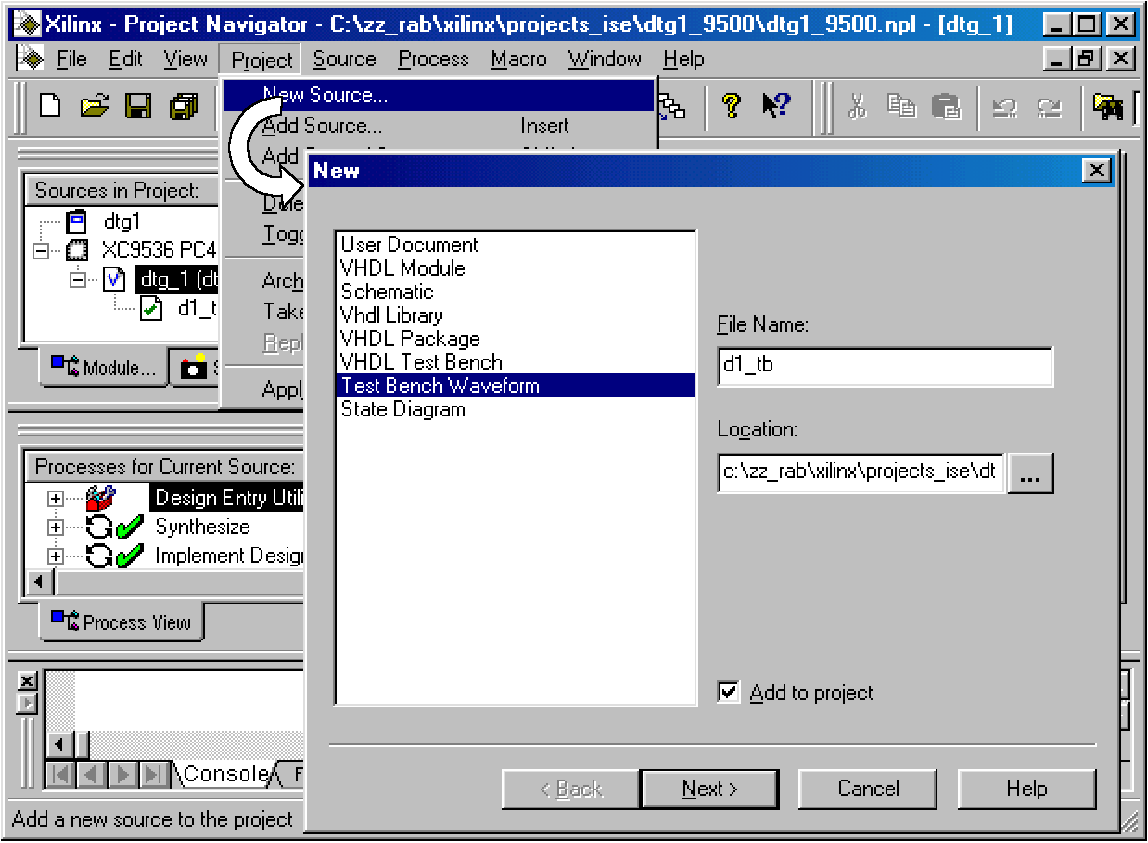

Одним из основных этапов при разработке схем на ПЛИС является моделирование разработанных устройств. После ввода описания схемы обычно проводится функциональное моделирование, оно позволяет провести предварительную проверку проекта. В системе ISE для моделирования используется программа ModelSim. Для задания сигналов системы моделирования в САПР ISE используются возможности программы Test Behcher. Вызов этой программы производится из основного меню последовательным выбором следующих пунктов: Project New Source Test Bench Waveform (см. рис. 2.5 а). Выбор пункта Test Bench Waveform позволяет задавать входные сигналы в виде временных диаграмм. При выборе пункта VHDL Test Bench входные воздействия описываются средствами языка VHDL.

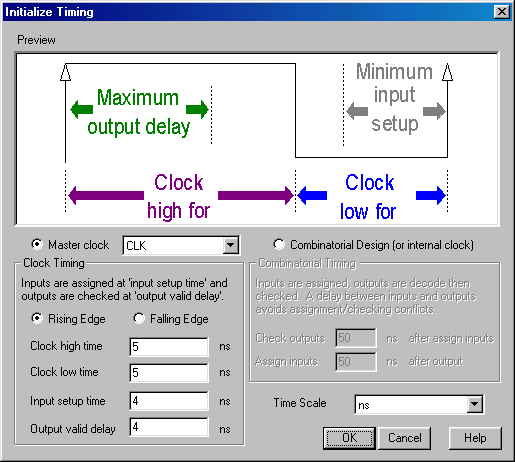

После запуска программы Test Behcher последовательно открываются несколько окон, в которых надо нажать клавиши Next и Finish. В результате в окне исходных модулей добавляется новый модуль (на рис. 2.6 а показано задание модуля с именем d1_tb). Перед началом работы в окне инициализации, приведенном на рис. 2.6 б, задаются временные характеристики синхросигнала и положение фронтов управляющих воздействий относительно фронтов тактового сигнала. Сущность вводимых значений поясняется на рисунке, приведенном в верхней части окна, показанного на рис. 2.6.

а.

б

Рис. 2.6. Задание параметров синхросигнала с помощью программы Test Behcher

В примере, приведенном на рис. 2.6 б, задаются длительности единичного (Clock high time: 5 ns) и нулевого (Clock low time: 5 ns) значения синхросигнала, время установки входных воздействий перед фронтом тактового сигнала (Input setup time: 4 ns) и время задержки выходных значений (Output valid delay: 4 ns). Затем в окне программы Test Behcher вводятся временные диаграммы входных воздействий (см. рис. 2.7).

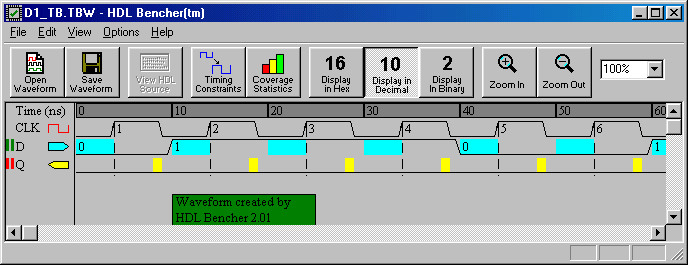

Рис. 2.7. Задание входных сигналов

Программа Test Behcher позволяет также задавать выходные воздействия, но в данном примере они не используются.

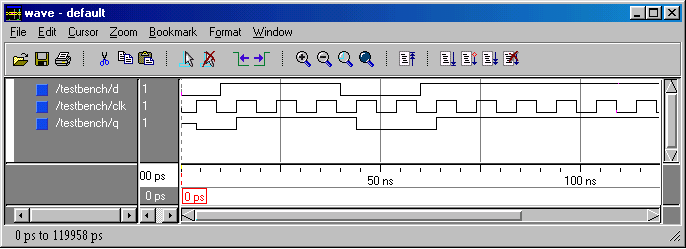

Для моделирования в окне исходных модулей необходимо выбрать файл входных воздействий, созданный в программе Test Behcher, а в окне процессов - «Behavioural VHDL Model». В результате запуска программы моделирования открывается несколько окон, в том числе окно просмотра результатов, показанное на рис. 2.8.

Рис. 2.8. Результаты моделирования

3. Синтез и реализация проекта на ПЛИС типа CPLD

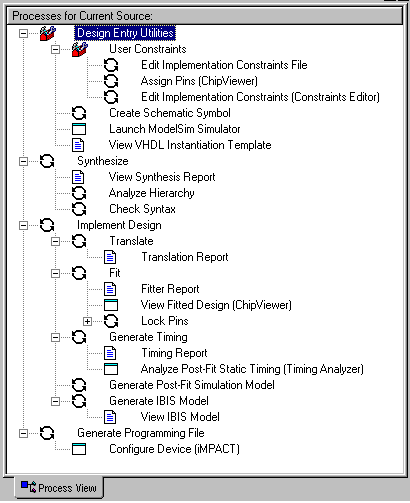

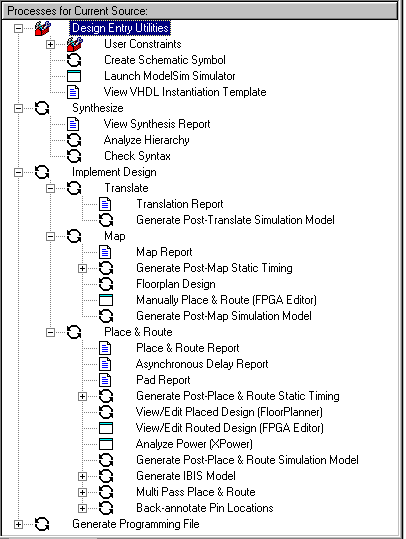

Этапы синтеза и реализации проекта выполняются в САПР ISE автоматически. Процессы реализации на ПЛИС типа CPLD и ПЛИС типа FPGA отличаются друг от друга. На рис. 2.9 показано окно процессов для ПЛИС типа CPLD.

Рис. 2.9. Окно процессов для ПЛИС типа CPLD

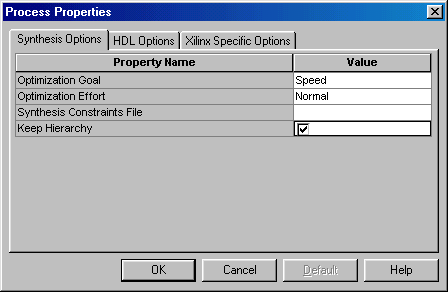

Для запуска этих процессов достаточно выбрать исходный файл в окне исходных модулей и дважды нажать левой клавишей мыши на нужном процессе в окне процессов, например, на пункте Implement Design. При необходимости проектировщик может проконтролировать и задать параметры синтеза и реализации. На рис. 2.10 в качестве примера показана диалоговая панель параметров синтеза.

Рис. 2.10. Диалоговая панель параметров синтеза.

Эта панель вызывается нажатием правой клавиши мыши на строке Synthesise в окне процессов. Здесь можно изменить такие параметры, как критерий оптимизации (Optimization Goal), уровень оптимизации (Optimization Effort) и другие.

В результате выполнения этих этапов создается ряд отчетов. Отчет о результатах синтеза (Synthesis Report) содержит параметры синтеза, информацию о ходе компиляции исходных модулей, сообщения об ошибках и другую информацию. В отчете о выполнении процесса трансляции приведены командные строки, информация об ошибках, информация о создаваемых файлах. Отчет о размещении (Fitter Report) содержит общую информацию о ресурсах ПЛИС, об общем количестве и числе используемых блоков ПЛБ, выходных контактов и их использовании и другую информацию. Так, например, отчет об использовании ресурсов содержит следующие строки:

Macrocells Product Terms Registers Pins Function Block

Used Used Used Used Inputs Used

1/36(2%) 1/180(0%) 1/36(2%) 3/34(8%) 1/72(1%)

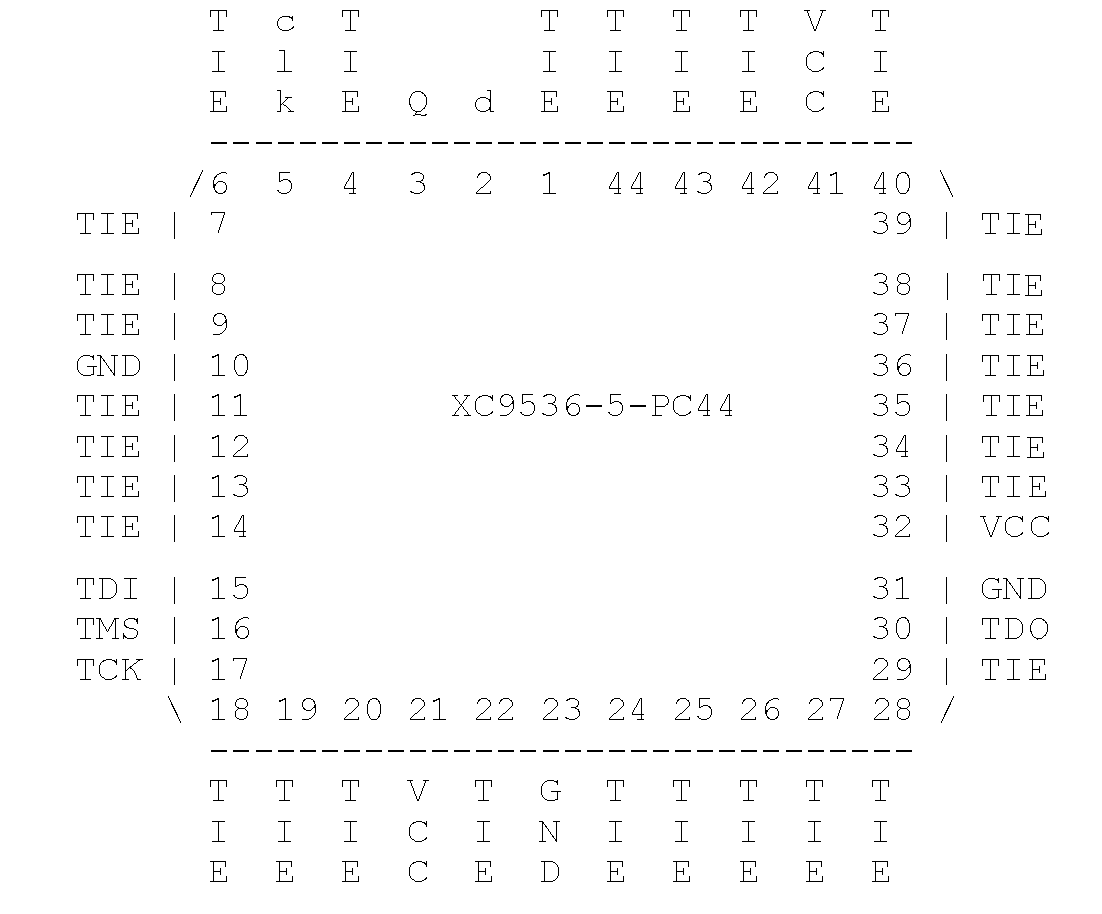

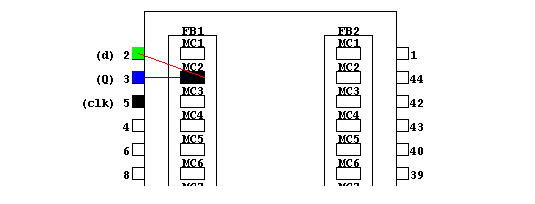

Стилизованное изображение микросхемы с распределением внешних сигналов по контактам показано на рис. 2.11.

Рис. 2.11. Вид микросхемы XC9536-5-PC44

Отчет о результатах временного анализа (Timing Report) позволяет оценить временные характеристики полученной схемы. Так, например, запись Clock Pad to Output Pad (tCO): 4.0ns (1 macrocell levels) характеризует время задержки срабатывания схемы после синхросигнала. Запись Minimum Clock Period: 8.0ns. свидетельствует о том, минимальный период синхросигнала составляет 8 нс, что соответствует максимальной частоте 125 МГц (Maximum Internal Clock Speed: 125.0Mhz).

Программа ChipViewer позволяет просмотреть распределение схемы по ресурсам микросхемы. На рис. 2.12 показан фрагмент схемы, из которой видно, какой функциональный блок используется, и на какие контакты выводятся внешние сигналы.

Рис. 2.12. Просмотр результатов размещения программой ChipViewer

4. Синтез и реализация проекта на ПЛИС типа FPGA

Создание проекта, ввод схемы, задание ограничений для ПЛИС типа FPGA, а также моделирование производятся также, как это описано в разделах 2.3 и 2.4. На рис. 2.13 показано окно процессов для ПЛИС типа FPGA. Содержание этих процессов отличается от процессов, приведенных на рис. 2.9, для предварительного размещения Map и окончательного размещения Place&Route.

Отчет о размещении и проведении связей (Place&Route Report) наряду с другой информацией содержит данные о задержках сигналов внутри ПЛИС. Эта информация представляет существенный интерес, так вследствие специфики структуры ПЛИС величина задержки зависит от взаимного расположения узлов и связей между ними. Пример фрагмента отчета приведен ниже:

The Average Connection Delay for this design is: 0.512 ns

The Maximum Pin Delay is: 1.102 ns

The Average Connection Delay on the Nets is: 0.138 ns

Listing Pin Delays by value: (ns)

d<1.00 <d<2.00 <d<3.00 <d<4.00 <d< 5.00 d>=5.00

2 1 0 0 0 0

Рис. 2.13. Окно процессов для ПЛИС типа FPGA

Вследствие ее важности информация о задержках приводится и в других отчетах. В отчете о задержках (Asynchronous Delay Report) приводится перечень задержек всех связей:

-------------------------------

| Max Delay (ns) | Netname |

-------------------------------

1.102 D_IBUF

0.426 clk_BUFGP

0.007 clk_BUFGP/IBUFG

---------------------------------

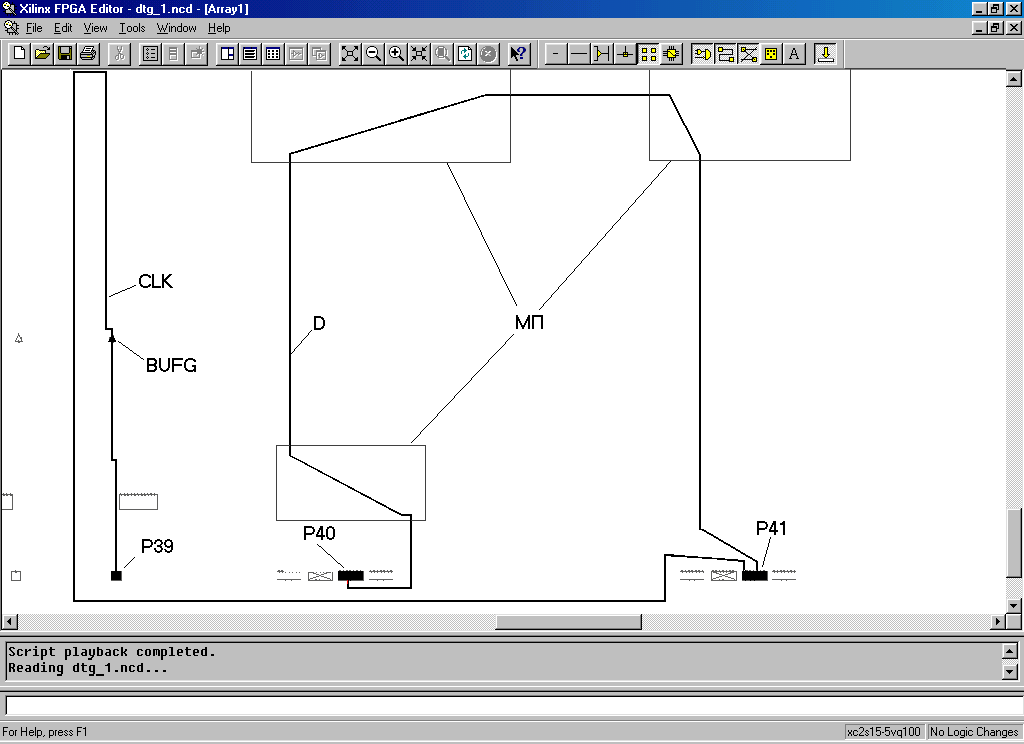

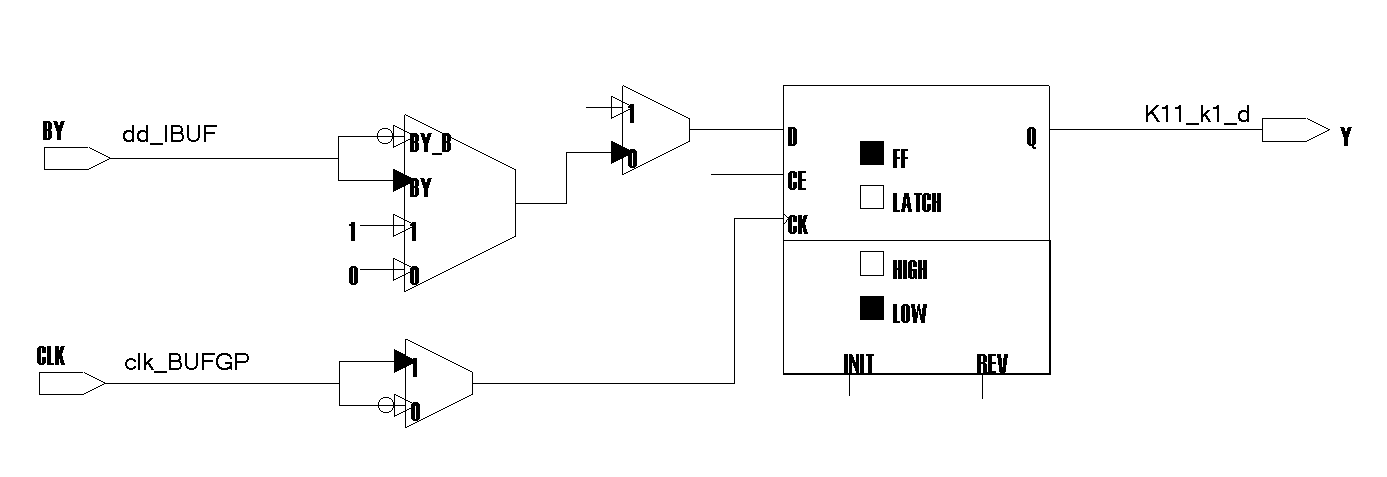

На рис. 2.14 показан пример размещения D –триггера в ПЛИС типа FPGA. На этом рисунке показаны связи D и CLK, выходная связь Q реализована внутри буфера ввода вывода P41. Синхросигнал CLK поступает на контакт P39, а затем через специализированный буфер BUFG поступает на внутренние узлы схемы. На рисунке показаны также матрицы переключений МП.

Рис. 2.14. Размещение схемы в ПЛИС типа FPGA

5. Разработка регистровой схемы

Рассмотрим разработку четырехразрядного сдвигающего регистра, обеспечивающего преобразование последовательного кода в параллельный и имеющего информационный вход DIN, вход синхронизации CLK и выход DOUT[3/0]. Ввод проекта и описание схемы на языке VHDL производится в соответствии с правилами, описанными в разделе 2.2. Тип микросхемы - ПЛИС типа FPGA xc2s15-vq100-5. Описание интерфейса данной схемы будет выглядеть следующим образом.

Рис. 2.15. Задание интерфейса разрабатываемой схемы

В качестве шаблона можно использовать пункт Serial to Parallel Shift Register из группы сдвигающих регистров Shift Registers. Окончательный вид описания регистра будет следующим:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity rg is

Port ( DIN : in std_logic;

CLK : in std_logic;

DOUT : out std_logic_vector(3 downto 0));

end rg;

architecture Behavioral of rg is

signal REG: STD_LOGIC_VECTOR(3 downto 0);

begin

process (CLK)

begin

if CLK'event and CLK='1' then

REG(3 downto 0) <= DIN & REG(3 downto 1);

end if;

DOUT <= REG;

end process;

end Behavioral;

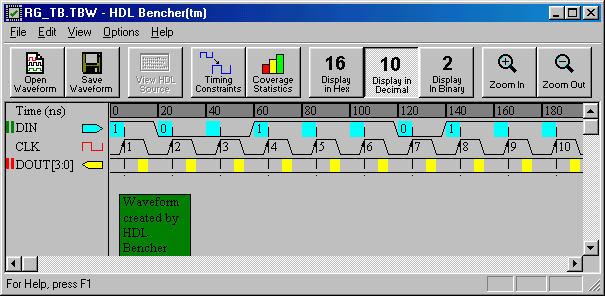

Внешние сигналы с помощью редактора ограничений задаются на следующие контакты: din - P40, clk - P39, dout[3/0] - P41, P43, P4, P45. Для моделирования с помощью программы Test Behcher задаются временные диаграммы сигналов din и clk, которые показаны на рис. 2.16.

Рис. 2.16. Входные сигналы

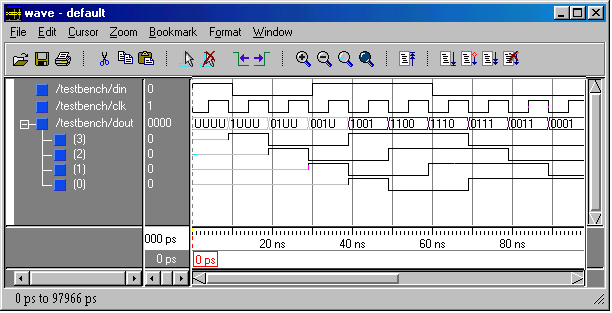

На этих временных диаграммах заданы следующие параметры: длительности единичного и нулевого значения синхросигнала – по 10 нс, время установки входных воздействий перед фронтом тактового сигнала и время задержки выходных значений по 6 нс. Моделирование производится на основе данных сигналов с применением программы ModelSim. Результаты функционального моделирования показаны на рис. 2.17.

Рис. 2.17. Результаты моделирования

В отчете о размещении схемы показано, что для реализации схемы используются 4 триггера в двух секциях, что отражено следующими строками:

Number of SLICEs 2 out of 192 1%

Number of Slice Flip Flops: 4 out of 384 1%.

Для реализации внешних связей требуется 5 обычных блоков ввода-вывода и один специализированный для синхросигнала с использованием глобального буфера GCLK:

Number of External IOBs 5 out of 60 8%

Number of External GCLKIOBs 1 out of 4 25%

Number of GCLKs 1 out of 4 25%

Распределение внешних сигналов по контактам, полностью совпадающее с заданным выше, отражается следующим фрагментом:

Resolved that GCLKIOB <clk> must be placed at site P39.

Resolved that IOB <din> must be placed at site P40.

Resolved that IOB <dout<0>> must be placed at site P41.

Resolved that IOB <dout<1>> must be placed at site P43.

Resolved that IOB <dout<2>> must be placed at site P44.

Resolved that IOB <dout<3>> must be placed at site P45.

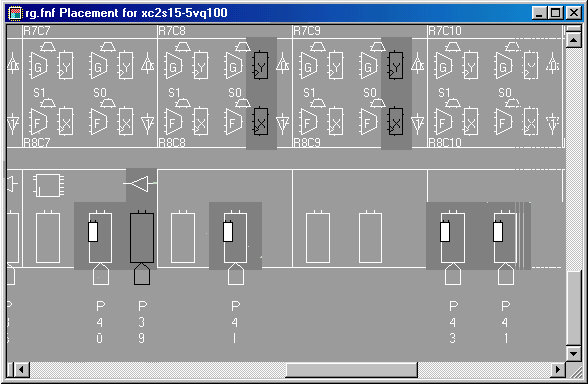

На рис. 2.18 приведен фрагмент ПЛИС, полученный с помощью программы FloorPlanner. Из этого рисунка видно, что для проектируемой схемы системой САПР ISE отведены 2 секции в блоках ПЛБ, расположенных по адресам R8C8 и R8C9. Данные секции выделены темным цветом.

Рис. 2.18. Размещение узлов схемы в ПЛИС

Информация о величине задержек схемы отражена в следующих строках:

The Average Connection Delay for this design is: 0.853 ns

The Maximum Pin Delay is: 1.564 ns

The Average Connection Delay on the 10 Worst Nets is:) 0.637ns

Listing Pin Delays by value: (ns)

d<1.00 <d< 2.00 <d< 3.00 <d< 4.00 <d< 5.00 d>= 5.00

8 4 0 0 0 0

Полная информация о задержках приведена в таблице:

-------------------------------

| Max Delay (ns) | Netname |

-------------------------------

1.564 reg_3_1

1.540 reg_2

1.209 reg_0

1.202 reg_1

0.853 reg_3

0.721 din_IBUF

0.469 clk_BUFGP

0.007 clk_BUFGP/IBUFG

---------------------------------

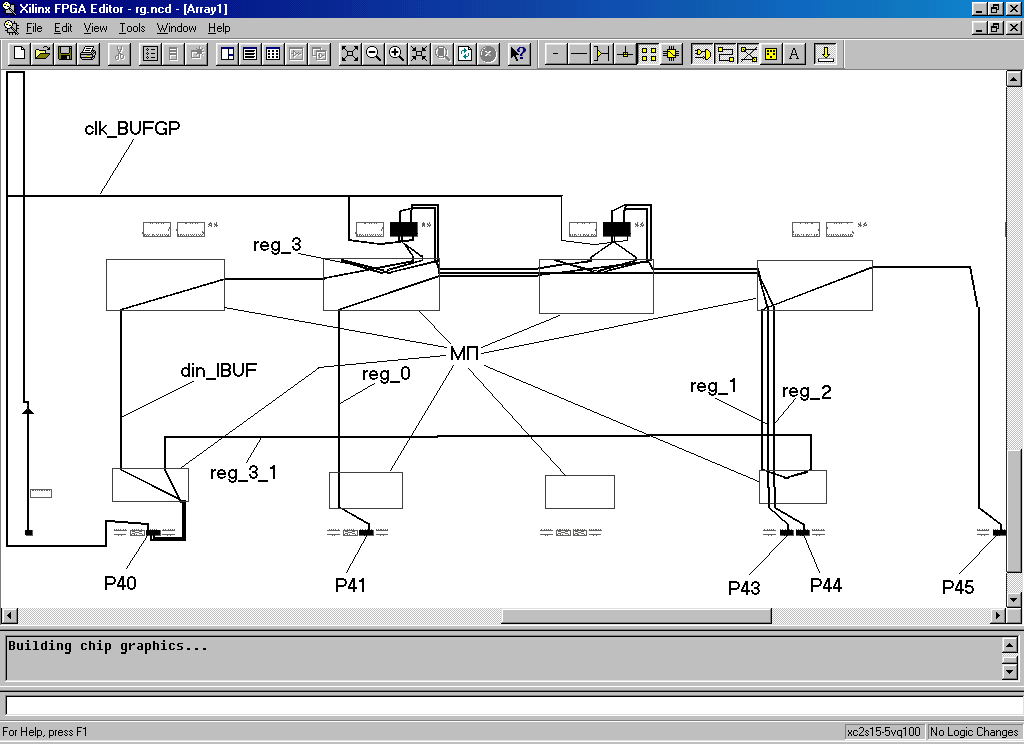

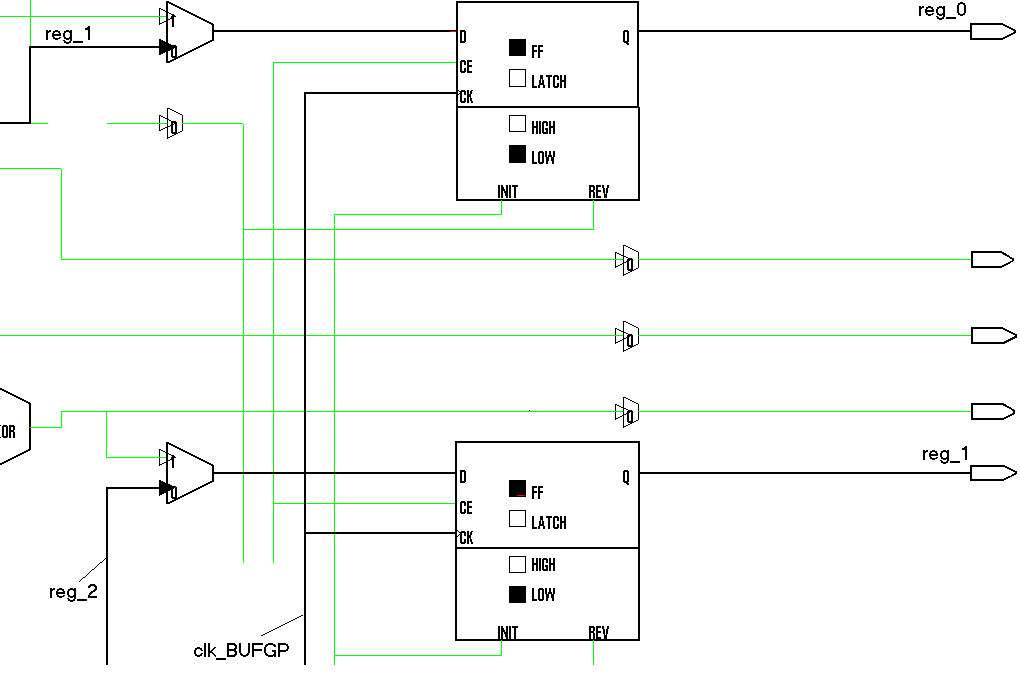

На рис. 19 показан фрагмент ПЛИС, на котором размещена проектируемая схема. Данный рисунок получен с помощью программы редактора FPGA (FPGA Editor).

Рис. 2.19. Окончательное размещение узлов и связей

На этом рисунке приведены контакты P40, P41, P43, P44 и P45, которые соответствуют входному сигналу DIN и выходным сигналам DOUT[0], DOUT[1], DOUT[2] и DOUT[3]. На рисунке показаны также внутренние сигналы reg_0, reg_1, reg_2 и reg_3. Название последних присвоила сама система, и их имена соответствуют индексам сигналов DOUT[0] … DOUT[3]. В схеме продублирован внутренний сигнал reg_3, его аналог имеет наименование reg_3_1 и используется для формирования сигнала DOUT[3] на контакте P45, сам сигнал reg_3 используется для формирования сигнала reg_2 при сдвиге. Указанное дублирование вызвано тем, что в системе задан режим оптимизации по быстродействию, и система обеспечивает максимальное быстродействие, пусть и за счет усложнения схемы.

Фрагмент секции CLB_R8C8.S0, где формируются два младших разряда, показан на рис. 2.20.

Рис. 2.20. Блок ввода-вывода

На рис. 2.21 показан фрагмент блока ввода-вывода (IOB) P40, который обеспечивает прохождение входного сигнала DIN. Сигнал поступает на входной контакт PAD, затем проходит через ряд буферных схем. Во внутреннюю логику ПЛИС поступает сигнал din_IBUF, а также сигнал reg_3_1, который вырабатывается на выходе D –триггера, находящегося в блоке ввода-вывода.

Рис. 2.21. Программируемый логический блок

Таким образом, разработчику достаточно ввести описание схемы на языке VHDL, а все остальное выполняет система проектирования.

6. Разработка умножителя

Пусть требуется разработать комбинационный умножитель 16х16 разрядов. Выходной код в этом случае должен иметь 32 разряда. Необходимо отметить, что в ряде современных семейств ПЛИС имеются встроенные умножители, однако в настоящем разделе используется ПЛИС типа FPGA XC2S15-VQ100, в которой таких блоков нет.

Описание умножителя на языке VHDL имеет следующий вид:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity mult is

Port ( a : in std_logic_vector(7 downto 0);

b : in std_logic_vector(7 downto 0);

c : out std_logic_vector(15 downto 0));

end mult;

architecture Behavioral of mult is

signal d: std_logic_vector (15 downto 0);

begin

d <= a*b;

c <= d;

end Behavioral;

Схема занимает 32 блока ввода-вывода и 36 секций для реализации логических функций. Об этом свидетельствуют строки из отчета о размещении и трассировке:

Number of External IOBs 32 out of 60 53%

Number of SLICEs 36 out of 192 18%.

Распределение длительностей связей будет выглядеть следующим образом:

d<1.00 <d<2.00 <d<3.00 <d<4.00 <d<5.00 d>=5.00

65 137 27 5 0 0.

Распределение сигналов по контактам:

Signal Name | Pin |Signal Name | Pin |Signal Name | Pin |

a<0> | P20 | a<1> | P19 | a<2> | P10 |

a<3> | P8 | a<4> | P9 | a<5> | P5 |

a<6> | P4 | a<7> | P98 |

b<0> | P22 | b<1> | P97 | b<2> | P21 |

b<3> | P6 | b<4> | P31 | b<5> | P71 |

b<6> | P72 | b<7> | P93 |

c<0> | P30 | c<1> | P18 | c<2> | P17 |

c<3> | P16 | c<4> | P59 | c<5> | P32 |

c<6> | P60 | c<7> | P62 | c<8> | P65 |

c<9> | P66 | c<10> | P69 | c<11> | P7 |

c<12> | P95 | c<13> | P96 | c<14> | P15 |

c<15> | P13

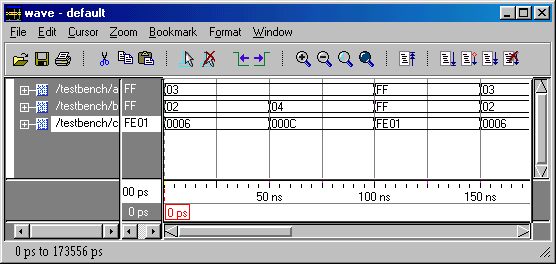

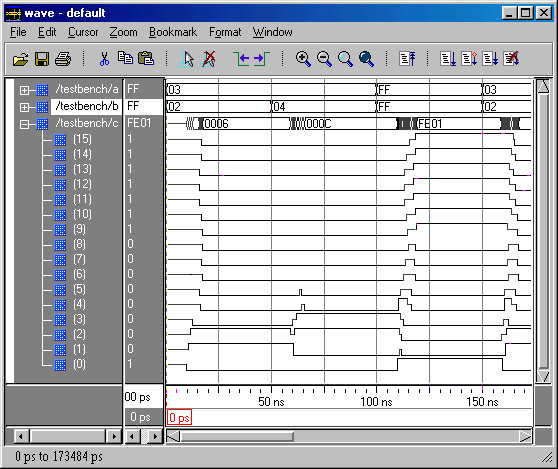

На рис. 2.22 показаны результаты функционального моделирования (рис. 2.22 а) и временного моделирования (рис. 2.22 б), полученного после реализации схемы.

а

б)

Рис. 2.22. Результаты моделирования

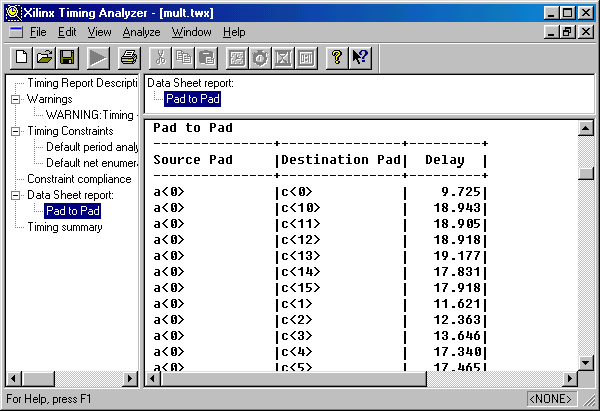

Разработанный умножитель является комбинационной схемой, поэтому для разработчика в данном случае представляют интерес задержки распространения сигнала от входа до выхода (Pad to Pad). Удобным средством для получения этих данных является программа временного анализатора Timing Analyzer, который позволяет получить самую разнообразную информацию о задержках. На рис. 2.23 показано окно анализатора Timing Analyzer, в котором приведен фрагмент отчета о задержках от входа до выхода (Pad to Pad).

Рис. 2.23.

Ниже приведены максимальные задержки от входа до выхода.

---------------+---------------+---------+

Source Pad |Destination Pad| Delay |

---------------+---------------+---------+

a<0> |c<13> | 19.177|

a<5> |c<13> | 19.110|

b<0> |c<13> | 19.033|

b<5> |c<10> | 19.149|

b<5> |c<11> | 19.109|

b<5> |c<12> | 19.122|

b<5> |c<13> | 19.381|

---------------+---------------+---------+

Еще одним способом задания нужных временных параметров типа Pad to Pad является задание временных ограничений с помощью программы редактора ограничений (Constraints Edior). Окно этой программы приведено на рис. 2.5, временные ограничения типа Pad to Pad задаются на вкладке Global. Например, для данной схемы может быть задано максимальное значение задержки величиной 20 нс. В файле ограничений пользователя это будет задано строкой:

TIMESPEC "TS_P2P" = FROM "PADS" TO "PADS" 20 ns.

Если система САПР не сможет обеспечить требуемое быстродействие, то об этом будет сообщено разработчику, и он должен предпринять соответствующие меры, например, взять микросхему с более высоким быстродействием.

7. Использование структурного описания

Рассмотрим особенности реализации в САПР ISE схем, заданных описанием типа Structura. Пусть требуется разработать цифровую задержку на четыре такта. Самый верхний уровень описания RG2 содержит два последовательно соединенных блока типа RG с именами K11 и K12, каждый из которых представляет собой задержку на два такта. Вход схемы имеет имя DD, выход – rr. Описание схемы имеет следующий вид.

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity rg2 is

Port (DD, CLK: in std_logic; RR : out std_logic);

end rg2;

architecture Structura of rg2 is

component rg port (D0, CLK: in std_logic; R : out

std_logic);

end component;

signal S11, S22 : std_logic;

begin

K11: rg port map (DD, CLK, S11);

K12: rg port map (S11, CLK, S22);

RR <= S22;

end Structura;

Каждый из блоков RG в свою очередь содержит два D триггера типа DTG, описание блока RG имеет следующий вид.

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity rg is

Port ( D0, CLK : in std_logic;

R : out std_logic);

end rg;

architecture Structura of rg is

component dtg port ( D, CLK : in std_logic;

Q : out std_logic);

end component;

signal S1, S2 : std_logic;

begin

K1: dtg port map (D0, CLK, S1);

K2: dtg port map (S1, CLK, S2);

R <= S2;

end Structura;

Описание D триггера, входящего в состав блока RG, имеет следующий вид.

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity dtg is

Port ( D, CLK : in std_logic;

Q : out std_logic);

end dtg;

architecture Behavioral of dtg is

begin

process (CLK)

begin

if CLK'event and CLK='1' then --CLK rising edge

Q <= D;

end if;

end process;

end Behavioral;

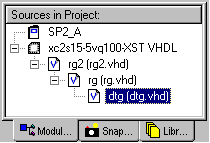

Структура проекта будет отражена в окне исходных модулей следующим образом (см. рис. 2.23).

Рис. 2.23. Структура проекта

Если представить разрабатываемое устройство в виде традиционной схемы, то она будет иметь следующий вид (см. рис. 2.24).

Рис. 2.24. Схема устройства

Каждый из блоков RG с именами K11 и K12 имеет в своем составе узлы K1 и K2. Входная связь DD в блоке K11 называется D0, связь с именем S11 между блоками K11 и K12 в блоке K11 называется S2, в блоке K12 - D0. Выходная связь устройства RR в блоке K12 имеет название S2. Связи внутри блоков между узлами K1 и K2 называются S1.

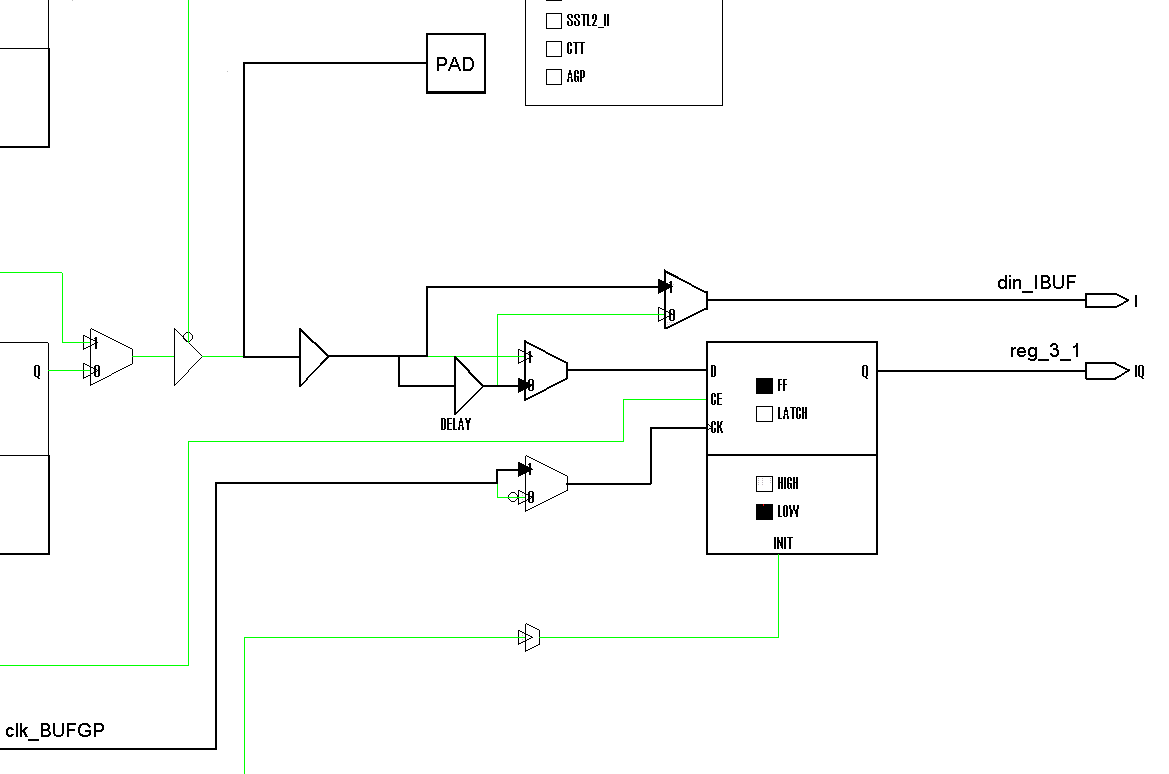

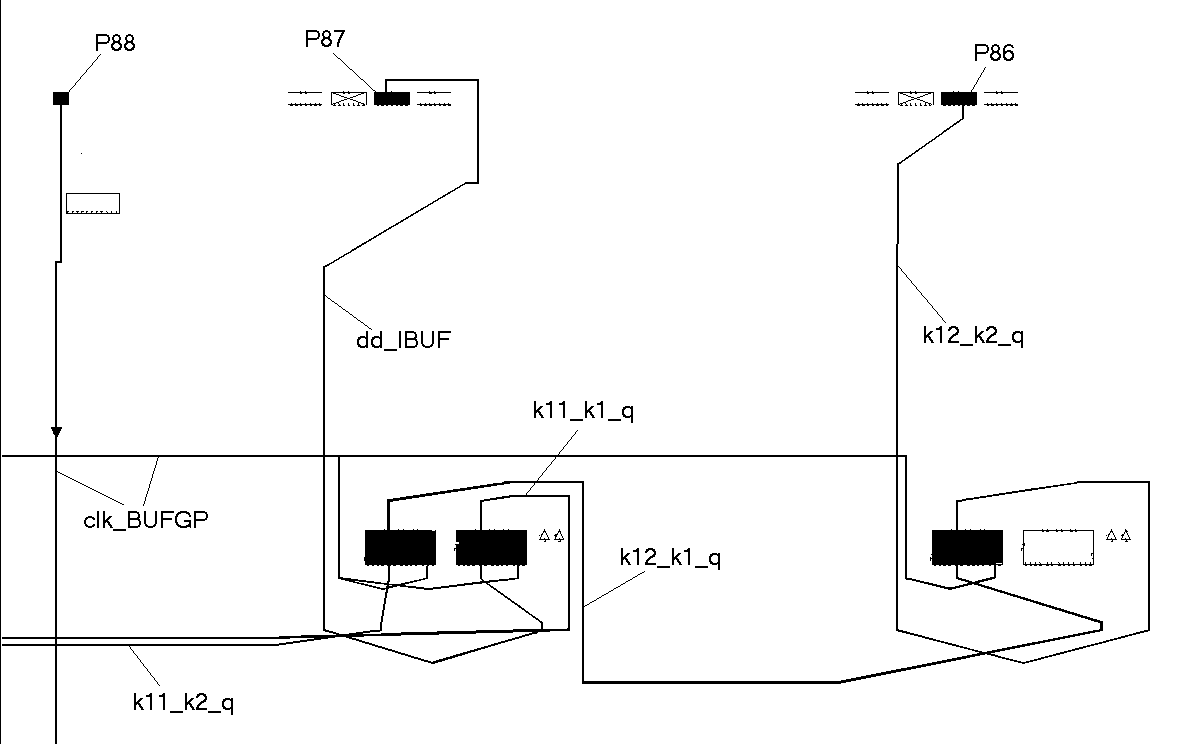

На рис. 2.25 показан результат размещения схемы в ПЛИС xc2s15 vq100, полученной c помощью программы FPGA Editor.

Рис. 2.25. Размещение схемы в ПЛИС

На рис. 2.25 показаны контакты P88 (вход синхросигнала CLK), P87 (вход схемы) и P86 (выход схемы). Там же показаны некоторые из связей, в том числе связь clk_BUFGP (синхросигнал на выходе глобального буфера), dd_IBUF (входной сигнал на выходе буфера IBUF) и другие. Наименование внутренних информационных связей система ISE составляет из имен компонентов, начиная с верхнего уровня. Так, например, связь k11_k2_q – это связь S1 в блоке K11 (см. рис. 2.24), в нем в свою очередь в блоке K1, а в этом блоке – выход триггера q. Связь k12_k2_q – это выходная связь S2 в блоке K12, а далее в блоке K2. Именно эта связь является выходной и поступает на контакт ПЛИС P86.

На рис. 2.26 показан фрагмент логической ячейки, в которой реализован элемент K1, который включен в состав элемента K12 (см. рис. 2.24). На выходе этой ячейки формируется связь k11_k2_q, которая упоминалась в предыдущем абзаце.

Рис. 2.26 Фрагмент логической ячейки.

На входы этой ячейки поступает сигнал синхронизации clk_BUFGP, который тактирует работу всей схемы, а также входной сигнал dd_IBUF.

Литература

1. Бибило П.Н. Синтез логических схем с использованием языка VHDL. М.: Солон-Р, 2002.

2. Суворова Е. А., Шейнин Ю. Е. Проектирование цифровых систем на VHDL. - СПб.: БХВ-Петербург. 2003.

3. Зотов В. Ю. Проектирование цифровых устройств на основе ПЛИС фирмы XILINX в САПР WebPACK ISE. - М.: Горячая линия-Телеком. 2003.

4. Стешенко В. Б. ПЛИС фирмы ALTERA: проектирование устройств обработки сигналов. - М.: ДОДЭКА. 2000.

5. Кнышев Д. А., Кузелин М. О. ПЛИС фирмы XILINX: описание структуры основных семейств. - М.: ДОДЭКА. 2001.

6. Угрюмов Е. П. Цифровая схемотехника. - СПб.: БХВ-Петербург. 2001.

7. Гурин Е. И. Программируемые логические интегральные схемы. - Пенза: Изд-во ПГУ. 2003.

8. Бродин В., Калинин А. Учебные классы микропроцессорной техники и ПЛИС. // Chep News. - 2000. - .№ 10.