Разработка блока динамического ОЗУ с мультиплексором кода адреса

ХТКЭМ

Курсовой проект.

Тема:

Разработка блока динамического ОЗУ с мультиплексором кода адреса.

Выполнил Ерохин В.А.

Проверил Калинкина М.В.

2000г.

ХИМКИНСКИЙ ТЕХНИКУМ КОСМИЧЕСКОГО ЭНЕРГОМАШИНОСТРОЕНИЯ

ЗАДАНИЕ

ДЛЯ КУРСОВОГО ПРОЕКТИРОВАНИЯ ПО КУРСУ________________________________

_ ___3________КУРСА____Э-32

97__ГРУППЫ

УЧАЩЕГОСЯ__Ерохина_________

___3________КУРСА____Э-32

97__ГРУППЫ

УЧАЩЕГОСЯ__Ерохина_________

Владимира Александровича

(фамилия, имя и отчество)

тема ЗАДАНИЯ И ИСХОДНЫЕ ДАННЫЕ_Разработка блок динамического ОЗУ с мультиплексором кода адреса емкостью 16К байт для 8-разрядных микропроцессорных устройств

При выполнении курсового проекта на указанную тему должны быть представлены:

1 .Пояснительная записка

______________________________________________________________________________________________________________________

2.Графическая часть проекта

ЛИСТ 1.________________________________________________________________________

2._________________________________________________________________

2._________________________________________________________________

Дата выдачи ____________________________

Срок окончания ____________

Преподаватель-руководитель курсового проектирования .

Введение.

ОЗУ выполняют запись, хранение и считывание произвольной двоичной информации. Оно является основным устройством памяти цифровых систем, в котором хранятся программы, определяющие процесс текущей обработки информации и массив обрабатываемых данных. Современные цифровые системы ОЗУ строятся из специальных микросхем памяти, которые объединяются в соответствующий функциональный блок.

Целью курсового проекта является разработка блока динамического ОЗУ емкостью 16Кбайт для 8-разрядных микропроцессорных устройств и закрепление полученных в процессе изучения дисциплины ЭВМ системы, комплексы и сети знаний по динамической памяти.

1.Организация работы блока динамического ОЗУ с мультиплексором кода адреса.

Для реалезации усройства необходимы: накопитель информации, состоящий из микросхем памяти (модуль памяти), и схемы управления.

Структурная схема такого блока показана в приложении 4.

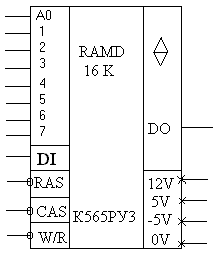

Модуль памяти, обозначаемый как DD1-DD8 на функциональной схеме (приложение 5), построен на микросхемах К565РУ3Г путем соединения их одноименных выводов, кроме информационных. Сигналы RAS и CAS формирует контроллер ОЗУ CLC. , сигнал MWTC с шины управления подан на вход W/R. Для снижения степени рассогласования с ТТЛ управляющими элементами целесообразно подключение всех адресных и управляющих линий ко входам микросхем памяти осуществлять через резисторы с сопративлением 20-30 Ом.

Буфер выходных данных DD13 реализован на парралельном 8-разрядном регистре КР580ИР82. Сигнал управления регистром вырабатывает контроллер ОЗУ. Сигнал ОЕ управляет выходами: при 0 они открыты для считывания, при 1-переходят в третье состояние, сигнал СЕ управляет входами: при 1 они открыты для записи, при 0 блокированы.

В блоке ОЗУ буферизованы только его выходные линии.

Мультиплексор DD9-DD12 выполненный на схемах К555КП2 обеспечивает последовательный во времени ввод адресного кода строк AX {AO-A7} и столбцов AY {A8-A15} в модуль ОЗУ.

Адресные сигналы поступают на входы D0.0, D1.0 и D0.1, D1.1 мультиплексорных микросхем и коммутируются на выхды под управлением сигнала на входе SED2(AY/AX) при наличии на другом управляющем входе SED1(REF) уровня 0. Условия коммутации сигналов: при AY/AX=0 к выходам подключаются каналы D0.0, D0.1 и, следовательно, на адресные входы ОЗУ поступает адрес строк AX; при AY/AX=1 к выходам подключаются каналы D1.0, D1.1 и к ОЗУ направляется код адреса столбцов AY.

Сигналы управления: REF- признак режима регенерации и AY/AX-сигнал мультиплексирования каналов, вырабатывает контроллер.

В режиме регенерации REF=1 и мультиплексор коммутирует на выходы при изменении AY/AX каналы D2.0, D3.0 и D2.1, D3.1. Но так как указанные каналы попарно соединены, то на результат коммутации сигнал AY/AX влияния не оказывает: при любых его значениях на выходы мультиплексора поступают адреса регенерации AR, вырабатываемые счетчиком контроллера. Эти сигналы адресуют только строки, сигналы адреса столбцов в этом режиме на адресных входах отсутствуют.

При отсутствии обращения к ОЗУ, ОЗУ работает только в режиме регенерации. С каждым тактом контроллер формирует сигналы RAS, REF и код адреса очередной строки, и инициирует работу модуля памяти по циклу регенерации.

Процесс регенерации прекращается при обращении микропроцессора к ОЗУ, и контроллер обрабатывает требование микропроцессора. В конце цикла обращения контроллер переводит блок ОЗУ в режим регенерации, продолжая этот процесс с адреса, на котором он был прерван.

Регенерация, осуществляемая по описанному алгоритму называется “ прозрачной”: она незаметна для микропроцессора и не снижает скорость обработки программ. Условием для применения этого способа является наличие временных интервалов между двумя любыми обращениями микропроцессора к ОЗУ, достаточных для проведения одного цикла регенерации, т.е. регенерации при обращении к модулю ОЗУ по одному адресу.

Например, алгоритмом работы микропроцессора К580ВМ80 такие интервалы предусмотрены: минимальный цикл между двумя любыми обращениями к памяти состоит из трех тактовых периодов.

При номинальной частоте генератора 18МГц длительность такта равна 0.5 мкс. Если учесть, что на выполнение одного цикла регенерации микросхем К565РУ3Г требуется 370 нс, то очевидна возможность реализации.

2.1.Принцип работы микросхемы динамических ОЗУ К565РУ3Г

В микросхемах памяти динамического типа функции ЭП выполняет электрический конденсатор, образованный внутри МДП структуры. Информация представляется в виде заряда: наличие заряда на конденсаторе соответствует логической 1, отсутствие-логическому 0. Поскольку время сохранения конденсатором заряда ограничено, предусматривают периодическое восстановление (регенерацию) записанной информации. Кроме того, для них необходима синхронизация, обеспечивающая требуемую последовательность включений и выключений функциональных узлов.

Для изготовления микросхем динамического ОЗУ в основном применяют n-МДП технологию, которая позволяет повышать быстродействие и уровень интеграции микросхем, обеспечивать малые токи утечки и за этот счет увеличивать время сохранения заряда на запоминающем конденсаторе.

- в

ыход

на три состояния;

ыход

на три состояния;

DI- входные данные; W/R- запись-считывание;

DO- выходные данные; A- адрес;

RAS- строб адреса строки;

CAS- строб адреса столбца;

Микросхема К565РУ3Г информационной емкостью 16Кx1бит. В ее структурную схему (приложение 1) входят выполненные в одном кремниевом кристалле матрица накопителя, содержащая 16384 элементов памяти, расположенных на пересечениях 128 строк и 128 столбцов, 128 усилителей считывания и регенерации, дешифраторы строк и столбцов, устройство управления, устройство ввода-вывода и мультиплексный регистр адреса.

Матрица накопителя разделена на две части по 64x64 ЭП в каждой. Между ними размещены усилители, так что каждый столбец состоит из двух секций, подключенных к разным плечам усилителя (приложение 2).

Элемент памяти собран по одно-транзисторной схеме и включает конденсатор Cij. Транзистор выполняет функции ключа: при сигнале на адресной шине строки Xi=1 он открывается и соединяет конденсатор Cij с j-разрядной шиной. Предварительно в паузах между обращениями к накопителю емкости полушин США и СШБ заряжает источник напряжения UO через открытые ключевые транзисторы VT5 и VT6. При обращении к накопителю эти транзисторы закрываются и изолируют полушины Aj и Bj от источника напряжения UО

Запоминающий конденсатор Сij выбранного ЭП подключается через открытый транзистор Vtij к полушине Aj и изменяет ее потенциал. Это изменение незначительнo, тк емкость запоминающего конденсатора равная 01-02 пФ много меньше емкости шины Поэтому для индикации малого изменения потенциала шины при считывании информации применен высоко чувствительный дифференциальный усилитель тригерного типа на транзисторах VT1-VT4 включенный в середину РШ

Кроме массива ЭП и усилителей матрица имеет в своей структуре опорные элементы (ЭО) по одному елементу в каждой полушине Эти элементы вкаждой половине матрицы состовляют опорную строку (ОС)

Опорный элемент построен аналогично запоминающему Его назначение состоит в поддержании опорного напряжения UO c которым усилитель сравнивает потенциал полушины с выбранным ЭП и реагирует на получающуюся при сравнении разность

потенциалов положительного и отрицательного знака в зависимости от считываемого уровня

Эта операция происходит следующем образом: если выбрана для обращения строка верхней полуматрицы Xi то сигнал А6 старшего разряда кода адреса строки коммутирует в селекторе опорной строки цепь через ключевой транзистор VT12 для сигнала F2 к ОС2 расположенной в нижней полуматрице Таким образом в каждом из 128 столбцов к усилителю с разных сторон подключены ЭП и ЭО Поскольку потенциал полушины с ЭП отличается от опорного в проводимости транзисторов разных плеч усилителя-триггера появляется асимметрия которая при включении цепи его питания сигналом F3 вызывает опрогидование триггера по преобладающему уровню В итоге на выходах-входах А и В триггера формируются полные уровни 1 и 0 Тот из сигналов который отражает считываемую информацию в данном примере сигнал с плеча А коммутируется на вход устройства вывода через ключевые транзисторы VT7VT9 и VT10 открываемые сигналами А6 F4 и Yj Очевидно считан может быть только один сигнал с выбранного дешифратором столбца : Yj=1 У остальных столбцов ключи VT10 закрыты Сигнал F4 зависит от наличия сигнала CAS: при отсутствии последнего он не формируется и ключ VT9 закрыт

Сигнал на входе-выходе А триггера-усилителя выполняет также функцию восстановления уровня заряда запоминающего конденсатора Cij , т.е. функцию регенерации информации. Причем эта операция происходит во всех ЭП выбранной строки одновременно.

Таким образом, при каждом обращении к матрице для считывания информации автоматически осуществляется регенерация информации во всех ЭП, принадлежащих выбранной строке.

Для адресации 16 К элементов памяти необходим 16-разрядный код, а у микросхемы только восемь адресных входов. С целью уменьшения числа необходимых выводов корпуса в микросхемах динамического ОЗУ код адреса вводят по частям: вначале семь младших разрядов АО-А7, сопровождая их стробирующим сигналом RAS, затем семь старших разрядов А8-А15 со стробирующим сигналом CAS. Внутри микросхемы коды адреса строк и столбцов

фиксируются на адресном регистре, затем дешифруются и осуществляют выборку адресуемого ЭП.

Таблица истинности микросхемы К565РУ3Г

RAS |

CAS |

W/R |

A |

DI |

DO |

Режим работы |

|

1 1 0 0 0 0 |

1 0 1 0 0 0 |

Х Х Х 0 0 1 |

Х Х А А А А |

Х Х Х 0 1 Х |

Z Z Z Z Z D |

Хранение Хранение Регенерация Запись 0 Запись 1 Считывание |

Для формирования внутренних сигналов F1-F4, управляющих включением и выключением в определенной последовательности функциональных узлов микросхемы, в ее структуре предусмотрено устройство управления, для которого входными являются сигналы RAS,CAS,W/R.

Устройство ввода-вывода обеспечивает ввод одного бита информации DO в режиме считывания и ввод одного бита информации DI с ее фиксацией с помощью триггера-защелки в режиме записи. Во всех режимах, кроме режима считывания выход принимает высокоомное (третье) состояние. Наличие у выхода высокоомного состояния позволяет объединять информационные вход и выход при подключении микросхемы к общей информационной шине.

По входам и выходу микросхема К565РУ3Г совместима с ТТЛ микросхемами, что означает соответствие их входных и выходных сигналов ТТЛ уровням.

Микросхемы динамических ОЗУ работают в следующих режимах: записи, считывания, считывания-модификация-записи, страничной записи, страничного считывания, регенерации.

Для обращения к микросхеме для записи и считывания информации необходимо подать (приложение 3 а) код адреса строк А0-А7 одновременно с ним или с некотой (не рекомендуется)

задержкой сигнал RAS, затем с нормированной задержкой на время удержания адреса строк относительно сигнала RAS должен быть подан код адреса столбцов и через время и через время установления tус а CAS-сигнал CAS.

К моменту подачи кода адреса столбцов на вход DI подводят записываемый бит информации, который сигналом W/R при наличии CAS=0 фиксируется на входном триггере-защелке. Сигнал записи W/R может быть подан уровнем или импульсом. В последнем случае он должен иметь длительность не менее определенного параметром WR значения. Если сигнал записи подан уровнем, то фиксацию DI триггером-защелкой производит отрицательный перепад сигнала CAS (при наличии RAS=0). По окончании записи должна быть выдержана пауза RAS, равная интервалу между сигналами RAS, для восстановления состояния внутренних цепей микросхемы.

В аналогичном порядке должны быть поданы адресные и управляющие сигналы при считывании информации (приложение 3 б). Сигнал W/R=1 может быть подан импульсом или уровнем. Время появления выходного сигнала можно отсчитывать от момента поступления сигналов адреса tва либо сигналов управления, время выборки сигнала RAS t В RAS , время выборки сигнала CAS t В CAS. Более информативным является параметр t В CAS , т.к. информацию выводит из микросхемы сигнал CAS при наличии сигнала W/R=1.

Из приложения 5 б следует: t В RAS=t В CAS+t УС RAS CAS.

Для оценки быстродействия микросхемы памяти в расчет принимают время цикла записи (считывания) t Ц ЗП, t Ц СЧ. Другие временные параметры необходимы для обеспечения бессбойного функционирования микросхем в составе эл. аппаратуры.

Динамические параметры микросхемы К565РУ3Г (нс)

|

t Ц ЗП (СЧ) |

370 |

t УС CAS RAS |

65 |

CAS ** |

80 |

|

t Ц СЧ-М-ЗП * |

420 |

t У А RAS |

25 |

В CAS |

135 |

|

t Ц ЗП (СЧ) ** |

225 |

t УС CAS A |

10 |

T РЕГ , мс |

2 |

|

RAS |

200 |

t У А CAS |

55 |

||

|

RAS |

120 |

WR |

55 |

||

|

CAS |

135 |

t У DI CAS |

55 |

*Время цикла в режиме (считывание-модификация-запись) ** В страничном режиме

Для обеспечения надежного сохранения записанной в накопителе информации реализуют режим принудительной регенерации. Регенерация информации в каждом ЭП должна осуществляться не реже чем через 2 мс.

Время, в течении которого необходимо обратиться к строке для регенерации, определяет параметр “Период регенерации” Трег.

Поскольку обращение к разным строкам происходит с различными по длительности интервалами времени, расчитывать только на автоматическую регенерацию нельзя.

Цикл регенерации состоит из m обращений к матрице, где m-число строк, путем перебора адресов строк с помощью внешнего счетчика циклов обращений. Обращение к матрице для регенерации может быть организовано по любому из режимов: записи, считывания, считывания-модификации-записи, а также по специальному режиму регенерации- сигналом RAS.

Режим работы “Считывание-модификация-запись” заключается в считывании информации с последующей записью в один и тот же ЭП. Во временных диаграммах сигналов для этого режима совмещены диаграммы для считывания (приложение 3 б) и записи (приложение 3 а) информации: при неизмененных сигналах RAS и CAS режим считывания сменяет режим записи данных по тому же адресу. Модификация режима заключается в смене сигнала считывания на сигнал записи и в подведении ко входу DI записываемой информации. Время цикла в этом режиме обращения больше чем в других.

При организации принудительной регенерации является режим регенерации сигналом RAS (приложение 3 в), при котором осуществляют перебор адресов в сопровождении стробирующего сигнала RAS при CAS=1.

В расчет времени регенерации следует принимать время цикла при выбранном режиме регенерации, умножив его на число строк. На регенерацию информации в ЭП одной строки у микросхемы К565РУ3Г в режиме “Считывание-модификация-запись” необходимо 420 нс, тогда для регенерации ЭП всех 128 строк потребуется 54 мкс, что составит 2.7% рабочего времени микросхемы. В режиме регенерации только сигналом RAS общее

время регенерации уменьшается до 47.4 мкс что состави 2.3% времени функционирования микросхемы.

m-число

строк

m-число

строк

tЗАН-время занятости

Страничные режимы записи и считывания реализуют обращением к микросхеме по адресу строки с выборкой ЭП этой строки изменение адреса стлбцов. В этих режимах значительно уменьшается время цикла записи (считывания) поскольку при неизменных сигналах RAS=0 и кода адреса строки использована часть полного цикла записи (считывания), относящаяся к адресации столбцов.

Микросхема К565РУ3Г нуждается в трех источниках питания и следует учитывать требования по порядку включения и выключения источников питания: первым включают источник –5В, а отключают последним. Это требование обусловлено тем, что напряжение –5В подается на подложку (кристалл) и если его не подключить первым, то воздействием, даже кратковременным, напряжений двух других источников с напряжением 5 и 12В может произойти в кристалле тепловой пробой. Порядок включения двух других напряжений питания может быть любым.

После подачи напряжения питания микросхема К565РУ3Г переходит в нормальный режим функционирования через восемь рабочих циклов.

2.2.Параметры микросхемы К565РУ3Г

Характеристика микросхемы К565РУ3Г

Емкость,бит -16К x 1

Время цикла записи считывания- 370нс

Напряжение питания- 5В,12В,-12В

Потребляемая мощность: в режиме хранения- 40 мВт

в режиме обращения- 460мВт

Тип корпуса- ДИП;16;7.5

Статические параметры микросхемы К565РУ3Г

I потребления динамический- 45мА I потребления статический- 4Ма

U вх низкого уровня мах 0.8B min –1B U вх высокого уровня вах 6В min 2.4B

U вых низкого уровня мах 0.4B

U вых высокого уровня min 2.4B

I вых низкого уровня мах 4мА

I вых высокого уровня мах 2мА

Выходной ток утечки мах 10мкА

Входной ток утечки мах 10мкА

Входная емкость по входам WR/RD, RAS, CAS мах 10пФ

по входам A, DI мах 6 пФ

Выходная емкость мах 10 пФ

Максимальная емкость нагрузки 100 пФ

2.3.Расчет нагрузочной способности микросхемы К565РУ3Г

Характерным для ДБИС ЗУ, изготовляемых по МДП-технологии, является высокое входное омическое сопротивление. При определении числа Q ДБИС ЗУ, нагружаемых на ТТЛ-схему, учитывается в основном емкость входов микросхемы памяти.

СМАХ- максимальная емкость нагрузки ТТЛ-схемы

СI- емкость входа ДБИС ЗУ

Т.к. для К555КП2 емкость СMAX≤150Пф, а для К565РУ3Г емкость СI≈ 6-10Пф, то Q≤15-25.

Выход К565РУ3Г имеет собственную емкость СВЫХ=10пФ и работает на емкостную нагрузку до 100пФ. Поэтому по входу можно объединить до 10 микросхем памяти.

3.1.Мультиплексоры блока динамического ОЗУ.

Мультиплексоры выполнены на схемах К555КП2.

Таблица истинности

|

Входы |

Выход |

||||||

|

E |

SED2 |

SED1 |

DO |

D1 |

D2 |

D3 |

D |

|

H |

X |

X |

X |

X |

X |

X |

L |

|

L |

L |

L |

L |

X |

X |

X |

L |

|

L |

L |

L |

H |

X |

X |

X |

H |

|

L |

L |

H |

X |

L |

X |

X |

L |

|

L |

L |

H |

X |

H |

X |

X |

H |

|

L |

H |

L |

X |

X |

L |

X |

L |

|

L |

H |

L |

X |

X |

H |

X |

H |

|

L |

L |

H |

X |

X |

X |

L |

L |

|

L |

L |

H |

X |

X |

X |

H |

H |

Назначение выводов ИС К555КП2

-

1

Вход выбора S1

EO

2

Вход адреса A1

SED2

3

Вход X1.4

D3.0

4

Вход X1.3

D2.0

5

Вход X1.2

D1.0

6

Вход X1.1

D0.0

7

Выход Y1

D.O

8

Общий

GND

9

Выход Y2

D.1

10

Вход X2.1

D0.1

11

Вход X2.2

D1.1

12

Вход X2.3

D2.1

13

Вход X2.4

D3.1

14

Вход адреса A0

SED1

15

Вход выбора S2

E.1

16

Питание

UCC

Условное графическое обозначение ИС КП555КП2 (рис а) и функциональная схема одного элемента (рис б).

(а)

(б)

3.2.Организация работы микросхемы К555КП2.

Мультиплексор К555КП2- это два мультиплексора 14 с общим дешефратором адреса канала и входами выбора (стробирующими входами) одного из мультиплексоров Е.0 и E.1.

Инверторы на входах Е.0 и Е.1 предназначены для развязки внутренних цепей от входных шин и обеспечивают помехоустойчивость схемы по входу.

Запрещена передача информации через мультиплексор, когда он находится в невыбранном состоянии (при этом выход находится в состоянии низкого уровня). Каждый из мультиплексоров имеет по четыре информационных входа и свои стробирующие входы Е.0 и Е1. Два аресных входа SED1 и SED2 управляют одновременно двумя мультиплексорами.

Код, который набран на адресных входах SED1 и SED2, разрешает работу только одного из информационных входов каждого мультиплексора. Сигнал с выбранного информационного входа появляется на выходе только при наличии на стробирующем входе Е низкого уровня.

Первая ступень мультиплексора выполнена на инверторах, вторая на логических элементах И-ИЛИ (без инверсии), использует стробирующие свойства функции И аргументов канала информации и адреса.

ИС К555КП2 включает входы управления с передачи при низком уровне напряжения на входе и с запретом передачи при высоком уровне напряжения на входе.

3.3.Характеристики микросхемы К555КП2

IВХ низкого уровня -0.4мА

IВХ высокого уровня 0.04мА

IВЫХ низкого уровня 4мА

IВЫХ высокого уровня -0.4 мА

UВХ МАХ 5.5В

UВХ MIN –0.4B

UВХ низкого уровня 0.4В

UВХ высокого уровня 2.5В

Нагрузочная способность 10

Время задержки распространения сигнала:

при включении 20нс (СН=15пФ)

при выключении 20нс (СН=15Пф)

Средний ток потребления не более 3мА

Помехоустойчивость 0.3B

Частота переключения не более 25МГц

UМАХ питания 5.5B

СН МАХ=150пФ

Диапазон рабочих температур -10 +70°С

4.1.Принцип работы микросхемы КР580ИР82.

КР580ИР82 представляет собой 8-разрядный буферный регистр, предназначенный для ввода и вывода информации со стробированием.

Микросхема имеет восемь триггеров D-типа и восемь выходных буферов, имеющих на выходе состояние “выключено”. Управление передачей информации осуществляется с помощью сигнала STB “строб”.

При поступлении на вход STB сигнала высокого уровня осуществляется нетактируемая передача информации от входа DI до выхода DO. При подаче на вход STB сигнала низкого уровня микросхема хранит информацию предыдущего такта; при подаче на вход STB положительного перепада импульса происходит “защелкивание” входной информации. Выходные буферы управляются сигналом ОЕ “разрешение выхода”. При поступлении на вход ОЕ сигнала высокого уровня выходные буферы переводятся в состояние “выключено”.

Функциональная схема микросхемы КР580ИР82.

Назначение выводов ИС КР580ИР82.

-

Номер вывода

Обозначение

Назначение

1-8

DI0-DI7

Входы регистра

9

OE

Разрешение выхода

10

GND

Общий

11

STB

Строб

19-12

D00-D07

Выходы регистра

20

UCC

Питание

Таблица истинности.

-

Вход ОЕ

Вход STB

Входы DI

Выходы DO

0

1

1

1

0

1

0

0

0

0

Х

D00

1

Х

Х

Z

DOO-состояние выхода в предыдущем такте.

Х-логический уровень на входе не влияет на состояние входа.

Z-состояние “выключено”.

4.2.Характеристики микросхемы КР580ИР82.

Число разрядов регистра 8

Ток потребления 160мА.

Входной ток низкого уровня ≤ -0.2мА.

Входной ток высокого уровня ≤50мкА.

Выходное напряжение низкого уровня ≤0.45В.

Выходное напряжение высокого уровня ≥2.4В.

Выходной ток низкого уровня в состоянии “выключено” ≤-50мА.

Выходной ток высокого уровня в состоянии “выключено” ≤50мА.

Время передачи информации от входа до выхода ≤ 30нс.

Время цикла “запись-считывание” 100нс.

Время задержки распространения информационного сигнала на выходе относительно сигнала строба ≤45нс.

Время задержки распространения информационного сигнала на выходе относительно сигнала “разрешения выхода” от10 до 30нс.

Время сохранения информационного сигнала на входе относительно сигнала строба ≥25нс.

Длительность импульса сигнала строба ≥15нс.

Минимальная длительность тактовых импульсов 15нс.

Входная емкость 12пФ.

Потребляемая мощность ≤ 800мВт.

Напряжение питания +5В.

Минимальная наработка 50000ч.

Срок сохраняемости 12 лет.

5.Расчет надежности блока динамического ОЗУ.

Для повышения надежности ЗУ применяется код Хемминга, исправляющий одноразрядную ошибку в слове ЗУ.

В качестве показателей надежности широко применяют вероятность безотказной работы Р(t) за время t и среднюю наработку до отказа Тср.

Вычисляется коэффициент КDL, учитывающий эквивалентную дозу отказов различных типов в зависимости от разрядности исправляемой ошибки L. При отказах БИС ЗУ можно выделить следующие основные типы отказов: отказ всей микросхемы (доля таких отказов а1), отказ строки (доля таких отказов а2), отказ столбца (доля таких отказов а3), отказ ЭП (доля таких отказов а4)

а1=2 а2=14

а3=17 а4=42

если код исправляет одноразрядную ошибку (L=1):

где: КM- коэффициент, учитывающий число разрядов БИС ЗУ (если число разрядов nM =1, то КМ=0, иначе КМ=1); KZ- коэффициент, учитывающий тип ЗУ (для ПЗУ КZ=0.5, а для ОЗУ КZ=1); E- информационная емкость БИС ЗУ (в битах).

Определение вероятности безотказной работы ЗУ Р(t).

Вероятность безотказной работы – это вероятность того, что в пределах заданной наработки, т.е. заданного интервала времени , отказ объекта не возникнет.

где: nO- разрядность слова ЗУ; λМ- интенсивность отказов БИС ЗУ;

NR- число строк в БИС ЗУ в ЗУ; λZ- интенсивность отказов схем обрамления и элементов конструкции ЗУ (например, паек, контактов соединителей, линий связи, печатного монтажа и т.п.)

КР1, КР2- поправочные коэффициенты, используемые для компенсации погрешностей в ЗУ с большим и средним числом БИС ЗУ. КР2- значение коэффициента определяется в зависимости от типа ЗУ и разрядности исправляемой ошибки

( для ОЗУ с L=1 если nM=1 то КР2=1); КР1- значение коэффициента в зависимости от nM (при nM=1 то КР1=1).

Вычисление значения параметра ХL, определяющего

соотношение между интенсивностью отказов элементов ЗУ, охваченных и неохваченых корректирующим кодом:

Определение средней наработки до отказа Тср.

Средняя наработка до отказа, или средняя время безотказной работы- это ожидаемая наработка объекта до первого отказа.

где: bLi- коэффициенты разложения полиномов

для L=1 bL1=1,2533 bL2= -1,0006 bL3=0,6308

6.Расчет потребляемой мощности блоком ОЗУ.

Мщность потребляемая микросхемой ОЗУ К565РУ3Г в режиме хранения информации, оценивается при следующих исходных данных: Ра=0.46Вт, Ро=0.04Вт, mр=128, Тц мин=0.37мкс, Трег=2000мкс -по формуле:

Рхр.рег.Ро+(Ра-Ро)(Тц.мин mр/Трег)=0.04+(0.46-0.04)(1280.37/2000)=0.049 Вт

где: Ра- мощность потребляемая ОЗУ в режиме считывания, записи; Ро-мощность потребляемая ОЗУ в режиме хранения; mр-количество строк в матрице ОЗУ; Тц.мин-минимальное время цикла обращения к модулю ОЗУ; Трег-период регенерации, определяющий максимальный интервал времени между двумя обращениями по каждому адресу для востановления хранимой информации.

Мощность потребляемая микросхемами ОЗУ в блоке в режиме считывания или записи информации оценивается при По=8 и Па=8 по формуле:

Рмп=РаПа+Рхр.рег(По-Па)=0.468+0.049(8-8)=1.84 Вт

где: По- общее число микросхем ОЗУ в блоке; Па- число микросхем ОЗУ, находящихся в активном режиме.

Мощность потребляемая микросхемами ОЗУ в блоке в режиме хранения информации определяется как:

Рмп.рег=Рхр.регПо=0.0498=0.39 Вт.

Мощность потребляемая блоком ОЗУ в режиме хранения информации:

Рб.рег=Рмп.рег+Ру=0.39+0.01654+0.8=1.26 Вт.

где: Ру- мощность потребляемая схемами управления.

Мощность потребляемая блоком ОЗУ в режиме записи, считывания информации:

Рб=Рмп+Ру=1.84+0.01654+0.8=2.7 Вт.

Чтобы получить электрическую , принципиальную и временные диаграммы процессов обратитесь по адресу tipa-iorsh@mtu-net.ru